El MOS Technology 6502 (que se pronuncia típicamente "sixty-five-oh-two" o "six-five-oh-two") [3] es un microprocesador de 8 bits que fue diseñado por un pequeño equipo dirigido por Chuck Peddle para MOS Technology . El equipo de diseño había trabajado anteriormente en Motorola en el proyecto Motorola 6800 ; el 6502 es esencialmente una versión simplificada, menos costosa y más rápida de ese diseño.

Cuando se presentó en 1975, el 6502 era el microprocesador más económico del mercado por un margen considerable. Inicialmente se vendió por menos de una sexta parte del costo de los diseños de la competencia de empresas más grandes, como el 6800 o el Intel 8080. Su introducción provocó rápidas disminuciones en los precios en todo el mercado de procesadores. Junto con el Zilog Z80 , desencadenó una serie de proyectos que dieron como resultado la revolución de las computadoras domésticas de principios de la década de 1980.

Las consolas de videojuegos y los ordenadores domésticos de los años 70 hasta principios de los 90, como el Atari 2600 , los ordenadores Atari de 8 bits , Apple II , Nintendo Entertainment System , Commodore 64 , Atari Lynx , BBC Micro y otros, utilizan el 6502 o variaciones del diseño básico. Poco después de la introducción del 6502, MOS Technology fue adquirida directamente por Commodore International , que continuó vendiendo el microprocesador y las licencias a otros fabricantes. En los primeros días del 6502, fue adquirido por Rockwell y Synertek , y más tarde se licenció a otras empresas.

En 1981, el Centro de Diseño Occidental comenzó a desarrollar una versión CMOS , la 65C02 . Esta sigue utilizándose ampliamente en sistemas integrados , con volúmenes de producción estimados en cientos de millones. [4]

El 6502 fue diseñado por muchos de los mismos ingenieros que habían diseñado la familia de microprocesadores Motorola 6800. [5] Motorola inició el proyecto del microprocesador 6800 en 1971 con Tom Bennett como arquitecto principal. Los ingenieros de Motorola podían ejecutar simulaciones analógicas y digitales en una computadora central IBM 370-165 . [6] El diseño del chip comenzó a fines de 1972, los primeros chips 6800 se fabricaron en febrero de 1974 y la familia completa se lanzó oficialmente en noviembre de 1974. [7] [8]

John Buchanan fue el diseñador del chip 6800 [9] [10] y Rod Orgill, quien más tarde hizo el 6501, ayudó a Buchanan con los análisis de circuitos y el diseño del chip. [11] Bill Mensch se unió a Motorola en junio de 1971 después de graduarse de la Universidad de Arizona (a la edad de 26 años). [12] Su primera tarea fue ayudar a definir los circuitos integrados periféricos para la familia 6800 y más tarde fue el diseñador principal del adaptador de interfaz periférica (PIA) 6820. [13] Bennett contrató a Chuck Peddle en 1973 para realizar trabajos de soporte arquitectónico en los productos de la familia 6800 que ya estaban en progreso. [14] Contribuyó en muchas áreas, incluido el diseño de la ACIA (interfaz serial) 6850. [15]

Los clientes objetivo de Motorola eran empresas de electrónica establecidas como Hewlett-Packard , Tektronix , TRW y Chrysler . [16] En mayo de 1972, los ingenieros de Motorola comenzaron a visitar a clientes selectos y a compartir los detalles de su sistema de microprocesador de 8 bits propuesto con ROM, RAM, interfaces paralelas y seriales. [17] A principios de 1974, proporcionaron muestras de ingeniería de los chips para que los clientes pudieran crear prototipos de sus diseños. La estrategia de "familia total de productos" de Motorola no se centró en el precio del microprocesador, sino en reducir el costo total de diseño del cliente. Ofrecieron software de desarrollo en una computadora de tiempo compartido, el sistema de depuración "EXORciser", capacitación en el sitio y soporte de ingenieros de aplicaciones de campo. [18] [19] Tanto Intel como Motorola habían anunciado inicialmente un precio de 360 dólares estadounidenses para un solo microprocesador. [20] [21] El precio real para las cantidades de producción fue mucho menor. Motorola ofreció un kit de diseño que contenía el 6800 con seis chips de soporte por 300 dólares estadounidenses . [22]

Peddle, que acompañaba a los vendedores en las visitas a los clientes, se dio cuenta de que los clientes se sentían desanimados por el alto coste de los chips de microprocesador. [23] Al mismo tiempo, estas visitas invariablemente daban como resultado que los ingenieros a los que se presentaba produjeran listas de instrucciones necesarias que eran mucho más pequeñas que "todas esas instrucciones sofisticadas" que se habían incluido en el 6800. [24] Peddle y otros miembros del equipo comenzaron a esbozar el diseño de un microprocesador de tamaño reducido y con características mejoradas. En ese momento, la nueva planta de fabricación de semiconductores de Motorola en Austin, Texas , estaba teniendo dificultades para producir chips MOS, y mediados de 1974 fue el comienzo de una recesión de un año en la industria de los semiconductores. Además, muchos de los empleados de Mesa, Arizona, estaban descontentos con la inminente reubicación en Austin. [25]

La dirección de la división de productos semiconductores de Motorola no mostró ningún interés en la propuesta de Peddle de fabricar un microprocesador de bajo coste. Finalmente, Peddle recibió una carta oficial en la que se le indicaba que dejase de trabajar en el sistema. [26] Peddle respondió a la orden informando a Motorola de que la carta representaba una declaración oficial de "abandono del proyecto" y, como tal, la propiedad intelectual que había desarrollado hasta ese momento era ahora suya. [27] En una entrevista de noviembre de 1975, el presidente de Motorola, Robert Galvin, finalmente estuvo de acuerdo en que el concepto de Peddle era bueno y que la división había perdido una oportunidad: "No elegimos a los líderes adecuados en la división de productos semiconductores". La división se reorganizó y se reemplazó a la dirección. El nuevo vicepresidente del grupo, John Welty, dijo: "La organización de ventas de semiconductores perdió su sensibilidad a las necesidades de los clientes y no podía tomar decisiones rápidas". [28]

Peddle comenzó a buscar fuera de Motorola una fuente de financiación para este nuevo proyecto. En un principio se puso en contacto con el director ejecutivo de Mostek, LJ Sevin , pero éste le denegó su oferta. Sevin admitió más tarde que esto se debía a que temía que Motorola los demandara. [29]

Mientras Peddle visitaba Ford Motor Company en uno de sus viajes de ventas, Bob Johnson, más tarde jefe de la división de automatización de motores de Ford, mencionó que su ex colega John Paivinen se había trasladado a General Instrument y había aprendido por su cuenta el diseño de semiconductores. [30] Paivinen luego formó MOS Technology en Valley Forge, Pensilvania en 1969 con otros dos ejecutivos de General Instrument, Mort Jaffe y Don McLaughlin. Allen-Bradley , un proveedor de componentes electrónicos y controles industriales, adquirió una participación mayoritaria en 1970. [31] La empresa diseñó y fabricó circuitos integrados personalizados para los clientes y había desarrollado una línea de chips para calculadoras. [32]

Después de que los esfuerzos de Mostek fracasaran, Peddle se acercó a Paivinen, quien "lo entendió de inmediato". [33] El 19 de agosto de 1974, Chuck Peddle, Bill Mensch, Rod Orgill, Harry Bawcom, Ray Hirt, Terry Holdt y Wil Mathys dejaron Motorola para unirse a MOS. Mike Janes se unió más tarde. De los diecisiete diseñadores de chips y personas de diseño en el equipo 6800, ocho se fueron. El objetivo del equipo era diseñar y producir un microprocesador de bajo costo para aplicaciones integradas y apuntar a una base de clientes lo más amplia posible. Esto sería posible solo si el microprocesador fuera de bajo costo, y el equipo estableció el precio objetivo para las compras por volumen en $ 5. [ 34] Mensch declaró más tarde que el objetivo no era el precio del procesador en sí, sino crear un conjunto de chips que pudieran venderse a $ 20 para competir con el recientemente presentado Intel 4040 que se vendía por $ 29 en un chipset completo similar. [35]

Los chips se producen imprimiendo múltiples copias del diseño del chip en la superficie de una oblea , un disco delgado de silicio de alta pureza. Se pueden imprimir chips más pequeños en mayor cantidad en la misma oblea, lo que reduce su precio relativo. Además, las obleas siempre incluyen una cierta cantidad de pequeños defectos físicos que se encuentran dispersos por toda la superficie. Cualquier chip impreso en esa ubicación fallará y deberá desecharse. Los chips más pequeños significan que es menos probable que se imprima una sola copia en un defecto. Por ambas razones, el costo del producto final depende en gran medida del tamaño del diseño del chip. [36]

Los chips 6800 originales estaban pensados para tener 180 por 180 milésimas de pulgada (4,6 mm × 4,6 mm), pero el diseño se completó en 212 por 212 milésimas de pulgada (5,4 mm × 5,4 mm), o un área de29,0 mm 2 . [37] Para el nuevo diseño, el objetivo de costo exigía un tamaño de 153 por 168 milésimas de pulgada (3,9 mm × 4,3 mm), o un área de16,6 mm 2 . [38] Se necesitarían varias técnicas nuevas para alcanzar este objetivo.

Dos avances significativos llegaron al mercado justo cuando se estaba diseñando el 6502, lo que supuso una reducción significativa de los costes. El primero fue el paso al NMOS de carga por agotamiento . El 6800 utilizaba un proceso NMOS temprano, el modo de mejora, que requería tres voltajes de suministro. Una de las características principales del 6800 era un duplicador de voltaje integrado que permitía utilizar una única fuente de alimentación de +5 V para +5, −5 y +12 V internamente, a diferencia de otros chips de la época, como el Intel 8080 , que requerían tres pines de alimentación independientes. [39] Aunque esta característica reducía la complejidad de la fuente de alimentación y el diseño de los pines, seguía requiriendo una línea de alimentación independiente para las distintas puertas del chip, lo que aumentaba la complejidad y el tamaño. Al pasar al nuevo diseño de carga por agotamiento, todo lo que se necesitaba era una única fuente de alimentación de +5 V, lo que eliminaba toda esta complejidad. [40]

Otra ventaja era que los diseños de carga de agotamiento consumían menos energía durante la conmutación, por lo que funcionaban a menor temperatura y permitían velocidades de funcionamiento más altas. Otra consecuencia práctica es que la señal de reloj de las CPU anteriores tenía que ser lo suficientemente fuerte como para sobrevivir a toda la disipación a medida que viajaba por los circuitos, lo que casi siempre requería un chip externo independiente que pudiera proporcionar una señal potente. Con los requisitos de energía reducidos del diseño de carga de agotamiento, el reloj podía trasladarse al chip, lo que simplificaba el diseño general de la computadora. Estos cambios redujeron en gran medida la complejidad y el costo de implementar un sistema completo. [40]

Un cambio más amplio que se produjo en la industria fue la introducción del enmascaramiento por proyección . Anteriormente, los chips se modelaban sobre la superficie de la oblea colocando una máscara sobre la superficie de la oblea y luego iluminándola con una luz brillante. Las máscaras a menudo recogían pequeños trozos de suciedad o fotorresistencia al despegarse del chip, lo que causaba fallas en esas ubicaciones en cualquier enmascaramiento posterior. Con diseños complejos como las CPU, se utilizaban 5 o 6 pasos de enmascaramiento de este tipo, y la probabilidad de que al menos uno de estos pasos introdujera una falla era muy alta. En la mayoría de los casos, el 90% de estos diseños tenían fallas, lo que resultaba en un rendimiento del 10%. El precio de los ejemplos funcionales tenía que cubrir el costo de producción del 90% que se desechaba. [41]

En 1973, Perkin-Elmer introdujo el sistema Micralign , que proyectaba una imagen de la máscara sobre la oblea en lugar de requerir contacto directo. Las máscaras ya no acumulaban suciedad de las obleas y duraban alrededor de 100.000 usos en lugar de 10. Esto eliminó los fallos paso a paso y las altas tasas de defectos que se observaban anteriormente en los diseños complejos. El rendimiento de las CPU aumentó inmediatamente del 10% al 60 o 70%. Esto significó que el precio de la CPU se redujo aproximadamente en la misma cantidad y el microprocesador se convirtió de repente en un dispositivo de consumo. [41]

Las líneas de fabricación existentes de MOS Technology se basaban en la antigua tecnología PMOS ; aún no habían comenzado a trabajar con NMOS cuando llegó el equipo. Paivinen prometió tener una línea NMOS en funcionamiento a tiempo para comenzar la producción de la nueva CPU. Cumplió su promesa: la nueva línea estuvo lista en junio de 1975. [42]

Chuck Peddle, Rod Orgill y Wil Mathys diseñaron la arquitectura inicial de los nuevos procesadores. Un artículo de septiembre de 1975 en la revista EDN ofrece este resumen del diseño: [43]

La familia MOS Technology 650X representa un intento consciente de ocho ex empleados de Motorola que trabajaron en el desarrollo del sistema 6800 de crear una pieza que reemplazara y superara al 6800, pero que se vendiera a un precio inferior. Con la ventaja de la retrospección obtenida del proyecto 6800, el equipo de MOS Technology encabezado por Chuck Peddle realizó los siguientes cambios arquitectónicos en la CPU de Motorola...

El cambio principal en términos de tamaño del chip fue la eliminación de los controladores triestado de las salidas del bus de direcciones. Un bus de tres estados tiene estados para "1", "0" y "alta impedancia". El último estado se utiliza para permitir que otros dispositivos accedan al bus, y se utiliza normalmente para multiprocesamiento , o más comúnmente en estas funciones, para acceso directo a memoria (DMA). Si bien es útil, esta característica es muy costosa en términos de circuitos en chip. El 6502 simplemente eliminó esta característica, de acuerdo con su diseño como un controlador económico que se utiliza para tareas específicas y se comunica con dispositivos simples . Peddle sugirió que cualquiera que realmente requiriera este estilo de acceso podría implementarlo con un solo 74158. [44] [a]

La siguiente gran diferencia fue la simplificación de los registros. Para empezar, se eliminó uno de los dos acumuladores . Los registros de uso general, como los acumuladores, deben ser accedidos por muchas partes del decodificador de instrucciones y, por lo tanto, requieren una cantidad significativa de cableado para mover datos hacia y desde su almacenamiento. Dos acumuladores facilitan muchas tareas de codificación, pero le cuestan una complejidad significativa al diseño del chip en sí. [43] Se lograron ahorros adicionales al reducir el registro de pila de 16 a 8 bits, lo que significa que la pila solo podía tener 256 bytes de longitud, lo que era suficiente para su función prevista como microcontrolador. [43] [ verificación fallida ]

El registro de índice IX de 16 bits se dividió en dos, convirtiéndose en X e Y. Más importante aún, el estilo de acceso cambió. En el 6800, IX contenía una dirección de 16 bits que se compensaba con un número de 8 bits almacenado con la instrucción y se sumaban. En el 6502 (y en la mayoría de los demás diseños contemporáneos), la dirección base de 16 bits se almacenaba en la instrucción y se le añadían los 8 bits X o Y. [44]

Finalmente, se simplificó el conjunto de instrucciones, liberando espacio en el decodificador y la lógica de control. De las 72 instrucciones originales del 6800, se implementaron 56. Entre las que se eliminaron se encontraban instrucciones que operaban entre los dos acumuladores del 6800 y varias instrucciones de bifurcación inspiradas en el PDP-11 . [44]

El diseño de alto nivel del chip tuvo que convertirse en dibujos de transistores e interconexiones. En MOS Technology, el "diseño" fue un proceso muy manual realizado con lápices de colores y papel vitela . El diseño consistía en miles de formas poligonales en seis dibujos diferentes; uno para cada capa del proceso de fabricación. Dados los límites de tamaño, el diseño completo del chip tuvo que ser considerado constantemente. Mensch y Paivinen trabajaron en el decodificador de instrucciones [46] mientras que Mensch, Peddle y Orgill trabajaron en la ALU y los registros. Un avance adicional, desarrollado en una fiesta, fue una forma de compartir parte del cableado interno para permitir que la ALU se redujera en tamaño. [47]

A pesar de sus mejores esfuerzos, el diseño final terminó siendo 5 milésimas de ancho. [48] Los primeros 6502 chips tenían 168 por 183 milésimas de ancho (4,3 mm × 4,6 mm), para un área de19,8 mm 2 . La versión original del procesador no tenía capacidad de rotación a la derecha (ROR), por lo que la instrucción se omitió de la documentación original. La siguiente iteración del diseño redujo el tamaño del chip y agregó la capacidad de rotación a la derecha, y la ROR se incluyó en la documentación revisada. [49] [b]

MOS introduciría dos microprocesadores basados en el mismo diseño subyacente: el 6501 se conectaría al mismo zócalo que el Motorola 6800, mientras que el 6502 reorganizó el pinout para admitir un oscilador de reloj en chip. Ambos funcionarían con otros chips de soporte diseñados para el 6800. No ejecutarían el software del 6800 porque tenían un conjunto de instrucciones diferente, registros diferentes y, en su mayoría, modos de direccionamiento diferentes. [3] Rod Orgill fue responsable del diseño del 6501; había ayudado a John Buchanan en Motorola en el 6800. Bill Mensch hizo el 6502; fue el diseñador del adaptador de interfaz periférica (PIA) 6820 en Motorola. Harry Bawcom, Mike Janes y Sydney-Anne Holt ayudaron con el diseño.

La presentación de los microprocesadores de MOS Technology fue diferente del tradicional lanzamiento de un producto que duraba meses. La primera tirada de un nuevo circuito integrado se utiliza normalmente para pruebas internas y se comparte con clientes selectos como "muestras de ingeniería". Estos chips suelen tener uno o dos defectos de diseño menores que se corregirán antes de que comience la producción. El objetivo de Chuck Peddle era vender la primera tirada de chips 6501 y 6502 a los asistentes a la feria comercial WESCON en San Francisco a partir del 16 de septiembre de 1975. Peddle fue un portavoz muy eficaz y los microprocesadores de MOS Technology recibieron una amplia cobertura en la prensa especializada. Una de las primeras fue una historia de página completa sobre los microprocesadores MCS6501 y MCS6502 en la edición del 24 de julio de 1975 de la revista Electronics . [53] También aparecieron artículos en EE Times (24 de agosto de 1975), [54] EDN (20 de septiembre de 1975), Electronic News (3 de noviembre de 1975), Byte (noviembre de 1975) [55] y Microcomputer Digest (noviembre de 1975). [56] Los anuncios del 6501 aparecieron en varias publicaciones la primera semana de agosto de 1975. El 6501 estaría a la venta en Wescon por 20 dólares cada uno. [57] En septiembre de 1975, los anuncios incluían tanto el microprocesador 6501 como el 6502. El 6502 costaría sólo 25 dólares (equivalente a 142 dólares en 2023). [58]

Cuando MOS Technology llegó a Wescon, se encontró con que a los expositores no se les permitía vender nada en el piso de exhibición. Alquilaron la Suite MacArthur en el Hotel St. Francis y dirigieron a los clientes allí para comprar los procesadores. En la suite, los procesadores se almacenaban en grandes frascos para dar a entender que los chips estaban en producción y disponibles. Los clientes no sabían que la mitad inferior de cada frasco contenía chips no funcionales. [59] Los chips costaban $ 20 y $ 25, mientras que el paquete de documentación costaba $ 10 adicionales . Se animó a los usuarios a hacer fotocopias de los documentos, una forma económica para MOS Technology de distribuir información del producto. Las hojas de datos preliminares enumeraban solo 55 instrucciones excluyendo la instrucción Rotate Right (ROR) que no era compatible con estos primeros chips. Las revisiones en Byte y EDN señalaron la falta de la instrucción ROR. La siguiente revisión del diseño solucionó este problema y la hoja de datos de mayo de 1976 enumeraba 56 instrucciones. Peddle quería que todos los ingenieros y aficionados interesados tuvieran acceso a los chips y a la documentación, mientras que otras empresas de semiconductores sólo querían tratar con clientes "serios". Por ejemplo, Signetics estaba presentando el microprocesador 2650 y sus anuncios pedían a los lectores que escribieran para solicitar información en papel membretado de la empresa. [60]

La introducción del 6501/6502 en forma impresa y en Wescon fue un enorme éxito. La desventaja fue que la amplia cobertura de prensa atrajo la atención de Motorola. En octubre de 1975, Motorola redujo el precio de un solo microprocesador 6800 de $175 a $69 . El kit de diseño del sistema de $300 se redujo a $150 y ahora venía con una placa de circuito impreso. [61] El 3 de noviembre de 1975, Motorola solicitó una orden judicial en la Corte Federal para impedir que MOS Technology fabricara y vendiera productos de microprocesadores. También presentaron una demanda alegando violación de patentes y apropiación indebida de secretos comerciales. Motorola afirmó que siete ex empleados se unieron a MOS Technology para crear los productos de microprocesadores de esa empresa. [62]

Motorola era una empresa multimillonaria con un caso plausible y abogados caros. El 30 de octubre de 1974, Motorola había presentado numerosas solicitudes de patentes sobre la familia de microprocesadores y se le concedieron veinticinco patentes. La primera fue en junio de 1976 y la segunda fue a Bill Mensch el 6 de julio de 1976, para el diseño del chip 6820 PIA. Estas patentes cubrían el bus 6800 y cómo los chips periféricos interactuaban con el microprocesador. [63] Motorola comenzó a fabricar transistores en 1950 y tenía una cartera de patentes de semiconductores. Allen-Bradley decidió no luchar en este caso y vendió su participación en MOS Technology a los fundadores. Cuatro de los antiguos ingenieros de Motorola fueron nombrados en la demanda: Chuck Peddle, Will Mathys, Bill Mensch y Rod Orgill. Todos fueron nombrados inventores en las solicitudes de patente 6800. Durante el proceso de descubrimiento, Motorola descubrió que un ingeniero, Mike Janes, había ignorado las instrucciones de Peddle y había llevado sus documentos de diseño del 6800 a MOS Technology. [64] En marzo de 1976, la ahora independiente MOS Technology se estaba quedando sin dinero y tuvo que resolver el caso. Acordaron abandonar el procesador 6501, pagarle a Motorola 200.000 dólares y devolver los documentos que Motorola sostenía que eran confidenciales. Ambas compañías acordaron conceder licencias cruzadas sobre patentes de microprocesadores. [65] En mayo de ese mismo año, Motorola redujo el precio de un solo microprocesador 6800 a 35 dólares . En noviembre, Commodore había adquirido MOS Technology. [66] [67]

Con los problemas legales a sus espaldas, MOS todavía tenía el problema de conseguir que los desarrolladores probaran su procesador, lo que llevó a Chuck Peddle a diseñar el ordenador de placa única MDT-650 ("terminal de desarrollo de microordenadores") . Otro grupo dentro de la empresa diseñó el KIM-1 , que se vendió semicompleto y podía convertirse en un sistema utilizable con la adición de un terminal de ordenador de terceros y una unidad de casete compacta . Si bien se vendió bien en su mercado objetivo, la empresa descubrió que el KIM-1 también se vendió bien entre los aficionados y los manitas. El sistema de control, formación y desarrollo Rockwell AIM-65 relacionado también tuvo buenos resultados. El software del AIM 65 se basaba en el del MDT. Otro producto más o menos similar fue el Synertek SYM-1 .

Uno de los primeros usos "públicos" del diseño fue el microordenador Apple I , introducido en 1976. El 6502 se utilizó a continuación en el Commodore PET y el Apple II , [68] ambos lanzados en 1977. Más tarde se utilizó en los ordenadores Atari de 8 bits , Acorn Atom , BBC Micro , [68] VIC-20 y otros diseños tanto para ordenadores domésticos como empresariales, como los ordenadores Ohio Scientific y Oric . El 6510 , un sucesor directo del 6502 con un puerto de E/S digital y un bus de direcciones triestado , fue la CPU utilizada en el ordenador doméstico más vendido [69] [70] Commodore 64 .

Otro uso importante de la familia 6500 fue en los videojuegos. El primero en hacer uso del diseño del procesador fue el Atari VCS de 1977, posteriormente rebautizado como Atari 2600. El VCS utilizó una variante del 6502 llamada 6507 , que tenía menos pines, por lo que solo podía direccionar 8 KB de memoria. Se venderían millones de consolas Atari, cada una con un procesador MOS. Otro uso significativo fue el de Nintendo Entertainment System y Famicom. El 6502 utilizado en la NES fue una segunda versión de origen de Ricoh , un sistema parcial en un chip , que carecía del modo decimal codificado en binario pero agregó 22 registros mapeados en memoria y hardware en la matriz para generación de sonido, lectura de joystick y DMA de lista de sprites . Llamado 2A03 en las consolas NTSC y 2A07 en las consolas PAL (la diferencia es el divisor de frecuencia de reloj y una tabla de búsqueda para las frecuencias de muestreo de audio), este procesador fue producido exclusivamente para Nintendo .

El 6502 o variantes se utilizaron en todas las unidades de disquete de Commodore para todas sus computadoras de 8 bits, desde la línea PET hasta el Commodore 128D, incluido el Commodore 64. Las unidades PET de 8 pulgadas tenían dos procesadores 6502. Atari utilizó el mismo 6507 utilizado en el Atari VCS para sus unidades de disco 810 y 1050 utilizadas para toda su línea de computadoras de 8 bits, desde el 400/800 hasta el XEGS.

En la década de 1980, una popular revista de electrónica, Elektor/Elektuur, utilizó el procesador en su placa de desarrollo de microprocesadores Junior Computer .

El sucesor CMOS del 6502, el WDC 65C02 , también se utilizó en ordenadores domésticos y consolas de videojuegos. Apple lo utilizó en la línea Apple II a partir del Apple IIc y variantes posteriores del Apple IIe y también ofreció un kit para actualizar los sistemas IIe más antiguos con el nuevo procesador. [71] El chip Hudson Soft HuC6280 utilizado en el TurboGrafx-16 se basaba en un núcleo 65C02. El Atari Lynx utilizó un chip personalizado llamado "Mikey" [72] diseñado por Epyx que incluía una celda con licencia VLSI VL65NC02. La variante G65SC12 de GTE Microcircuits (rebautizada como California Micro Devices) se utilizó en el BBC Master . Algunos modelos del BBC Master también incluían un coprocesador G65SC102 adicional.

El 6502 es un procesador little-endian de 8 bits con un bus de direcciones de 16 bits . Las versiones originales se fabricaron utilizando un chip de tecnología de proceso de 8 µm [73] con un tamaño de chip de 3,9 mm × 4,3 mm (153 por 168 milésimas de pulgada), para un área total de16,6 mm2 . [ 38]

La lógica interna funciona a la misma velocidad que la frecuencia de reloj externa. Presentaba una secuencia simple: en cada ciclo, el procesador extrae un byte de la memoria y procesa otro. Esto significa que cualquier instrucción individual puede tardar tan solo dos ciclos en completarse, dependiendo de la cantidad de operandos que utilice esa instrucción. A modo de comparación, el Zilog Z80 requería dos ciclos para extraer memoria y el tiempo mínimo de instrucción era de cuatro ciclos. Por lo tanto, a pesar de las velocidades de reloj más bajas en comparación con los diseños de la competencia, generalmente en el entorno de 1 a 2400 bytes, el tiempo de instrucción mínimo era de cuatro ciclos.A 2 MHz , el rendimiento del 6502 era competitivo con las CPU que usaban relojes significativamente más rápidos. Esto se debe en parte a una máquina de estados simple implementada mediante lógica combinacional (sin reloj) en mayor medida que en muchos otros diseños; el reloj de dos fases (que proporciona dos sincronizaciones por ciclo) podía controlar así directamente el ciclo de la máquina.

Este diseño también dio lugar a una nota de diseño útil del 6502 y del 6800 anterior. Como el chip solo accedía a la memoria durante una determinada parte del ciclo de reloj, y esta duración se indicaba mediante el pin de salida de reloj φ2-low, otros chips de un sistema podían acceder a la memoria durante esos momentos en los que el 6502 estaba fuera del bus. Esto se conocía a veces como "acceso oculto". Esta técnica era muy utilizada por los sistemas informáticos; utilizaban una memoria capaz de acceder a 2 MHz y luego ejecutaban la CPU a 1 MHz. Esto garantizaba que la CPU y el hardware de vídeo pudieran intercalar sus accesos, con un rendimiento total que coincidiera con el del dispositivo de memoria. Como este acceso se realizaba cada dos ciclos, no era necesario indicar a la CPU que evitara utilizar el bus, lo que hacía que este tipo de acceso fuera fácil de implementar sin ninguna lógica de bus. [74] Cuando memorias más rápidas estuvieron disponibles en la década de 1980, las máquinas más nuevas podían usar esta misma técnica mientras funcionaban a velocidades de reloj más altas; el BBC Micro usó una RAM más nueva que le permitió a su CPU funcionar a 2 MHz mientras seguía usando las mismas técnicas de uso compartido de bus.

Al igual que la mayoría de las CPU simples de la época, el chip dinámico NMOS 6502 no se secuencia mediante microcódigo, sino que se decodifica directamente mediante un PLA dedicado . El decodificador ocupaba aproximadamente el 15 % del área del chip. Esto se compara con los diseños posteriores basados en microcódigo, como el Motorola 68000 , donde la ROM de microcódigo y el motor de decodificación representaban aproximadamente un tercio de las puertas del sistema.

Al igual que su precursor, el 6800, el 6502 tiene muy pocos registros . Entre ellos se incluyen [75]

A= registro acumulador de 8 bitsP= registro de estado de 7 bits [76] n= negativov= desbordamientob= ruptura (solo en valores de pila, no en hardware [77] )d= decimali= deshabilitar interrupciónz= ceroc= llevarPC= contador de programa de 16 bitsS= puntero de pila de 8 bitsX= registro de índice de 8 bitsY= registro de índice de 8 bitsEsto se compara con un competidor contemporáneo, el Intel 8080 , que también tiene un acumulador de 8 bits y un contador de programa de 16 bits, pero tiene seis registros de 8 bits de propósito general (que se pueden combinar en tres punteros de 16 bits) y un puntero de pila de 16 bits más grande. [78]

Para compensar un poco la falta de registros, el 6502 incluye un modo de direccionamiento de página cero que utiliza un byte de dirección en la instrucción en lugar de los dos necesarios para direccionar la página completa.64 KB de memoria. Esto proporciona un acceso rápido a la primera256 bytes de RAM mediante el uso de instrucciones más cortas. Por ejemplo, una instrucción para agregar un valor de la memoria al valor del acumulador normalmente sería de tres bytes, uno para la instrucción y dos para la dirección de 16 bits. El uso de la página cero reduce esto a una dirección de 8 bytes, lo que reduce la longitud total de la instrucción a dos bytes y, por lo tanto, mejora el rendimiento de la instrucción.

El espacio de direcciones de la pila está conectado directamente a la página de memoria $01, es decir, al rango de direcciones $0100– $01FF( 256– 511). El acceso del software a la pila se realiza a través de cuatro instrucciones de modo de direccionamiento implícito, cuyas funciones son empujar o sacar (extraer) el acumulador o el registro de estado del procesador. La misma pila también se utiliza para llamadas a subrutinas a través de las instrucciones JSR (saltar a subrutina) y RTS (regresar desde subrutina) y para el manejo de interrupciones .

El chip utiliza los registros de índice y pila de manera efectiva con varios modos de direccionamiento , incluido un modo rápido de "página directa" o "página cero", similar al que se encuentra en el PDP-8 , que accede a las ubicaciones de memoria de las direcciones 0 a 255 con una única dirección de 8 bits (ahorrándose el ciclo normalmente requerido para obtener el byte de orden superior de la dirección); el código para el 6502 usa la página cero de manera muy similar a como el código para otros procesadores usaría registros. En algunas microcomputadoras basadas en el 6502 con un sistema operativo, el sistema operativo usa la mayor parte de la página cero, dejando solo un puñado de ubicaciones para el usuario.

Los modos de direccionamiento también incluyen implícito (instrucciones de 1 byte); absoluto (3 bytes); absoluto indexado (3 bytes); página cero indexada (2 bytes); relativo (2 bytes); acumulador (1); indirecto,x e indirecto,y (2); e inmediato (2). El modo absoluto es un modo de propósito general. Las instrucciones de bifurcación utilizan un desplazamiento de 8 bits con signo en relación con la instrucción después de la bifurcación; por lo tanto, el rango numérico −128..127 se traduce en 128 bytes hacia atrás y 127 bytes hacia adelante desde la instrucción que sigue a la bifurcación (que es 126 bytes hacia atrás y 129 bytes hacia adelante desde el inicio de la instrucción de bifurcación). El modo acumulador opera en el registro acumulador y no necesita ningún dato de operando . El modo inmediato utiliza un operando literal de 8 bits .

Los modos indirectos son útiles para el procesamiento de matrices y otros bucles. Con el modo "(indirect),y" de 5/6 ciclos, el registro Y de 8 bits se agrega a una dirección base de 16 bits leída desde la página cero, que se encuentra a un solo byte después del código de operación. Por lo tanto, el registro Y es un registro de índice en el sentido de que se utiliza para almacenar un índice real (a diferencia del registro X en el 6800, donde se almacenaba directamente una dirección base y al que se podía agregar un desplazamiento inmediato). Incrementar el registro de índice para recorrer la matriz byte a byte solo requiere dos ciclos adicionales. Con el modo "(indirect,x)" menos utilizado, la dirección efectiva para la operación se encuentra en la dirección de la página cero formada al agregar el segundo byte de la instrucción al contenido del registro X. Al usar los modos indexados, la página cero actúa efectivamente como un conjunto de hasta 128 registros de dirección adicionales (aunque muy lentos).

El 6502 es capaz de realizar sumas y restas en binario o decimal codificado en binario . Al colocar la CPU en modo BCD con la SEDinstrucción (establecer indicador D) se realiza una aritmética decimal, en la que $99 + $01se activaría $00 y se activaría el indicador de acarreo (C). En modo binario ( CLDborrar indicador D), la misma operación daría como resultado $9A y se borraría el indicador de acarreo. Aparte del BASIC de Atari , el modo BCD rara vez se utilizó en aplicaciones de computadoras domésticas.

Consulte el artículo ¡Hola mundo! para ver un ejemplo simple pero característico del lenguaje ensamblador 6502 .

Los códigos de operación de la instrucción 6502 ( opcodes ) tienen 8 bits de longitud y tienen la forma general AAABBBCC, donde AAA y CC definen el opcode, y BBB define el modo de direccionamiento. [79] Por ejemplo, la ORAinstrucción realiza un OR bit a bit en los bits del acumulador con otro valor. El opcode de la instrucción tiene la forma 000bbb01, donde bbb puede ser 010 para un valor de modo inmediato (constante), 001 para una dirección fija de página cero, 011 para una dirección absoluta, y así sucesivamente. [79] Este patrón no es universal, ya que hay excepciones, pero permite que los valores del opcode se conviertan fácilmente en mnemotécnicos de ensamblaje para la mayoría de las instrucciones, manejando los casos extremos con código de propósito especial. [79]

De los 256 códigos de operación posibles disponibles utilizando un patrón de 8 bits, el 6502 original utiliza 151 de ellos, organizados en 56 instrucciones con (posiblemente) múltiples modos de direccionamiento . Dependiendo de la instrucción y el modo de direccionamiento, el código de operación puede requerir cero, uno o dos bytes adicionales para los operandos. Por lo tanto, las instrucciones de máquina 6502 varían en longitud de uno a tres bytes. [80] [81] El operando se almacena en el formato little-endian habitual del 6502 .

El 65C816 , el descendiente CMOS de 16 bits del 6502, también admite direccionamiento de 24 bits, lo que da como resultado instrucciones ensambladas con operandos de tres bytes, también dispuestos en formato little-endian.

Los 105 códigos de operación restantes no están definidos. En el diseño original, no se utilizaron instrucciones donde los 4 bits de orden inferior ( nibble ) eran 3, 7, B o F, lo que dejaba espacio para una expansión futura. Del mismo modo, la columna $2x tenía una sola entrada, . Las 25 ranuras vacías restantes se distribuyeron. Algunas de las ranuras vacías se utilizaron en el 65C02 para proporcionar nuevas instrucciones y variaciones de las existentes con nuevos modos de direccionamiento. Las instrucciones $Fx inicialmente se dejaron libres para permitir que los proveedores externos añadieran sus propias instrucciones, pero las versiones posteriores del 65C02 estandarizaron un conjunto de instrucciones de manipulación de bits desarrolladas por Rockwell Semiconductor .LDX #constant

Una instrucción en lenguaje ensamblador 6502 consta de una mnemotecnia de instrucción de tres caracteres seguida de cualquier operando . Las instrucciones que no toman un operando separado sino que apuntan a un solo registro según el modo de direccionamiento combinan el registro de destino en la mnemotecnia de instrucción, por lo que el ensamblador utiliza INXen lugar de para INC Xincrementar el registro X.

El siguiente código fuente en lenguaje ensamblador 6502 corresponde a una subrutina denominada , que copia una cadena de caracteres terminada en cero de una ubicación a otra, convirtiendo caracteres de letras mayúsculas en letras minúsculas. La cadena que se copia es la "fuente" y la cadena en la que se almacena la fuente convertida es el "destino".TOLOWER

La entrada de interrupción no enmascarable (NMI) del procesador es sensible a los flancos , lo que significa que la interrupción se activa por el flanco descendente de la señal en lugar de por su nivel. La implicación de esta característica es que no se admite fácilmente un circuito de interrupción OR cableado . Sin embargo, esto también evita que se produzcan interrupciones NMI anidadas hasta que el hardware vuelva a desactivar la entrada NMI, a menudo bajo el control del controlador de interrupciones NMI .

La activación simultánea de las líneas de interrupción de hardware NMI e IRQ (enmascarables) hace que se ignore IRQ. Sin embargo, si la línea IRQ permanece activada después de la activación de NMI, el procesador responderá inmediatamente a IRQ, ya que IRQ es sensible al nivel . Por lo tanto, se estableció una especie de prioridad de interrupción incorporada en el diseño del 6502.

El indicador B se establece mediante el muestreo periódico de la salida del detector de borde NMI y la entrada IRQ del 6502. Sin embargo, la señal IRQ que se activa a nivel bajo solo se reconoce si el indicador I permite IRQ. Si de esta manera se detecta una solicitud NMI o una IRQ (enmascarable), el indicador B se establece en cero y hace que el procesador ejecute la instrucción BRK a continuación en lugar de ejecutar la siguiente instrucción según el contador de programa. [82] [83]

La instrucción BRK luego coloca el estado del procesador en la pila, con el bit de la bandera B establecido en cero. Al final de su ejecución, la instrucción BRK restablece el valor de la bandera B a uno. Esta es la única forma en que se puede modificar la bandera B. Si una instrucción distinta de la instrucción BRK coloca la bandera B en la pila como parte del estado del procesador [84], la bandera B siempre tiene el valor uno.

Una transición de alto a bajo en el pin de entrada SO activará el bit de estado de desbordamiento del procesador. Esto se puede utilizar para una respuesta rápida al hardware externo. Por ejemplo, un controlador de dispositivo de sondeo de alta velocidad puede sondear el hardware una vez en solo tres ciclos utilizando una instrucción Branch-on-oVerflow-Clear ( BVC) que se ramifica a sí misma hasta que se activa el desbordamiento mediante una transición descendente SO. El Commodore 1541 y otras unidades de disquete Commodore utilizan esta técnica para detectar cuándo el serializador está listo para transferir otro byte de datos del disco. El diseño del hardware y el software del sistema debe garantizar que no se produzca un SO durante el procesamiento aritmético e interrumpa los cálculos.

El 6502 fue la variante más prolífica de la familia de la serie 65xx de MOS Technology .

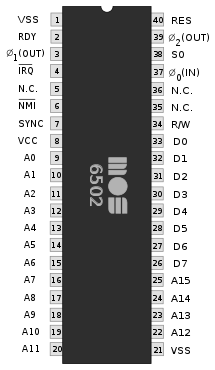

Los modelos 6501 y 6502 tienen encapsulados DIP de 40 pines ; los modelos 6503, 6504, 6505 y 6507 son versiones DIP de 28 pines, lo que reduce el costo del chip y de la placa de circuito. En todas las versiones de 28 pines, se reduce el número de pines al omitir algunos de los pines de dirección de orden superior y varias combinaciones de pines de función, lo que hace que esas funciones no estén disponibles.

Por lo general, los 12 pines que se omiten para reducir el número de pines de 40 a 28 son los tres pines no conectados (NC), uno de los dos pines Vss, uno de los pines de reloj, el pin SYNC, el pin de desbordamiento de conjunto (SO), la interrupción enmascarable o la interrupción no enmascarable (NMI) y las cuatro líneas de dirección más significativas (A12–A15). La omisión de cuatro pines de dirección reduce la direccionabilidad externa a 4 KB (de los 64 KB del 6502), aunque el registro de PC interno y todos los cálculos de dirección efectiva siguen siendo de 16 bits .

El 6507 omite ambos pines de interrupción para incluir la línea de dirección A12, lo que proporciona 8 KB de direccionabilidad externa pero no capacidad de interrupción. El 6507 se utilizó en la popular consola de videojuegos Atari 2600 , cuyo diseño divide el espacio de memoria de 8 KB a la mitad, asignando la mitad inferior a la RAM interna de la consola y los periféricos, y la mitad superior al cartucho de juego, por lo que los cartuchos Atari 2600 tienen un límite de dirección de 4 KB (y el mismo límite de capacidad a menos que el cartucho contenga circuitos de conmutación de bancos ).

Un ordenador popular basado en el 6502, el Commodore 64 , utilizaba una CPU 6502 modificada, la 6510. A diferencia de los 6503–6505 y 6507, el 6510 es un chip de 40 pines que añade hardware interno: un puerto de E/S paralelo de 6 bits asignado a las direcciones 0000 y 0001. El 6508 es otro chip que, al igual que el 6510, añade hardware interno: 256 bytes de SRAM y un puerto de E/S de 8 bits similar a los que presenta el 6510. Aunque estos chips no tienen un número reducido de pines en comparación con el 6502, necesitan nuevos pines para el puerto de E/S paralelo añadido. En este caso, no hay líneas de dirección entre los pines eliminados.

El Western Design Center diseñó y actualmente produce el procesador WDC 65C816 S, un sucesor de 16 bits y núcleo estático del 65C02 . El W65C816S es una variante más nueva del 65C816, que es el núcleo de la computadora Apple IIGS y es la base del procesador Ricoh 5A22 que impulsa el Super Nintendo Entertainment System . El W65C816S incorpora pequeñas mejoras con respecto al 65C816 que hacen que el chip más nuevo no sea un reemplazo exacto compatible con el hardware del anterior. Entre estas mejoras se encontraba la conversión a un núcleo estático, lo que permite detener el reloj en cualquiera de las fases sin que los registros pierdan datos. Disponible a través de distribuidores de productos electrónicos, a partir de marzo de 2020, el W65C816S está clasificado oficialmente para operar a 14 MHz.

El Western Design Center también diseñó y produjo el 65C802 , que era un núcleo 65C816 con un espacio de dirección de 64 kilobytes en un encapsulado compatible con pines 65(C)02. El 65C802 podía ser adaptado a una placa 6502 y funcionaba como un 65C02 al encenderse, operando en "modo emulación". Al igual que con el 65C816, una secuencia de dos instrucciones cambiaría el 65C802 a operación en "modo nativo", exponiendo su acumulador de 16 bits y registros de índice , y otras características del 65C816. El 65C802 no fue ampliamente utilizado y la producción terminó.

El 6502 tenía varios errores y peculiaridades que había que tener en cuenta al programarlo:

JMP (<address>), está parcialmente rota. Si <address> es hexadecimal xxFF (es decir, cualquier palabra que termine en FF ), el procesador no saltará a la dirección almacenada en xxFF y xxFF+1como se esperaba, sino a la definida por xxFF y xx00 (por ejemplo, JMP ($10FF)saltaría a la dirección almacenada en 10FF y 1000, en lugar de la almacenada en 10FF y 1100). Este defecto continuó a lo largo de toda la línea NMOS, pero se corrigió en los derivados CMOS.El primer 6502 se fabricó con tecnología de 8 micrones, funcionaba a un megahercio y tenía una memoria máxima de 64k.

La llegada de cualquier interrupción se refleja en el indicador B, cuya salida (B_OUT) obliga al procesador a ejecutar una instrucción BRK...

B_OUT; BUS DE DATOS INTERNO (DB)

Los ingenieros de Atari lo llaman SALLY, pero [los documentos de soporte lo llaman] "6502 (Modificado)", "6502 Modificado", "6502 Personalizado" o "6502C". [..] Los chips SALLY 6502 nunca están marcados como "6502C" sino que, a excepción del UMC UM6502I, siempre están [marcados] como C014806. [..] [Otros] chips marcados como "6502C" [..] NO son los "6502C" de Atari sino los [6502 estándar] certificados para 4 MHz