El Zilog Z80 es un microprocesador de 8 bits diseñado por Zilog que desempeñó un papel importante en la evolución de la informática temprana. Compatible con el software del Intel 8080 , ofrecía una alternativa convincente debido a su mejor integración y mayor rendimiento. Además de los siete registros y el registro de indicadores del 8080, el Z80 tenía un conjunto de registros alternativos que los duplicaba, dos registros de índice de 16 bits e instrucciones adicionales que incluían manipulación de bits y copia/búsqueda de bloques.

Inicialmente pensado para usarse en sistemas integrados como el 8080, la combinación de compatibilidad, asequibilidad y rendimiento superior del Z80 lo impulsó a una adopción generalizada en sistemas de videojuegos y computadoras hogareñas a fines de la década de 1970 y principios de la de 1980, impulsando la revolución de la computación personal .

El Z80 fue una creación de Federico Faggin , una figura clave detrás de la creación del Intel 8080. Después de dejar Intel en 1974, Faggin cofundó Zilog con Ralph Ungermann . El Z80 fue lanzado en julio de 1976. Con los ingresos del Z80, la compañía construyó sus propias fábricas de chips . [2] Zilog licenció el Z80 a Synertek y Mostek , con sede en EE. UU. , que los había ayudado con la producción inicial, así como a un fabricante de segunda fuente europeo, SGS . El diseño también fue copiado por varios fabricantes japoneses, de Europa del Este y soviéticos. [d] Esto ganó la aceptación del Z80 en el mercado mundial ya que grandes empresas como NEC , Toshiba , Sharp y Hitachi comenzaron a fabricar el dispositivo (o sus propios clones o diseños compatibles con Z80).

El Z80 siguió utilizándose en sistemas integrados durante décadas después de su introducción, con avances constantes. La última incorporación a la familia Z80 es el eZ80 , que se ofrece junto con los chips sucesores. Zilog anunció la discontinuación del Z80 en abril de 2024 después de casi cinco décadas de producción.

En Fairchild Semiconductor , y más tarde en Intel , el físico e ingeniero Federico Faggin había estado trabajando en la tecnología fundamental de fabricación de transistores y semiconductores . También desarrolló la metodología de diseño básica utilizada para memorias y microprocesadores en Intel y dirigió el trabajo en el Intel 4004 , el Intel 8080 y varios otros circuitos integrados. Masatoshi Shima fue el principal diseñador de lógica y a nivel de transistores del 4004 y el 8080 bajo la supervisión de Faggin, mientras que Ralph Ungermann estaba a cargo del diseño de circuitos integrados personalizados . [3]

A principios de 1974, Intel consideraba que sus microprocesadores no eran tanto productos que se pudieran vender por sí solos, sino una forma de vender más de sus productos principales, RAM y ROM estáticas . Una reorganización colocó muchas de las secciones anteriormente independientes bajo la dirección de Les Vadasz, diluyendo aún más el lugar del microprocesador en la empresa. Ese año, la recesión de 1973-1975 alcanzó su punto álgido e Intel despidió a varios empleados. [3] Todo esto provocó que Faggin se pusiera nervioso, e invitó a Ungermann a tomar algo y le preguntó si estaría interesado en iniciar su propia empresa. Ungermann aceptó de inmediato y, como tenía menos cosas que hacer en Intel, se fue en agosto o septiembre, seguido por Faggin, cuyo último día en Intel fue Halloween de 1974. [4] Cuando Shima se enteró, pidió venir también a la nueva empresa, pero al no tener un diseño de producto real ni dinero, le dijeron que esperara. [5]

La compañía recién formada y sin nombre inicialmente comenzó a diseñar un microcontrolador de un solo chip llamado 2001. Se reunieron con Synertek para discutir la fabricación en sus líneas, y cuando Faggin comenzó a entender los costos involucrados, quedó claro que un producto de bajo costo como este no podría competir con un diseño de una compañía con sus propias líneas de producción, como Intel. Entonces comenzaron a considerar un microprocesador más complejo en su lugar, inicialmente conocido como Super 80, con la característica principal siendo su uso de un bus de +5 V [5] en lugar de los más comunes −5, +5 y 12 V utilizados por diseños como el 8080. El nuevo diseño estaba destinado a ser compatible con el 8080, pero agregar muchas de las agradables características del Motorola 6800 , incluidos los registros de índice e interrupciones mejoradas . [6]

Mientras aún se estaba formando, el boletín de noticias del sector Electronic News se enteró de ellos y publicó un artículo sobre la empresa recién formada. Esto atrajo la atención de Exxon Enterprises, el brazo inversor de alta tecnología de Exxon . En ese momento, en medio de la recesión, había muy poco capital de riesgo disponible, con un total de 10 millones de dólares para toda la industria gastados en todo 1975 (equivalentes a 57 millones de dólares en 2023). Alguien de Exxon se puso en contacto con la empresa aún sin nombre [5] y organizó una reunión que finalmente llevó a que proporcionaran una financiación inicial de 500.000 dólares en junio de 1975 (equivalentes a 2,8 millones de dólares en 2023). [7]

En febrero de 1975, cuando se estaba discutiendo la financiación y se tenía que construir un diseño, Shima se unió a la empresa. [6] Shima se puso inmediatamente a producir un diseño de alto nivel, añadiendo varios conceptos propios. En particular, utilizó su experiencia con las minicomputadoras NEC para añadir el concepto de dos conjuntos de registros de procesador para que pudieran responder rápidamente a las interrupciones . [4] [e] Ungerman comenzó el desarrollo de una serie de controladores y chips periféricos relacionados que complementarían el diseño. [8]

Durante este período, Shima se ganó una reputación legendaria por ser capaz de convertir conceptos lógicos en diseño físico en tiempo real; mientras discutía una característica propuesta, a menudo interrumpía y decía cuánto espacio ocuparía eso en el chip y vetaba su adición si era demasiado grande. [9] El primer paso del diseño se completó en abril de 1975. Shima había completado un diseño lógico a principios de mayo. Una segunda versión del diseño lógico se publicó el 7 de agosto y los detalles del bus el 16 de septiembre. La producción en cinta se completó en noviembre y la conversión de la cinta en una máscara de producción requirió dos meses más. [10]

Faggin ya había empezado a buscar un socio de producción. Para entonces, Synertek y Mostek ya habían instalado las líneas de producción en modo de agotamiento que podrían utilizarse para producir el diseño. Tras haber hablado con Synertek previamente, Faggin se puso en contacto con ellos primero. Sin embargo, el presidente de Synertek exigió que se le otorgara a la empresa una licencia de segunda fuente , lo que les permitiría vender el diseño directamente. Faggin pensó que esto significaría que nunca podrían competir incluso si instalaban sus propias líneas, y el acuerdo fracasó. Entonces recurrió a Mostek, que aceptó un plazo de exclusividad mientras Zilog instalaba sus líneas, y finalmente obtuvo el acuerdo de segunda fuente. [11]

Después de considerar muchos nombres para la nueva empresa y de encontrarlos tan poco memorables que no pudieron recordarlos ni siquiera un día después, Faggin y Ungermann estaban barajando ideas basadas en la "lógica integrada" cuando Ungermann dijo "¿qué tal Zilog?" Faggin estuvo de acuerdo de inmediato, afirmando que podían decir que era "la última palabra en lógica integrada". Cuando se reunieron al día siguiente y ambos lo recordaron de inmediato, la empresa tenía su nombre. [12]

Las primeras muestras fueron devueltas desde Mostek el 9 de marzo de 1976. [8] A finales de mes, también habían completado un sistema de desarrollo basado en ensamblador . Algunos de los circuitos integrados de soporte y periféricos del Z80 estaban en desarrollo en ese momento, y muchos de ellos se lanzaron durante el año siguiente. Entre ellos se encontraban el Z80 CTC (contador/temporizador), el Z80 DMA [13] (acceso directo a memoria), el Z80 DART (receptor-transmisor asíncrono dual), el Z80 SIO (controlador de comunicación síncrona) y el Z80 PIO (entrada/salida paralela).

El Z80 se lanzó oficialmente en julio de 1976. [14] Uno de los primeros clientes fue un comprador que, sin que Zilog lo supiera, trabajaba para NEC. En ese momento, las empresas de electrónica japonesas eran bien conocidas por tomar diseños de chips estadounidenses y producirlos sin licencia. El equipo de Zilog se había preocupado por esto, y Faggin había tenido la idea de agregar transistores que se modificarían sutilmente para que funcionaran de manera diferente a lo que sugeriría una inspección visual. Shima agregó seis de estas "trampas" alrededor del diseño. Algún tiempo después, un ingeniero de NEC le dijo a Shima que las trampas habían retrasado sus esfuerzos de copia durante seis meses. [15]

El exitoso lanzamiento permitió a Faggin y Ungermann acercarse a Exxon en busca de financiación para construir su propia fábrica. La empresa aceptó y Zilog construyó una línea de producción muy rápidamente. Esto les permitió captar entre el 60 y el 70% del mercado total de ventas del Z80. [16] Con su propia línea en funcionamiento, Mostek recibió el visto bueno para iniciar las ventas de sus propias versiones, la MK3880, que proporcionaba una segunda fuente de clientes de la que carecía Intel. En ese momento, una segunda fuente se consideraba extremadamente importante ya que una empresa emergente como Zilog podría quebrar y dejar a los clientes potenciales varados. [6] [f]

Faggin diseñó el conjunto de instrucciones para que fuera compatible a nivel binario con el 8080 [17] [18] de modo que la mayor parte del código del 8080, en particular el sistema operativo CP/M y el compilador PL/M de Intel para el 8080 (así como el código generado por el mismo), pudiera ejecutarse sin modificaciones en la nueva CPU Z80. Masatoshi Shima diseñó la mayor parte de la microarquitectura , así como los niveles de compuerta y transistor de la CPU Z80, con la ayuda de un pequeño número de ingenieros y diseñadores gráficos . [19] [20] El director ejecutivo Federico Faggin estuvo muy involucrado en el trabajo de diseño del chip, junto con dos diseñadores gráficos dedicados. Según Faggin, trabajaba 80 horas a la semana para cumplir con el ajustado cronograma que le habían dado los inversores financieros. [2]

El Z80 ofreció muchas mejoras con respecto al 8080: [18]

El Z80 tomó el relevo del 8080 y su descendiente, el 8085 , en el mercado de procesadores [25] y se convirtió en una de las CPU de 8 bits más populares y ampliamente utilizadas. [26] [27] Algunas organizaciones como British Telecom se mantuvieron leales al 8085 para aplicaciones integradas, debido a su familiaridad con él y a su interfaz serial en chip y arquitectura de interrupción. Del mismo modo, Zenith Data Systems emparejó el 8085 con el Intel 8088 de 16 bits en su primer ordenador MS-DOS, el Zenith Z-100 , a pesar de tener experiencia previa con sus productos pioneros Heathkit H89 y Zenith Z-89 basados en Z80 . Sin embargo, se fabricaron otros ordenadores integrando el Z80 con otras CPU: el Radio Shack TRS-80 Modelo 16 con un Motorola 68000 , el DEC Rainbow con un 8088 y el Commodore 128 con un MOS Technology 8502 .

Más tarde, Zilog produjo un Z80 de bajo consumo adecuado para el creciente mercado de ordenadores portátiles de principios de los años 1980. Intel produjo un CMOS 8085 (80C85) utilizado en ordenadores portátiles alimentados por batería, como el portátil diseñado por Kyocera a partir de abril de 1983, también vendido por Tandy (como TRS-80 Model 100 ), Olivetti y NEC. En los años siguientes, sin embargo, las versiones CMOS del Z80 (tanto de Zilog como de fabricantes japoneses) dominarían también este mercado, en productos como el Amstrad NC100 , el Cambridge Z88 y el propio WP-2 de Tandy.

Tal vez una de las claves del éxito inicial del Z80 fue la actualización de la memoria DRAM incorporada, al menos en mercados como CP/M y otros ordenadores domésticos y de oficina (la mayoría de los sistemas integrados Z80 utilizan RAM estática que no necesita actualización). También puede haber sido su sistema minimalista de interrupción de dos niveles o, por el contrario, su sistema general de interrupción en cadena de varios niveles útil para dar servicio a varios chips de E/S del Z80. Estas características permitieron construir sistemas con menos hardware de soporte y diseños de placas de circuitos más simples.

Sin embargo, otros afirman que su popularidad se debió a los registros duplicados que permitían cambios de contexto rápidos o un procesamiento más eficiente de cosas como matemáticas de punto flotante en comparación con las CPU de 8 bits con menos registros. (El Z80 puede mantener varios de esos números internamente, utilizando HL'HL, DE'DE y BC'BC como registros de 32 bits, evitando tener que acceder a ellos desde una RAM más lenta durante el cálculo). [28]

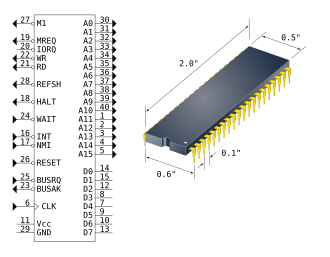

Para el diseño NMOS original , el límite superior de frecuencia de reloj especificado aumentó sucesivamente desde los 2,5 MHz introductorios , pasando por los conocidos 4 MHz (Z80A), hasta los 6 MHz (Z80B) y los 8 MHz (Z80H). [29] [30] La versión NMOS se ha producido como una parte de 10 MHz desde finales de los años 1980. Las versiones CMOS se desarrollaron con límites superiores de frecuencia especificados que iban desde los 4 MHz hasta los 20 MHz para la versión que se vende hoy en día. Las versiones CMOS permitían un modo de espera de bajo consumo con el estado interno retenido, sin tener un límite de frecuencia inferior . [j] Los derivados totalmente compatibles HD64180 / Z180 [31] [32] y eZ80 están especificados actualmente para hasta 33 MHz y 50 MHz, respectivamente.

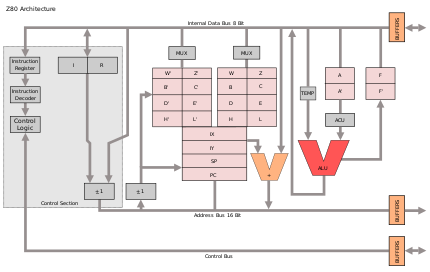

El modelo de programación y el conjunto de registros del Z80 son bastante convencionales, basados en última instancia en la estructura de registros del Datapoint 2200. El Z80 fue diseñado como una extensión del Intel 8080, creado por los mismos ingenieros, que a su vez era una extensión del 8008. El 8008 era básicamente una implementación PMOS de la CPU basada en TTL del Datapoint 2200. [k]

El diseño 2200 permitió que los registros de 8 bits H y L (alto y bajo) se emparejaran en un registro de dirección de 16 bits HL. [l] En el 8080, este emparejamiento también se agregó a los pares BC y DE, mientras que HL se generalizó para permitir su uso como un acumulador de 16 bits, no solo como un registro de dirección. El 8080 también introdujo datos inmediatos de 16 bits para cargas BC, DE, HL y SP. Además, ahora era posible la copia directa de 16 bits entre HL y la memoria, utilizando una dirección directa.

El Z80 ortogonalizó esto aún más al hacer que todos los pares de registros de 16 bits, incluidos IX e IY, sean de propósito más general, además de permitir la copia de 16 bits directamente hacia y desde la memoria para todos estos pares. Los registros IX e IY de 16 bits en el Z80 están pensados principalmente como registros de dirección base, donde una instrucción particular proporciona un desplazamiento constante que se suma a los valores anteriores, pero también se pueden usar como acumuladores de 16 bits, entre otras cosas. Una limitación es que todas las referencias de operandos que involucran IX o IY requieren un byte de prefijo de instrucción adicional, agregando al menos cuatro ciclos de reloj sobre el tiempo de una instrucción que usa HL en su lugar; esto a veces hace que usar IX o IY sea menos eficiente que un método que usa solo los registros del modelo 8080. El Z80 también introdujo un nuevo indicador de desbordamiento con signo y complementó la aritmética bastante simple de 16 bits del 8080 con instrucciones dedicadas para aritmética con signo de 16 bits.

Los registros compatibles con 8080 AF, BC, DE, HL están duplicados como un archivo de registro separado en el Z80, [34] donde el procesador puede cambiar rápidamente (cuatro estados t, el menor tiempo de ejecución posible para cualquier instrucción Z80) de un banco al otro; [35] una característica útil para acelerar las respuestas a interrupciones de alta prioridad de un solo nivel. Una característica similar estaba presente en el 2200, pero nunca se implementó en Intel. El conjunto de registros dual es muy útil en el rol integrado, ya que mejora el rendimiento del manejo de interrupciones, pero encontró un uso generalizado en el rol de computadora personal como un conjunto adicional de registros generales para código complejo como aritmética de punto flotante o juegos de computadora domésticos.

El archivo de registro duplicado se suele denominar "conjunto de registros alternativos" (algunos lo denominan "archivo de registros preparados", ya que el carácter de apóstrofo se utiliza para indicarlos en el código fuente del ensamblador y en la documentación de Zilog). Esto pone de relieve que solo se puede acceder a un conjunto en cualquier momento. Sin embargo, el acumulador A de 8 bits con su registro de bandera F se bifurca de los pares de registros de "propósito general" HL, DE y BC. Esto se logra con dos instrucciones independientes que se utilizan para intercambiar sus accesibilidades: EX AF,AF'intercambia solo el par de registros AF con AF', mientras que la EXXinstrucción intercambia los tres pares de registros de propósito general HL, DE y BC con sus alternativos HL', DE' y BC'. Por lo tanto, el acumulador A puede interactuar de forma independiente con cualquiera de los registros de 8 bits de propósito general en el archivo de registros alternativos (o preparados) o, si HL' contiene un puntero a la memoria, algún byte allí (DE' y BC' también pueden transferir datos de 8 bits entre la memoria y el acumulador A).

Esto puede llegar a ser confuso para los programadores porque después de ejecutar EX AF,AF'o EXXlo que antes eran los registros alternativos (primarios) ahora son los registros principales, y viceversa. La única forma que tiene el programador de saber qué conjunto(s) están en contexto (mientras "juega a la computadora" mientras examina el texto fuente del ensamblador, o peor, examina el código con un depurador) es rastrear dónde se realiza cada intercambio de registro en cada punto del programa. Obviamente, si se realizan muchos saltos y llamadas dentro de estos segmentos de código, puede volverse rápidamente difícil saber qué archivo de registro está en contexto a menos que se comente cuidadosamente. Por lo tanto, es aconsejable que las instrucciones de intercambio se utilicen directamente y en segmentos de código discretos cortos. El conjunto de instrucciones Zilog Z280 incluye JAFinstrucciones JARque saltan a una dirección de destino si los registros alternativos están en contexto (reconociendo así oficialmente esta complicación de programación).

Al igual que en el 8080, los registros de 8 bits suelen emparejarse para proporcionar versiones de 16 bits. Los registros compatibles con el 8080 [36] son:

AF: El acumulador de 8 bits (A) y los bits de bandera (F) llevan, cero, menos, paridad/desbordamiento, medio acarreo (usado para BCD ) y una bandera de suma/resta (generalmente llamada N) también para BCDBC: registro de datos/dirección de 16 bits o dos registros de 8 bitsDE: registro de datos/dirección de 16 bits o dos registros de 8 bitsHL: registro acumulador/de dirección de 16 bits o dos registros de 8 bitsSP: puntero de pila , 16 bitsPC: contador de programa, 16 bitsLos nuevos registros introducidos con el Z80 son:

IX:Índice de 16 bits o registro base para desplazamientos inmediatos de 8 bitsIY:Índice de 16 bits o registro base para desplazamientos inmediatos de 8 bitsI: registro base del vector de interrupción, 8 bitsR:Contador de actualización de DRAM, 8 bits ( msb no cuenta)AF': acumulador alternativo (o de sombra) y banderas ( activadas y desactivadas con EX AF, AF' )BC', DE'y HL': registros alternativos (o de sombra) ( activados y desactivados con EXX )El registro de actualización , R, se incrementa cada vez que la CPU obtiene un código de operación (o un prefijo de código de operación, que se ejecuta internamente como una instrucción de 1 byte) y no tiene una relación simple con la ejecución del programa. Esto se ha utilizado a veces para generar números pseudoaleatorios en juegos y también en esquemas de protección de software. [ cita requerida ] También se ha empleado como un contador de "hardware" en algunos diseños; un ejemplo de esto es el ZX81 , que le permite realizar un seguimiento de las posiciones de los personajes en la pantalla del televisor al activar una interrupción en el bucle (al conectar INT a A6).

El registro de vector de interrupción , I, se utiliza para las interrupciones del modo 2 específicas del Z80 (seleccionadas por la IM 2instrucción). Suministra el byte alto de la dirección base para una tabla de 128 entradas de direcciones de rutina de servicio que se seleccionan a través de un índice enviado a la CPU durante un ciclo de reconocimiento de interrupción ; este índice es simplemente la parte del byte bajo del puntero a la dirección indirecta tabulada que apunta a la rutina de servicio. [22] El puntero identifica un chip periférico particular o una función o evento periférico, donde los chips normalmente están conectados en una llamada cadena de margarita para la resolución de prioridad. Al igual que el registro de actualización, este registro también se ha utilizado a veces de forma creativa; en los modos de interrupción 0 y 1 (o en un sistema que no utiliza interrupciones) se puede utilizar simplemente como otro registro de datos de 8 bits.

Las instrucciones LD A,Ry LD A,Iafectan al registro de indicadores Z80, a diferencia de todas las demás LDinstrucciones (de carga). Los indicadores de signo (bit 7) y cero (bit 6) se configuran de acuerdo con los datos cargados desde los registros de origen de actualización o interrupción. Para ambas instrucciones, el indicador de paridad/desbordamiento (bit 2) se configura de acuerdo con el estado actual del flip-flop IFF2. [37]

Aunque generalmente se considera que el Z80 es una CPU de ocho bits, tiene una ALU de cuatro bits , por lo que los cálculos se realizan en dos pasos. [38]

El primer lenguaje ensamblador del Intel 8008 se basaba en una sintaxis muy simple (pero sistemática) heredada del diseño Datapoint 2200. Esta sintaxis original se transformó posteriormente en una nueva forma de lenguaje ensamblador, algo más tradicional, para este mismo chip 8008 original. Casi al mismo tiempo, el nuevo lenguaje ensamblador también se amplió para dar cabida a los modos de direccionamiento adicionales del chip Intel 8080 más avanzado (el 8008 y el 8080 compartían un subconjunto de lenguaje sin ser compatibles a nivel binario ; sin embargo, el 8008 era compatible a nivel binario con el Datapoint 2200).

En este proceso, la mnemotecnia L, para LOAD , fue reemplazada por varias abreviaturas de las palabras LOAD , STORE y MOVE , entremezcladas con otras letras simbólicas. La letra mnemotécnica M, para memory (referenciada por HL), fue sacada de dentro de la mnemotecnia de instrucción para convertirse en un operando sintácticamente independiente , mientras que los registros y combinaciones de registros comenzaron a denotarse de manera muy inconsistente; ya sea por operandos abreviados (MVI D, LXI H y así sucesivamente), dentro de la mnemotecnia de instrucción misma (LDA, LHLD y así sucesivamente), o ambos al mismo tiempo (LDAX B, STAX D y así sucesivamente).

Ilustración de cuatro sintaxis, utilizando muestras de instrucciones de carga y almacenamiento equivalentes o (para 8086) muy similares. [39] La sintaxis Z80 utiliza paréntesis alrededor de una expresión para indicar que el valor debe usarse como una dirección de memoria (como se menciona a continuación), mientras que la sintaxis 8086 utiliza corchetes en lugar de paréntesis ordinarios para este propósito. Tanto Z80 como 8086 utilizan el signo + para indicar que se agrega una constante a un registro base para formar una dirección. Tenga en cuenta que 8086 no es un superconjunto completo de Z80. BX es el único par de registros 8086 que se puede utilizar como puntero.

Como Intel reclamó los derechos de autor sobre sus mnemotécnicos de ensamblaje, [40] se tuvo que desarrollar una nueva sintaxis de ensamblaje para el Z80. Esta vez se utilizó un enfoque más sistemático:

Estos principios hicieron que fuera sencillo encontrar nombres y formas para todas las nuevas instrucciones del Z80, así como ortogonalizaciones de las antiguas, como LD BC,1234.

Aparte de las diferencias de denominación, y a pesar de una cierta discrepancia en la estructura básica de los registros, la sintaxis del Z80 y del 8086 son prácticamente isomorfas para una gran parte de las instrucciones. Sólo existen similitudes bastante superficiales (como la palabra MOV o la letra X, para registro extendido) entre los lenguajes ensambladores del 8080 y del 8086, aunque los programas del 8080 se pueden traducir al lenguaje ensamblador del 8086 mediante programas traductores . [42] [43]

El Z80 utiliza 252 de los 256 códigos disponibles como códigos de operación de un solo byte ("instrucción raíz", la mayoría de los cuales se heredan del 8080); los cuatro códigos restantes se utilizan ampliamente como prefijos de código de operación: [44] CB y ED habilitan instrucciones adicionales, y DD o FD seleccionan IX+d o IY+d respectivamente (en algunos casos sin desplazamiento d) en lugar de HL. Este esquema proporciona al Z80 una gran cantidad de permutaciones de instrucciones y registros; Zilog los clasifica en 158 "tipos de instrucciones" diferentes, 78 de los cuales son los mismos que los del Intel 8080 [44] (lo que permite el funcionamiento de todos los programas del 8080 en un Z80). La documentación de Zilog [45] agrupa además las instrucciones en las siguientes categorías (la mayoría del 8080, otras completamente nuevas como las instrucciones de bloque y bit, y otras instrucciones del 8080 con modos de direccionamiento más versátiles, como las cargas de 16 bits, E/S, rotaciones/desplazamientos y saltos relativos):

En el Z80 original no hay instrucciones de multiplicación explícitas [46], aunque los registros A y HL se pueden multiplicar por potencias de dos con las instrucciones ADD A,A y ADD HL,HL (de manera similar a IX e IY). Las instrucciones Shift también pueden multiplicar o dividir por potencias de dos.

Los diferentes tamaños y variantes de adiciones, desplazamientos y rotaciones tienen efectos algo diferentes en los indicadores, ya que se copiaron la mayoría de las propiedades de cambio de indicadores del 8080. Sin embargo, el bit de indicador de paridad P del 8080 (bit 2) se denomina P/V (paridad/desbordamiento) en el Z80, ya que cumple la función adicional de indicador de desbordamiento de complemento a dos, una característica de la que carece el 8080. Las instrucciones aritméticas del Z80 lo configuran para indicar desbordamiento en lugar de paridad, mientras que las instrucciones bit a bit aún lo utilizan como indicador de paridad. (Esto introduce una sutil incompatibilidad del Z80 con el código escrito para el 8080, ya que el Z80 a veces indica desbordamiento con signo donde el 8080 indicaría paridad, posiblemente causando que la lógica de algún software práctico del 8080 falle en el Z80. [o] ) Este nuevo indicador de desbordamiento se utiliza para todas las nuevas operaciones de 16 bits específicas del Z80 ( ADC, SBC) así como para operaciones aritméticas de 8 bits, mientras que las operaciones de 16 bits heredadas del 8080 ( ADD, INC, DEC) no lo afectan. Además, el bit 1 del registro de indicadores (un bit de repuesto en el 8080) se utiliza como un indicador N que indica si la última instrucción aritmética ejecutada fue una resta o una suma. La versión Z80 de la DAAinstrucción (acumulador de ajuste decimal para aritmética BCD) verifica el indicador N y se comporta en consecuencia, por lo que una resta (hipotética) seguida posteriormente por DAAproducirá un resultado diferente en un 8080 antiguo que en el Z80. Sin embargo, es probable que se trate de un código erróneo en el 8080, ya que DAAse definió solo para la suma en ese procesador.

El Z80 tiene seis nuevas LDinstrucciones que pueden cargar los pares de registros DE, BC y SP desde la memoria, y cargar la memoria desde estos tres pares de registros, a diferencia del 8080. [39] Al igual que en el 8080, las instrucciones de carga no afectan a los indicadores (excepto las cargas de registros I y R de propósito especial). Un resultado de una codificación regular (común con el 8080) es que cada uno de los registros de 8 bits se puede cargar desde sí mismos (por ejemplo, LD A,A). Esto es efectivamente un NOP.

Las nuevas instrucciones de transferencia de bloques pueden mover hasta 64 kilobytes de memoria a memoria o entre memoria y puertos periféricos de E/S. Las instrucciones de bloque LDIRy LDDR( cargar , incrementar / decrementar , repetir ) usan HL para apuntar a la dirección de origen, DE a la dirección de destino y BC como un contador de bytes. Los bytes se copian de origen a destino, los punteros se incrementan o decrementan, y el contador de bytes se decrementa hasta que BC llega a cero. Las versiones no repetitivas y mueven un solo byte y hacen subir los punteros y el contador de bytes, que si llega a cero reinicia el indicador P/V. Las instrucciones de memoria a E/S correspondientes , , , , , , y funcionan de manera similar, excepto que B, no BC, se usa como contador de bytes. [47] [48] El Z80 puede ingresar y sacar cualquier registro a un puerto de E/S usando el registro C para designar el puerto. (El 8080 solo realiza E/S a través del acumulador A, utilizando una dirección de puerto directo especificada en la instrucción; se requiere una técnica de código automodificable para utilizar una dirección de puerto 8080 variable).LDILDDINIRINDROTIROTDRINIINDOUTIOUTD

El último grupo de instrucciones de bloque realiza una CPoperación de comparación entre el byte en (HL) y el acumulador A. No se utiliza el par de registros DE. Las versiones repetidas CPIRy CPDRsolo terminan si BC va a cero o se encuentra una coincidencia. HL se deja apuntando al byte después ( CPIR) o antes ( CPDR) del byte coincidente. Si no se encuentra ninguna coincidencia, se restablece el indicador Z. Hay versiones no repetidas CPIy CPD.

A diferencia del 8080, el Z80 puede saltar a una dirección relativa ( JRen lugar de JP) utilizando un desplazamiento de 8 bits con signo. Solo los indicadores de cero y de acarreo se pueden probar para estas nuevas JRinstrucciones de dos bytes. (Todos los saltos y llamadas del 8080, condicionales o no, son instrucciones de tres bytes). Una instrucción de dos bytes especializada para bucles de programas también es nueva en el Z80: DJNZ( decrementar salto si no es cero ) toma un desplazamiento de 8 bits con signo como operando inmediato. El registro B se decrementa y, si el resultado es distinto de cero, la ejecución del programa salta en relación con PC; los indicadores permanecen inalterados. Para realizar un bucle equivalente en un 8080 se requieren instrucciones de salto condicionales (a una dirección absoluta de dos bytes) separadas (DEC que suman cuatro bytes), y el DECaltera el registro de indicadores.

Las instrucciones de registro de índice (IX/IY, a menudo abreviadas como XY) pueden ser útiles para acceder a datos organizados en estructuras heterogéneas fijas (como registros ) o en desplazamientos fijos con respecto a una dirección base variable (como en marcos de pila recursivos ) y también pueden reducir el tamaño del código al eliminar la necesidad de múltiples instrucciones cortas que utilicen registros no indexados. Sin embargo, aunque pueden ahorrar velocidad en algunos contextos en comparación con secuencias "equivalentes" largas/complejas de operaciones más simples, incurren en mucho tiempo de CPU adicional (por ejemplo, 19 estados T para acceder a una ubicación de memoria indexada frente a tan solo 11 para acceder a la misma memoria utilizando HL y apuntar a la siguiente). Por lo tanto, para accesos simples o lineales a datos, el uso de IX e IY tiende a ser más lento y ocupa más memoria. Aún así, pueden ser útiles en casos en los que todos los registros "principales" están ocupados, al eliminar la necesidad de guardar/restaurar registros. Sus mitades de 8 bits no documentadas oficialmente (ver más abajo) pueden ser especialmente útiles en este contexto, ya que incurren en menos desaceleración que sus progenitores de 16 bits. De manera similar, las instrucciones para adiciones de 16 bits no son particularmente rápidas (11 ciclos de reloj) en el Z80 original (siendo 1 ciclo más lento que en el 8080/8085); no obstante, son aproximadamente el doble de rápidas que realizar los mismos cálculos utilizando operaciones de 8 bits, e igualmente importante, reducen el uso de registros. No era raro que los programadores "meteran" diferentes bytes de desplazamiento de compensación (que normalmente se calculaban dinámicamente) en instrucciones indexadas; este es un ejemplo de código automodificable , que era una práctica habitual en casi todos los primeros procesadores de 8 bits con unidades de ejecución no segmentadas .INC

Los registros de índice tienen una instrucción paralela a JP (HL), que es JP (XY). Esto se ve a menudo en lenguajes orientados a la pila como Forth , que al final de cada palabra Forth (subrutinas atómicas que componen el lenguaje) deben saltar incondicionalmente de nuevo a sus rutinas de interpretación de subprocesos. Normalmente, esta instrucción de salto aparece cientos de veces en una aplicación, y el uso JP (XY)de en lugar de JP THREADguarda un byte y dos estados T para cada ocurrencia. Esto naturalmente hace que el registro de índice no esté disponible para ningún otro uso, o de lo contrario la necesidad de recargarlo constantemente anularía su eficiencia.

El diseño Z180 , diez años más nuevo y microcodificado , inicialmente podía permitir una mayor "área de chip", lo que permitía una implementación ligeramente más eficiente (utilizando una ALU más amplia , entre otras cosas); se pueden decir cosas similares de los Z800 , Z280 y Z380 . Sin embargo, no fue hasta que se lanzó el eZ80 completamente segmentado en 2001 que esas instrucciones finalmente se volvieron aproximadamente tan eficientes en cuanto a ciclos como es técnicamente posible hacerlas, es decir, dadas las codificaciones Z80 combinadas con la capacidad de hacer una lectura o escritura de 8 bits en cada ciclo de reloj. [ cita requerida ]

Los registros de índice, IX e IY, fueron pensados como punteros flexibles de 16 bits, mejorando la capacidad de manipular la memoria, los marcos de pila y las estructuras de datos. Oficialmente, se los trataba como de 16 bits solamente. En realidad, se implementaron como un par de registros de 8 bits, [49] de la misma manera que el registro HL, al que se puede acceder como de 16 bits o por separado como los registros High y Low . Los códigos de operación binarios (lenguaje de máquina) eran idénticos, pero precedidos por un nuevo prefijo de código de operación. [50] Zilog publicó los códigos de operación y los mnemónicos relacionados para las funciones previstas, pero no documentó el hecho de que cada código de operación que permitía la manipulación de los registros H y L era igualmente válido para las porciones de 8 bits de los registros IX e IY. Por ejemplo, el código de operación 26h seguido de un valor de byte inmediato (LD H,n)cargará ese valor en el registro H. Si se antepone a esta instrucción de dos bytes el prefijo de código de operación del registro IX, DD, se cargarían los 8 bits más significativos del registro IX con ese mismo valor. Una excepción notable a esto serían las instrucciones similares a LD H,(IX+d)las que utilizan tanto los registros HL como los IX o IY en la misma instrucción; [50] en este caso el prefijo DD solo se aplica a la parte (IX+d) de la instrucción. Las mitades de los registros XY también podrían contener operandos para instrucciones aritméticas, lógicas y de comparación de 8 bits, lo que dejaría los registros regulares de 8 bits libres para otros usos. La capacidad no documentada de incrementar y decrementar la mitad superior de un registro de índice facilitó la expansión del rango de las instrucciones indexadas normales, sin tener que recurrir a la documentada ADD/SBC XY,DEo ADD/SBC XY,BC.

También existen otras instrucciones no documentadas. [51] El Z80 no detecta los códigos de operación no documentados o ilegales y estos tienen varios efectos, algunos de los cuales son útiles. Sin embargo, como no forman parte de la definición formal del conjunto de instrucciones, no se garantiza (ni es especialmente probable) que las diferentes implementaciones del Z80 funcionen de la misma manera para cada código de operación no documentado.

La OTDRinstrucción no cumple con la documentación del Z80. Se supone que tanto la instrucción OTDRcomo la instrucción dejan el indicador de acarreo (C) sin modificar. La instrucción funciona correctamente; sin embargo, durante la ejecución de la instrucción, el indicador de acarreo toma los resultados de una comparación espuria entre el acumulador (A) y la última salida de la instrucción. [52]OTIROTIROTDROTDR

El siguiente código fuente de ensamblaje Z80 es para una subrutina llamada memcpyque copia un bloque de bytes de datos de un tamaño determinado de una ubicación a otra. Importante: el código de ejemplo no maneja el caso en el que el bloque de destino se superpone al de origen; una limitación grave, pero que es irrelevante para algunas aplicaciones, como, especialmente, cuando el origen está en ROM y el destino en RAM, por lo que nunca pueden superponerse. El bloque de datos se copia un byte a la vez, y el movimiento de datos y la lógica de bucle utilizan operaciones de 16 bits. Demuestra una variedad de instrucciones, pero en la práctica no se codificaría de esta manera, ya que el Z80 tiene una sola instrucción que reemplazará a toda esta subrutina: LDIR. El código de muestra moverá un byte cada 46 estados T. Sustituir la LDIRinstrucción moverá cada byte en solo 21 estados T. Tenga en cuenta que el código ensamblado es compatible a nivel binario con las CPU Intel 8080 y 8085.

Cada instrucción se ejecuta en pasos que normalmente se denominan ciclos de máquina (ciclos M), cada uno de los cuales puede durar entre tres y seis períodos de reloj (estados T). [53] Cada ciclo M corresponde aproximadamente a un acceso a la memoria o a una operación interna. Muchas instrucciones terminan en realidad durante el M1 de la siguiente instrucción, lo que se conoce como superposición de búsqueda/ejecución .

Los ciclos de máquina Z80 están secuenciados por una máquina de estados interna que construye cada ciclo M a partir de 3, 4, 5 o 6 estados T según el contexto. Esto evita la lógica asincrónica engorrosa y hace que las señales de control se comporten de manera consistente en un amplio rango de frecuencias de reloj. También significa que se debe utilizar un cristal de frecuencia más alta que sin esta subdivisión de ciclos de máquina (aproximadamente 2-3 veces más alta). No implica requisitos más estrictos en los tiempos de acceso a la memoria , ya que un reloj de alta resolución permite un control más preciso de los tiempos de memoria y, por lo tanto, la memoria puede estar activa en paralelo con la CPU en mayor medida, lo que permite un uso más eficiente del ancho de banda de memoria disponible. [ cita requerida ]

Un ejemplo central de esto es que, para la obtención del código de operación , el Z80 combina dos ciclos de reloj completos en un período de acceso a la memoria (la señal M1). En el Z80, esta señal dura una parte relativamente mayor del tiempo típico de ejecución de instrucciones que en un diseño como el 6800 , 6502 o similar, donde este período normalmente duraría típicamente el 30-40% de un ciclo de reloj. [ cita requerida ] Con la asequibilidad del chip de memoria (es decir, tiempos de acceso alrededor de 450-250 ns en la década de 1980 [ cita requerida ] ) determinando típicamente el tiempo de acceso más rápido posible, esto significaba que dichos diseños estaban limitados a un ciclo de reloj significativamente más largo (es decir, menor velocidad de reloj interno) que el Z80.

La memoria era generalmente lenta en comparación con los subciclos de máquina de estados (ciclos de reloj) utilizados en los microprocesadores contemporáneos. Por lo tanto, el ciclo de máquina más corto que se podía utilizar de forma segura en diseños integrados a menudo se veía limitado por los tiempos de acceso a la memoria, no por la frecuencia máxima de la CPU (especialmente durante la era de los ordenadores domésticos). Sin embargo, esta relación ha cambiado lentamente durante las últimas décadas, en particular en lo que respecta a la SRAM ; por lo tanto, los diseños de un solo ciclo sin caché, como el eZ80, han adquirido mucha más importancia recientemente.

El contenido del registro de actualización R se envía a la mitad inferior del bus de direcciones junto con una señal de control de actualización mientras la CPU está decodificando y ejecutando la instrucción obtenida. Durante la actualización, el contenido del registro de interrupción I se envía a la mitad superior del bus de direcciones. [60]

Zilog introdujo una serie de componentes periféricos para el Z80, todos ellos compatibles con el sistema de manejo de interrupciones y el espacio de direcciones de E/S del Z80. Entre ellos se incluyen el canal de contador/temporizador (CTC), [61] el SIO (entrada/salida en serie), el DMA (acceso directo a memoria), el PIO (entrada/salida en paralelo) y el DART (receptor-transmisor asíncrono dual). A medida que se desarrolló la línea de productos, se introdujeron versiones de bajo consumo, alta velocidad y CMOS de estos chips.

Al igual que los procesadores 8080, 8085 y 8086, pero a diferencia de procesadores como el Motorola 6800 y el MOS Technology 6502, el Z80 y el 8080 tienen una línea de control y un espacio de direcciones independientes para las instrucciones de E/S. Si bien algunas computadoras basadas en el Z80, como el Osborne 1 , utilizaban dispositivos de entrada/salida mapeados en memoria "estilo Motorola" , normalmente el espacio de E/S se utilizaba para direccionar uno de los muchos chips periféricos Zilog compatibles con el Z80. Durante la sincronización de una operación de lectura o escritura de E/S, el Z80 inserta automáticamente un único ciclo de espera. [62] Los chips de E/S Zilog admitían las nuevas interrupciones de modo 2 del Z80, lo que simplificaba el manejo de interrupciones para una gran cantidad de periféricos.

El Z80 fue descrito oficialmente como compatible con direccionamiento de memoria de 16 bits (64 KB) y direccionamiento de E/S de 8 bits (256 puertos). Todas las instrucciones de E/S en realidad hacen uso de todo el bus de direcciones de 16 bits. OUT (C),reg e IN reg,(C) colocan el contenido de todo el registro BC de 16 bits en el bus de direcciones; [52] OUT (n),A e IN A,(n) colocan el contenido del registro A en b8–b15 del bus de direcciones y n en b0–b7 del bus de direcciones. Un diseñador podría elegir decodificar todo el bus de direcciones de 16 bits en operaciones de E/S para aprovechar esta característica, o usar la mitad superior del bus de direcciones para seleccionar subcaracterísticas del dispositivo de E/S. Esta característica también se ha utilizado para minimizar los requisitos de hardware de decodificación, como en Amstrad CPC / PCW y ZX81 .

Mostek, que produjo el primer Z80 para Zilog, lo ofreció como segunda fuente como MK3880. SGS-Thomson (ahora STMicroelectronics ) también fue una segunda fuente, con su Z8400. Sharp y NEC desarrollaron segundas fuentes para el NMOS Z80, el LH0080 y el μPD780C , respectivamente. El LH0080 se utilizó en varias computadoras domésticas y computadoras personales fabricadas por Sharp y otros fabricantes japoneses, incluidas las computadoras Sony MSX y varias computadoras de la serie Sharp MZ . [63] Sharp desarrolló el LH0080A y el LH0080B para operar a frecuencias de 4 MHz y 6 MHz, respectivamente. [64] Sharp también desarrolló el LH0083 [65] compatible con Z80 DMA.

Toshiba fabricó una versión CMOS, la TMPZ84C00, que se cree [ ¿quién lo cree? ] (pero no está verificado) que es el mismo diseño que utilizó Zilog para su propio CMOS Z84C00. También hubo chips Z8400 y Z80 fabricados por GoldStar (ahora LG ) y la serie BU18400 de clones Z80 (incluidos DMA, PIO, CTC, DART y SIO) en NMOS y CMOS fabricados por ROHM Electronics . Los LH5080, [66] LH5081, [67] y LH5082, [68] que son versiones CMOS del Z80, PIO y CTC respectivamente, son fabricados por Sharp.

En Alemania del Este se fabricó un clon sin licencia del Z80, conocido como U880 . Se utilizó ampliamente en los sistemas informáticos de Robotron y VEB Mikroelektronik Mühlhausen (como la serie KC85 ) y también en muchos sistemas informáticos de fabricación propia. En Rumania se pudo encontrar otro clon sin licencia, llamado MMN80CPU y producido por Microelectronica , utilizado en ordenadores domésticos como TIM-S, HC, COBRA.

Además, se crearon varios clones del Z80 en la Unión Soviética , siendo los más notables el T34BM1, también llamado КР1858ВМ1 (en paralelo al clon soviético 8080 KR580VM80A ). La primera marca se utilizó en series de preproducción, mientras que la segunda tuvo que usarse para una producción más grande. Sin embargo, debido al colapso de la microelectrónica soviética a fines de la década de 1980, hay muchos más T34BM1 que КР1858ВМ1. [ cita requerida ]

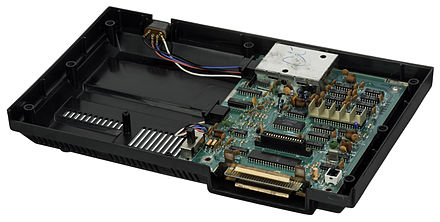

A finales de los años 1970 y principios de los años 1980, el Z80 se utilizó en un gran número de máquinas orientadas a los negocios bastante anónimas con el sistema operativo CP/M , una combinación que dominaba el mercado en ese momento. [84] [85] Cuatro ejemplos conocidos de computadoras comerciales Z80 que ejecutan CP/M son el Heathkit H89 , el portátil Osborne 1 , la serie Kaypro y el Epson QX-10 . Menos conocido fue el costoso Otrona Attache de alta gama. [86] Algunos sistemas usaban software de sistema operativo multitarea (como MP/M o Micronix de Morrow ) para compartir el procesador entre varios usuarios simultáneos .

Se introdujeron múltiples computadoras domésticas que usaban el Z80 como procesador principal o como una opción de complemento para permitir el acceso al software escrito para el Z80. Destacan la serie TRS-80 , incluido el modelo original (posteriormente rebautizado como "Modelo I"), el Modelo II , el Modelo III y el Modelo 4 , que estaban equipados con un Z80 como procesador principal, y algunos (pero no todos) otros modelos TRS-80 que usaban el Z80 como procesador principal o secundario. Otras máquinas notables fueron el DEC Rainbow 100 y el Seequa Chameleon , que presentaban tanto un Intel 8088 como una CPU Z80, para admitir aplicaciones CP/M-80 de 8 bits que se ejecutaban en el Z80, o un MS-DOS personalizado que no era totalmente compatible con aplicaciones PC DOS que se ejecutaban en el 8088.

En 1981, Multitech (que más tarde se convertiría en Acer ) presentó el Microprofessor I , un sistema de entrenamiento sencillo y económico para el microprocesador Z80. En la actualidad, todavía lo fabrica y vende Flite Electronics International Limited en Southampton, Inglaterra .

En 1984, Toshiba presentó el Toshiba MSX HX-10 en Japón y Australia.

En 1985, Sharp presentó el Hotbit y Gradiente presentó el Expert , que se convirtieron en las computadoras domésticas de 8 bits dominantes en Brasil hasta finales de la década de 1980.

El uso del Z80 en dispositivos más ligeros y que funcionaban con baterías se generalizó con la disponibilidad de versiones CMOS del procesador. También inspiró el desarrollo de otros procesadores basados en CMOS, como el LH5801 [87] de Sharp. El Sharp PC-1500 , un ordenador de bolsillo programable en BASIC , se lanzó en 1981, seguido por el Sharp PC-1600 mejorado en 1986 y el Sharp PC-E220 en 1991. Los modelos posteriores de la serie Sharp Wizard de organizadores personales también estaban basados en Z80. Los portátiles que podían ejecutar el sistema operativo CP/M al igual que las máquinas de escritorio siguieron con el Epson PX-8 Geneva en 1984, y en 1985 el Epson PX-4 y el Bondwell-2 . Mientras que el mercado de las computadoras portátiles en los años siguientes se movió hacia procesadores Intel 8086 más potentes y el sistema operativo MS-DOS, todavía se estaban introduciendo sistemas ligeros basados en Z80 con una mayor duración de la batería, como el Cambridge Z88 en 1988 y el Amstrad NC100 en 1992. El Z8S180 derivado del Z80 también encontró su camino en uno de los primeros asistentes digitales personales operados con lápiz , el Amstrad PenPad PDA600 en 1993. VTech, con sede en Hong Kong, produjo una línea de pequeñas computadoras portátiles llamadas 'Lasers' basadas en un Z80. [88] [89] Los dos últimos fueron el Laser PC5 [90] y el PC6. [91] El Cidco MailStation Mivo 100, lanzado por primera vez en 1999, era un dispositivo de correo electrónico portátil independiente, con un microcontrolador basado en Z80. [92] Texas Instruments produjo una línea de organizadores de bolsillo (que finalizó en 2000) utilizando procesadores Toshiba construidos alrededor de un núcleo Z80; el primero de ellos fue el TI PS-6200 [93] y después de una larga producción de unas docenas de modelos culminó en su serie PocketMate. [94]

El Zilog Z80 ha sido durante mucho tiempo un microprocesador popular en sistemas integrados y núcleos de microcontroladores , [36] donde sigue siendo de uso generalizado en la actualidad. [26] [95] Las aplicaciones del Z80 incluyen usos en electrónica de consumo , productos industriales e instrumentos musicales electrónicos. Por ejemplo, el Z80 se utilizó en el innovador sintetizador musical Prophet-5 , [96] así como en el primer sintetizador MIDI Prophet 600. [97] Casio utilizó el Z80A en su consola de videojuegos PV-1000 .

Una buena cantidad de videojuegos arcade de principios de la década de 1980, incluido el juego arcade Pac-Man , contienen CPU Z80.

El Z80 se utilizó en las consolas Master System y Game Gear de Sega . La Sega Genesis contiene un Z80, con sus propios 8 KB de RAM, que funciona en paralelo con la CPU principal MC68000, tiene acceso directo a los chips de sonido del sistema y a los puertos de E/S (controlador), y tiene una ruta de datos conmutada al bus de memoria principal del 68000 (que proporciona acceso a la RAM principal de 64 KB, al cartucho de software y a todo el chip de vídeo); además de proporcionar compatibilidad con versiones anteriores de los juegos de Master System, el Z80 se utiliza a menudo para controlar y reproducir audio en el software de Genesis. [p]

Las CPU Z80 también se utilizaron en la pionera y popular serie de calculadoras gráficas TI-8x de Texas Instruments , comenzando en 1990 con la TI-81 , que cuenta con un Z80 con una frecuencia de reloj de 2 MHz. La mayoría de las calculadoras de línea superior de la serie, comenzando con la TI-82 y la TI-85 , tienen sus CPU Z80 a 6 MHz o más. (Algunos modelos con nombres TI-8x usan otras CPU, como la M68000, pero la gran mayoría están basadas en Z80. En ellas, es posible ejecutar programas de usuario ensamblados o compilados en forma de código de lenguaje de máquina Z80). La serie TI-84 Plus , presentada en 2004, todavía está en producción a partir de 2023. La serie TI-84 Plus CE , presentada en 2015, utiliza el procesador Zilog eZ80 derivado de Z80 y también sigue en producción a partir de 2024.

A finales de la década de 1980, una serie de teléfonos fijos soviéticos llamados "AON" presentaron el Z80; estos teléfonos ampliaron el conjunto de funciones de los teléfonos fijos con identificador de llamadas , diferentes tonos de llamada según la persona que llama, marcación rápida , etc. [98] Sin embargo, en la segunda mitad de la década de 1990, los fabricantes de estos teléfonos cambiaron a MCU compatibles con 8051 para reducir el consumo de energía y evitar que los adaptadores de corriente de pared compactos se sobrecalienten.

El 15 de abril de 2024, Zilog anunció la discontinuación del procesador Z80 y que se aceptarían pedidos hasta el 14 de junio de 2024. El anuncio incluía 13 variantes del procesador Z80, muchas de las cuales eran variantes DIP40 del chip. Zilog continuará fabricando la versión eZ80 mejorada del procesador. [99]

JP), que cargan el contador del programa con una nueva dirección de instrucción, no acceden a la memoria. Las formas absolutas y relativas del salto reflejan esto omitiendo los corchetes de sus operandos. Las instrucciones de salto basadas en registros, como " JP (HL)", incluyen corchetes en una aparente desviación de esta convención. [41]ADDsumarle un cero, al SUBrestarle un cero, o al ORsumarle o XORrestarle un cero; todas estas son operaciones de una sola instrucción de la misma velocidad y tamaño, tanto en el 8080 como en el Z80. Si el programador eligiera probar la paridad al ORsumarle o XORrestarle un cero, entonces el Z80 ejecutará el programa correctamente, pero si el programador eligiera probar la paridad al ADDsumarle o SUBrestarle un cero, entonces el Z80 siempre restablecerá el indicador P/V a cero (ya que sumar o restar cero nunca causa un desbordamiento o subdesbordamiento) en lugar de asignar P para indicar correctamente la paridad del byte (como lo haría el 8080—o el 8085—), y el programa puede fallar. Nada en los manuales de programación de Intel u otra documentación para el 8080 desaconseja el uso de instrucciones aritméticas o prescribe el uso de instrucciones lógicas para probar la paridad, por lo que no hay motivo para esperar que un programador del 8080 que ejerza las buenas prácticas de programación recomendadas haya elegido una de las formas que funcionarán en el Z80 en lugar de una de las formas que no funcionarán.la interrupción comienza de acuerdo con el método de interrupción estipulado por la instrucción IM i , i = 0, 1 o 2. Si i = 1, para el método directo, la PC se carga con 0038H. Si i = 0, para el método vectorial, el dispositivo de interrupción tiene la oportunidad de colocar el código de operación para un byte. Si i = 2, para el método vectorial indirecto, el dispositivo de interrupción debe colocar un byte. El Z80 luego usa este byte donde se puede seleccionar uno de los 128 vectores de interrupción por byte.

La arquitectura de registros del Z80 es más innovadora que la del 8085.

En el mundo de los 8 bits, los dos microordenadores más populares son los chips informáticos Z80 y 6502.

Además de soportar todo el conjunto de instrucciones del Z80, el Z180

Los diseñadores eligieron una arquitectura compatible con el Z80, lo que les brinda a los usuarios del Z80 una ruta de actualización completamente compatible con el software. El procesador 64180 ejecuta cada instrucción del Z80 exactamente como lo hace un Z80.

Todos los mnemónicos son propiedad intelectual de Intel Corporation 1977.

[...] El 8086 es compatible con el software del 8080 a nivel de lenguaje ensamblador. [...]

[...] Un programa traductor de Intel podría convertir programas ensambladores 8080 en programas ensambladores 8086 [...]

Tiene un lenguaje de 252 instrucciones raíz y con los 4 bytes reservados como prefijos, accede a 308 instrucciones adicionales.

Los microprocesadores de 8 bits que precedieron a la familia 80x86 (como el Intel 8080, el Zilog Z80 y el Motorola) no incluían la multiplicación.

permiten operaciones de 8 bits con registros IX e IY.

Si un código de operación funciona con los registros HL, H o L, entonces, si ese código de operación está precedido por #DD (o #FD), funciona en IX, IXH o IXL (o IY, IYH, IYL), con algunas excepciones. Las excepciones son instrucciones como LD H, IXH y LD L, IYH.

Las instrucciones de E/S utilizan todo el bus de direcciones, no solo los 8 bits inferiores. De hecho, puede tener 65536 puertos de E/S en un sistema Z80 (el Spectrum los utiliza). IN r,(C), OUT (C),r y todas las instrucciones del bloque de E/S colocan todo el BC en el bus de direcciones. IN A,(n) y OUT (n),A colocan A*256+n en el bus de direcciones.

AGREGAR A, n Agrega acumulador con datos inmediatos n. MEMORIA Temporización: 2 M ciclos; 7 T estados.

La mayoría de las MZ utilizan la CPU de 8 bits LH0080/Z80 [...]

El 64180 es un núcleo Z80 suministrado por Hitachi con numerosos "extras" en el chip. La versión de Zilog es el Z180, que es esencialmente la misma pieza.

Tanto Toshiba como Zilog venden los modelos 84013 y 84015, que son núcleos Z80 con periféricos Z80 convencionales integrados en la placa.

Los KL5C80A12, KL5C80A16 y KL5C8400 de Kawasaki son

microcontroladores

y CPU de 8 bits de alta velocidad. Su código de CPU, KC80, es compatible con el Z80 de Zilog a nivel binario. El KC80 ejecuta instrucciones aproximadamente cuatro veces más rápido que el Z80 a la misma velocidad de reloj.

, que es un derivado muy mejorado y optimizado del venerable microprocesador Z80 de ZiLOG, Inc.

se basan estrechamente en la arquitectura Zilog Z180, aunque no son compatibles binariamente con las piezas Zilog.

y CP/M continuaron dominando el mundo de las microcomputadoras de 8 bits.

La idea de un sistema operativo genérico todavía está en pañales. En muchos sentidos, comienza con CP/M y la mezcolanza de las primeras computadoras 8080 y Z80.

Fuentes

Simuladores / Emuladores: