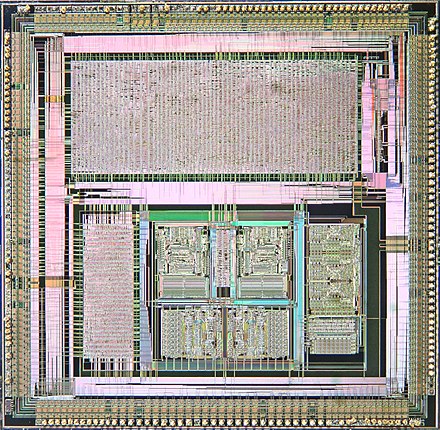

Un circuito integrado de aplicación específica ( ASIC / ˈ eɪ s ɪ k / ) es un chip de circuito integrado (CI) personalizado para un uso particular, en lugar de estar destinado a un uso de propósito general, como un chip diseñado para ejecutarse en una grabadora de voz digital o un códec de video de alta eficiencia . [1] Los chips de productos estándar de aplicación específica son intermedios entre los ASIC y los circuitos integrados estándar de la industria como la serie 7400 o la serie 4000. [2] Los chips ASIC generalmente se fabrican utilizando tecnología de semiconductor de óxido de metal (MOS), como chips de circuito integrado MOS . [3]

A medida que los tamaños de las características se han reducido y las herramientas de diseño de chips han mejorado con el paso de los años, la complejidad máxima (y, por lo tanto, la funcionalidad) posible en un ASIC ha crecido de 5000 puertas lógicas a más de 100 millones. Los ASIC modernos a menudo incluyen microprocesadores completos , bloques de memoria que incluyen ROM , RAM , EEPROM , memoria flash y otros bloques de construcción grandes. Un ASIC de este tipo a menudo se denomina SoC ( sistema en chip ). Los diseñadores de ASIC digitales a menudo utilizan un lenguaje de descripción de hardware (HDL), como Verilog o VHDL , para describir la funcionalidad de los ASIC. [2]

Las matrices de puertas programables en campo (FPGA) son la mejora tecnológica moderna en placas de pruebas , lo que significa que no están hechas para ser específicas de la aplicación a diferencia de los ASIC. Los bloques lógicos programables y las interconexiones programables permiten que el mismo FPGA se use en muchas aplicaciones diferentes. Para diseños más pequeños o volúmenes de producción más bajos, los FPGA pueden ser más rentables que un diseño ASIC, incluso en producción. El costo de ingeniería no recurrente (NRE) de un ASIC puede llegar a millones de dólares. Por lo tanto, los fabricantes de dispositivos generalmente prefieren FPGA para prototipos y dispositivos con bajo volumen de producción y ASIC para volúmenes de producción muy grandes donde los costos de NRE se pueden amortizar en muchos dispositivos. [4]

Los primeros ASIC utilizaban tecnología de matriz de compuertas . En 1967, Ferranti e Interdesign ya fabricaban las primeras matrices de compuertas bipolares . En 1967, Fairchild Semiconductor introdujo la familia Micromatrix de matrices de lógica bipolar de diodo-transistor (DTL) y lógica transistor-transistor (TTL). [3]

La tecnología de semiconductores complementarios de óxido metálico (CMOS) abrió la puerta a la amplia comercialización de matrices de puertas. Las primeras matrices de puertas CMOS fueron desarrolladas por Robert Lipp, [5] [6] en 1974 para International Microcircuits, Inc. (IMI). [3]

La tecnología de celda estándar de semiconductor de óxido de metal (MOS) fue introducida por Fairchild y Motorola , bajo los nombres comerciales Micromosaic y Polycell, en la década de 1970. Esta tecnología fue comercializada posteriormente con éxito por VLSI Technology (fundada en 1979) y LSI Logic (1981). [3]

Una aplicación comercial exitosa de los circuitos de matriz de puertas se encontró en las computadoras personales de 8 bits de gama baja ZX81 y ZX Spectrum , introducidas en 1981 y 1982. Estas fueron utilizadas por Sinclair Research (Reino Unido) esencialmente como una solución de E/S de bajo costo destinada a manejar los gráficos de la computadora .

La personalización se produjo modificando una máscara de interconexión de metal. Las matrices de puertas tenían complejidades de hasta unos pocos miles de puertas; esto ahora se llama integración de escala media . Las versiones posteriores se generalizaron, con diferentes matrices de base personalizadas tanto con capas de metal como de polisilicio . Algunas matrices de base también incluyen elementos de memoria de acceso aleatorio (RAM).

A mediados de la década de 1980, un diseñador elegía un fabricante de ASIC e implementaba su diseño utilizando las herramientas de diseño disponibles del fabricante. Si bien existían herramientas de diseño de terceros, no había un vínculo efectivo entre las herramientas de diseño de terceros y el diseño y las características reales de rendimiento del proceso de semiconductores de los diversos fabricantes de ASIC. La mayoría de los diseñadores usaban herramientas específicas de fábrica para completar la implementación de sus diseños. Una solución a este problema, que también produjo un dispositivo de densidad mucho mayor, fue la implementación de celdas estándar . [7] Cada fabricante de ASIC podía crear bloques funcionales con características eléctricas conocidas, como retardo de propagación , capacitancia e inductancia, que también podían representarse en herramientas de terceros. El diseño de celdas estándar es la utilización de estos bloques funcionales para lograr una densidad de compuertas muy alta y un buen rendimiento eléctrico. El diseño de celdas estándar es intermedio entre § Diseño de matriz de compuertas y semipersonalizado y § Diseño totalmente personalizado en términos de ingeniería no recurrente y costos de componentes recurrentes, así como rendimiento y velocidad de desarrollo (incluido el tiempo de comercialización ).

A fines de la década de 1990, se empezaron a utilizar herramientas de síntesis lógica que podían compilar descripciones HDL en una lista de conexiones a nivel de compuerta. Los circuitos integrados (CI) de celda estándar se diseñan en las siguientes etapas conceptuales, denominadas flujo de diseño electrónico , aunque estas etapas se superponen significativamente en la práctica:

Estos pasos, implementados con un nivel de habilidad común en la industria, casi siempre producen un dispositivo final que implementa correctamente el diseño original, a menos que posteriormente se introduzcan fallas por el proceso de fabricación física. [8]

Los pasos de diseño, también denominados flujo de diseño , también son comunes al diseño de productos estándar. La diferencia significativa es que el diseño de celdas estándar utiliza las bibliotecas de celdas del fabricante que se han utilizado en cientos de otras implementaciones de diseño y, por lo tanto, tienen un riesgo mucho menor que un diseño totalmente personalizado. Las celdas estándar producen una densidad de diseño que es rentable y también pueden integrar núcleos IP y memoria de acceso aleatorio estática (SRAM) de manera eficaz, a diferencia de las matrices de puertas.

El diseño de matriz de puertas es un método de fabricación en el que se predefinen capas difusas, cada una de las cuales consta de transistores y otros dispositivos activos , y las obleas electrónicas que contienen dichos dispositivos se "mantienen en stock" o se desconectan antes de la etapa de metalización del proceso de fabricación . El proceso de diseño físico define las interconexiones de estas capas para el dispositivo final. Para la mayoría de los fabricantes de ASIC, esto consiste en entre dos y nueve capas de metal, cada capa perpendicular a la que está debajo. Los costos de ingeniería no recurrentes son mucho más bajos que los diseños personalizados completos, ya que las máscaras fotolitográficas solo se requieren para las capas de metal. Los ciclos de producción son mucho más cortos, ya que la metalización es un proceso comparativamente rápido, lo que acelera el tiempo de comercialización .

Los ASIC de matriz de puertas son siempre un compromiso entre el diseño rápido y el rendimiento , ya que la asignación de un diseño determinado a lo que un fabricante tenía como oblea de serie nunca permite una utilización del circuito del 100 % . A menudo, las dificultades para enrutar la interconexión requieren la migración a un dispositivo de matriz más grande, con el consiguiente aumento del precio de las piezas. Estas dificultades suelen ser el resultado del software EDA de diseño utilizado para desarrollar la interconexión.

En la actualidad, los diseñadores de circuitos rara vez implementan diseños de matrices de puertas puras y basadas únicamente en lógica, ya que han sido reemplazadas casi por completo por dispositivos programables en campo . Los más destacados de estos dispositivos son las matrices de puertas programables en campo (FPGA), que pueden ser programadas por el usuario y, por lo tanto, ofrecen costos mínimos de herramientas, ingeniería no recurrente, un costo de pieza solo marginalmente mayor y un rendimiento comparable.

En la actualidad, las matrices de puertas están evolucionando hacia ASIC estructurados que constan de un núcleo IP grande como una CPU , unidades de procesamiento de señales digitales , periféricos , interfaces estándar , memorias integradas , SRAM y un bloque de lógica reconfigurable y no comprometida. Este cambio se debe en gran medida a que los dispositivos ASIC son capaces de integrar grandes bloques de funcionalidad del sistema , y los sistemas en un chip (SoC) requieren lógica de unión , subsistemas de comunicaciones (como redes en chip ), periféricos y otros componentes en lugar de solo unidades funcionales e interconexión básica.

En el uso frecuente que se hace de los ASIC, los términos "matriz de compuertas" y "semipersonalizado" son sinónimos. Los ingenieros de procesos suelen utilizar el término "semipersonalizado", mientras que los diseñadores de lógica (o de nivel de compuerta) suelen utilizar "matriz de compuertas".

Por el contrario, el diseño ASIC totalmente personalizado define todas las capas fotolitográficas del dispositivo. [7] El diseño totalmente personalizado se utiliza tanto para el diseño ASIC como para el diseño de productos estándar.

Los beneficios del diseño totalmente personalizado incluyen una reducción del área (y, por lo tanto, del costo recurrente de los componentes), mejoras en el rendimiento y también la capacidad de integrar componentes analógicos y otros componentes prediseñados (y, por lo tanto, completamente verificados), como núcleos de microprocesador , que forman un sistema en un chip .

Las desventajas de un diseño totalmente personalizado pueden incluir un mayor tiempo de fabricación y diseño, mayores costos de ingeniería no recurrentes, mayor complejidad en los sistemas de diseño asistido por computadora (CAD) y de automatización del diseño electrónico , y un requisito de habilidades mucho mayor por parte del equipo de diseño.

Sin embargo, para los diseños exclusivamente digitales, las bibliotecas de celdas de "celdas estándar", junto con los sistemas CAD modernos, pueden ofrecer considerables ventajas en términos de rendimiento y costo con un bajo riesgo. Las herramientas de diseño automatizadas son rápidas y fáciles de usar y también ofrecen la posibilidad de "modificar manualmente" u optimizar manualmente cualquier aspecto del diseño que limite el rendimiento.

Este está diseñado mediante el uso de puertas lógicas básicas, circuitos o diseños especiales para un diseño.

El diseño de ASIC estructurado (también conocido como " diseño de ASIC de plataforma ") es una tendencia relativamente nueva en la industria de semiconductores, lo que da lugar a algunas variaciones en su definición. Sin embargo, la premisa básica de un ASIC estructurado es que tanto el tiempo del ciclo de fabricación como el del diseño se reducen en comparación con el ASIC basado en celdas, en virtud de que existen capas de metal predefinidas (lo que reduce el tiempo de fabricación) y la caracterización previa de lo que hay en el silicio (lo que reduce el tiempo del ciclo de diseño).

La definición de Fundamentos de sistemas integrados establece que: [9]

En un diseño "ASIC estructurado", las capas de máscara lógica de un dispositivo están predefinidas por el proveedor del ASIC (o en algunos casos por un tercero). La diferenciación y personalización del diseño se logra mediante la creación de capas de metal personalizadas que crean conexiones personalizadas entre elementos lógicos de capa inferior predefinidos. La tecnología "ASIC estructurado" se considera que cierra la brecha entre las matrices de puertas programables en campo y los diseños ASIC de "celda estándar". Debido a que solo se debe producir de manera personalizada una pequeña cantidad de capas de chip, los diseños "ASIC estructurado" tienen gastos no recurrentes (NRE) mucho menores que los chips de "celda estándar" o "totalmente personalizados", que requieren que se produzca un conjunto de máscaras completo para cada diseño.

— Fundamentos de los sistemas integrados

Esta es, en efecto, la misma definición que la de matriz de compuertas. Lo que distingue a un ASIC estructurado de una matriz de compuertas es que en una matriz de compuertas, las capas de metal predefinidas sirven para acelerar el proceso de fabricación. En un ASIC estructurado, el uso de metalización predefinida tiene como objetivo principal reducir el costo de los conjuntos de máscaras, además de acortar significativamente el tiempo del ciclo de diseño.

Por ejemplo, en un diseño basado en celdas o en matrices de compuertas, el usuario a menudo debe diseñar por sí mismo las estructuras de potencia, reloj y prueba. Por el contrario, estas están predefinidas en la mayoría de los ASIC estructurados y, por lo tanto, pueden ahorrar tiempo y gastos al diseñador en comparación con los diseños basados en matrices de compuertas. Asimismo, las herramientas de diseño utilizadas para ASIC estructurados pueden tener un costo sustancialmente menor y ser más fáciles (más rápidas) de usar que las herramientas basadas en celdas, porque no tienen que realizar todas las funciones que realizan las herramientas basadas en celdas. En algunos casos, el proveedor de ASIC estructurado requiere que se utilicen herramientas personalizadas para su dispositivo (por ejemplo, síntesis física personalizada), lo que también permite que el diseño se lleve a fabricación más rápidamente.

Las bibliotecas de celdas de primitivas lógicas suelen ser proporcionadas por el fabricante del dispositivo como parte del servicio. Aunque no implican ningún coste adicional, su publicación estará amparada por los términos de un acuerdo de confidencialidad (NDA) y serán consideradas propiedad intelectual por el fabricante. Normalmente, su diseño físico estará predefinido, por lo que podrían denominarse "macros duros".

Lo que la mayoría de los ingenieros entienden como " propiedad intelectual " son los núcleos IP , diseños comprados a un tercero como subcomponentes de un ASIC más grande. Pueden proporcionarse en forma de un lenguaje de descripción de hardware (a menudo denominado "macro suave"), o como un diseño completamente enrutado que podría imprimirse directamente en la máscara de un ASIC (a menudo denominado "macro duro"). Muchas organizaciones ahora venden estos núcleos prediseñados (CPU, Ethernet, USB o interfaces telefónicas) y las organizaciones más grandes pueden tener un departamento o división completo para producir núcleos para el resto de la organización. La empresa ARM solo vende núcleos IP, lo que la convierte en un fabricante fabless .

De hecho, la amplia gama de funciones disponibles actualmente en el diseño de ASIC estructurado es resultado de la fenomenal mejora en la electrónica a finales de los años 1990 y principios de los años 2000; como crear un núcleo requiere mucho tiempo e inversión, su reutilización y desarrollo posterior reduce drásticamente los tiempos de ciclo del producto y crea productos mejores. Además, las organizaciones de hardware de código abierto como OpenCores están recopilando núcleos de propiedad intelectual gratuitos, en paralelo con el movimiento de software de código abierto en el diseño de hardware.

Las macros blandas suelen ser independientes del proceso (es decir, se pueden fabricar en una amplia gama de procesos de fabricación y con distintos fabricantes). Las macros duras están limitadas por el proceso y, por lo general, se debe invertir más esfuerzo de diseño para migrarlas (transferirlas) a un proceso o fabricante diferente.

Algunos fabricantes y casas de diseño de circuitos integrados ofrecen un servicio de obleas multiproyecto (MPW, por sus siglas en inglés) como método para obtener prototipos de bajo costo. Estos MPW, que a menudo se denominan lanzaderas, contienen varios diseños y se ejecutan a intervalos regulares y programados sobre la base de "cortar y listo", generalmente con una responsabilidad limitada por parte del fabricante. El contrato implica la entrega de matrices desnudas o el ensamblaje y empaquetado de un puñado de dispositivos. El servicio generalmente implica el suministro de una base de datos de diseño física (es decir, información de enmascaramiento o cinta de generación de patrones (PG, por sus siglas en inglés)). El fabricante a menudo se conoce como una "fundición de silicio" debido a la baja participación que tiene en el proceso.

Un producto estándar específico de la aplicación o ASSP es un circuito integrado que implementa una función específica que resulta atractiva para un mercado amplio. A diferencia de los ASIC, que combinan una colección de funciones y están diseñados por o para un cliente , los ASSP están disponibles como componentes listos para usar. Los ASSP se utilizan en todas las industrias, desde la automotriz hasta las comunicaciones. [ cita requerida ] Como regla general, si puede encontrar un diseño en un libro de datos , probablemente no sea un ASIC, pero existen algunas excepciones. [ aclaración necesaria ]

Por ejemplo, dos circuitos integrados que podrían o no considerarse ASIC son un chip controlador para una PC y un chip para un módem . Ambos ejemplos son específicos de una aplicación (lo que es típico de un ASIC), pero se venden a muchos proveedores de sistemas diferentes (lo que es típico de las piezas estándar). Los ASIC como estos a veces se denominan productos estándar específicos de la aplicación (ASSP).

Algunos ejemplos de ASSP son el chip de codificación/decodificación, el chip controlador de interfaz de red Ethernet, etc.

{{cite book}}: |website=ignorado ( ayuda )