El CDC 6600 fue el buque insignia de la serie 6000 de sistemas de computadoras mainframe fabricados por Control Data Corporation . [8] [9] Generalmente considerado como el primer superordenador exitoso , superó al anterior poseedor del récord de la industria, el IBM 7030 Stretch , por un factor de tres. [10] [11] Con un rendimiento de hasta tres megaFLOPS , [12] [13] el CDC 6600 fue el ordenador más rápido del mundo desde 1964 hasta 1969, cuando cedió ese estatus a su sucesor, el CDC 7600. [14]

Los primeros CDC 6600 se entregaron en 1965 a Livermore y Los Álamos . [15] Rápidamente se convirtieron en un sistema imprescindible en la computación matemática y científica de alto nivel, y se entregaron sistemas al Instituto Courant de Ciencias Matemáticas , al CERN , [16] [17] al Laboratorio de Radiación Lawrence , [18] y a muchos otros. Se entregaron al menos 100 en total. [19]

En el Museo de Historia de la Computación de Mountain View, California , se exhibe una CDC 6600. La única máquina de la serie CDC 6000 que sigue en funcionamiento ha sido restaurada por Living Computers: Museum + Labs .

Los primeros productos de CDC se basaron en las máquinas diseñadas en Engineering Research Associates (ERA), que a Seymour Cray se le había pedido que actualizara después de mudarse a CDC. Después de una máquina experimental conocida como Little Character , [20] en 1960 entregaron el CDC 1604 , uno de los primeros ordenadores comerciales basados en transistores y una de las máquinas más rápidas del mercado. La gerencia estaba encantada e hizo planes para una nueva serie de máquinas que estuvieran más adaptadas al uso comercial; incluirían instrucciones para el manejo de caracteres y el mantenimiento de registros, por ejemplo. Cray no estaba interesado en un proyecto así y se fijó el objetivo de producir una nueva máquina que fuera 50 veces más rápida que la 1604. Cuando se le preguntó [ ¿cuándo? ] que completara un informe detallado sobre los planes a uno y cinco años en el futuro, respondió que su objetivo a cinco años era "producir el ordenador más grande del mundo", siendo "más grande" en ese momento sinónimo de "más rápido", y que su plan de un año era "estar en una quinta parte del camino". [21]

Tras trasladar a su equipo central a unas nuevas oficinas cerca de la sede original de CDC, empezaron a experimentar con versiones de mayor calidad de los transistores "baratos" que Cray había utilizado en el 1604. Tras mucha experimentación, descubrieron que no había forma de que los transistores basados en germanio pudieran funcionar mucho más rápido que los utilizados en el 1604. La "máquina de negocios" que la dirección había querido originalmente, que ahora se estaba formando como la serie CDC 3000 , los llevó hasta donde podían llegar. Cray decidió entonces que la solución era trabajar con los entonces nuevos transistores basados en silicio de Fairchild Semiconductor , que acababan de salir al mercado y ofrecían un rendimiento de conmutación drásticamente mejorado.

Durante este período, CDC pasó de ser una empresa emergente a convertirse en una gran empresa y Cray se sentía cada vez más frustrado por lo que consideraba requisitos de gestión ridículos. Las cosas se pusieron considerablemente más tensas en 1962, cuando el nuevo CDC 3600 empezó a acercarse a la calidad de producción y parecía ser exactamente lo que la dirección quería, cuando lo quería. Cray acabó comunicándole al director ejecutivo de CDC, William Norris , que algo tenía que cambiar o dejaría la empresa. Norris sentía que era demasiado importante como para perderlo y le dio luz verde a Cray para que estableciera un nuevo laboratorio donde quisiera.

Después de una breve búsqueda, Cray decidió regresar a su ciudad natal de Chippewa Falls, Wisconsin , donde compró un terreno y puso en marcha un nuevo laboratorio. [ ¿cuándo? ]

Aunque este proceso supuso un retraso bastante prolongado en el diseño de su nueva máquina, una vez en el nuevo laboratorio, sin la intervención de la dirección, las cosas empezaron a progresar rápidamente. Para entonces, los nuevos transistores se estaban volviendo bastante fiables y los módulos construidos con ellos tendían a funcionar correctamente a la primera. El 6600 empezó a tomar forma, con Cray trabajando junto a Jim Thornton , arquitecto de sistemas y "genio oculto" del 6600.

Durante la vida útil de la máquina (entre 1964 y 1969) se vendieron más de 100 CDC 6600. Muchos de ellos se destinaron a diversos laboratorios relacionados con las armas nucleares y unos cuantos acabaron en laboratorios informáticos universitarios. Un CDC 6600 se utilizó para refutar la conjetura de la suma de potencias de Euler en un ejemplo temprano de búsqueda numérica directa. [22]

Cray se concentró inmediatamente en su reemplazo, y esta vez se fijó el objetivo de multiplicar por diez el rendimiento del 6600, que se presentó como CDC 7600. Las computadoras CDC Cyber 70 y 170 posteriores [¿ cuándo? ] eran muy similares al CDC 6600 en diseño general y eran casi completamente compatibles con versiones anteriores.

El 6600 era tres veces más rápido que el anterior poseedor del récord, el IBM 7030 Stretch ; esto alarmó a IBM . El entonces director ejecutivo Thomas Watson Jr. escribió una nota a sus empleados el 28 de agosto de 1963: "La semana pasada, Control Data ... anunció el sistema 6600. Entiendo que en el laboratorio que desarrolla el sistema hay sólo 34 personas, incluido el conserje. De ellos, 14 son ingenieros y 4 son programadores ... Comparando este modesto esfuerzo con nuestras vastas actividades de desarrollo, no entiendo por qué hemos perdido nuestra posición de liderazgo en la industria al permitir que alguien más ofrezca el ordenador más potente del mundo". La respuesta de Cray fue sardónica: "Parece que el Sr. Watson ha respondido a su propia pregunta". [23] [24]

Las máquinas típicas de los años 1950 y 1960 utilizaban una sola unidad central de procesamiento (CPU) para controlar todo el sistema. [25] Un programa típico primero cargaba datos en la memoria (a menudo utilizando un código de biblioteca predefinido), los procesaba y luego los volvía a escribir. Esto requería que las CPU fueran bastante complejas para manejar el conjunto completo de instrucciones que se les pediría que ejecutaran. Una CPU compleja implicaba una CPU grande, lo que introducía retrasos en la señalización mientras la información fluía entre los módulos individuales que la componían. Estos retrasos establecían un límite superior máximo en el rendimiento, ya que la máquina solo podía funcionar a una velocidad de ciclo que permitiera que las señales tuvieran tiempo de llegar al siguiente módulo.

Cray adoptó otro enfoque. En la década de 1960, las CPU generalmente funcionaban más lentamente que la memoria principal a la que estaban conectadas. Por ejemplo, un procesador podía tardar 15 ciclos en multiplicar dos números, mientras que cada acceso a la memoria solo necesitaba uno o dos ciclos. Esto significaba que había un tiempo significativo en el que la memoria principal estaba inactiva. Fue este tiempo inactivo el que el 6600 aprovechó.

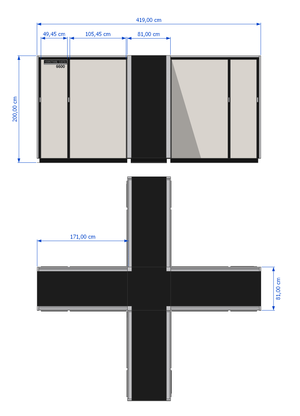

El CDC 6600 utilizaba un procesador central simplificado (CP) que estaba diseñado para ejecutar operaciones matemáticas y lógicas lo más rápido posible, lo que exigía que se construyera lo más pequeño posible para reducir la longitud del cableado y los retrasos de señalización asociados. Esto llevó al chasis principal de la máquina (normalmente) en forma de cruz con las placas de circuito para la CPU dispuestas cerca del centro, lo que dio como resultado una CPU mucho más pequeña. Combinado con las velocidades de conmutación más rápidas de los transistores de silicio, la nueva CPU funcionaba a 10 MHz (tiempo de ciclo de 100 ns), aproximadamente diez veces más rápido que otras máquinas del mercado. Además de que el reloj era más rápido, el procesador simple ejecutaba instrucciones en menos ciclos de reloj; por ejemplo, la CPU podía completar una multiplicación en diez ciclos.

Para respaldar a la CPU había diez procesadores periféricos (PP) de 12 bits y 4 KiB, cada uno con acceso a un conjunto común de 12 canales de entrada/salida (E/S) , que manejaban la entrada y la salida, así como también controlaban qué datos se enviaban a la memoria central para su procesamiento por parte del CP. Los PP fueron diseñados para acceder a la memoria durante los momentos en que la CPU estaba ocupada realizando operaciones. Esto les permitía realizar la entrada/salida esencialmente de forma gratuita en términos de tiempo de procesamiento central, manteniendo a la CPU ocupada tanto como fuera posible.

El CP del 6600 utilizaba una palabra de 60 bits y una representación de complemento a uno de números enteros, algo que las máquinas CDC posteriores utilizarían hasta fines de la década de 1980, lo que las convirtió en los últimos sistemas, además de algunos procesadores de señales digitales, en utilizar esta arquitectura. [26]

Más tarde, [¿ cuándo? ] CDC ofreció opciones en cuanto al número y tipo de CP, PP y canales, por ejemplo, el CDC 6700 tenía dos procesadores centrales, un CP 6400 y un CP 6600.

Mientras que otras máquinas de su época tenían paneles frontales elaborados para controlarlas, el 6600 solo tiene un panel de inicio muerto . [27] Hay una consola de sistema CRT dual, pero está controlada por el sistema operativo y no controla ni muestra el hardware directamente.

La máquina 6600 completa contenía aproximadamente 400.000 transistores. [28]

La CPU solo podía ejecutar un número limitado de instrucciones simples. Una CPU típica de la época tenía un conjunto de instrucciones complejo , que incluía instrucciones para manejar todas las tareas normales de "mantenimiento", como el acceso a la memoria y la entrada/salida . Cray, en cambio, implementó estas instrucciones en procesadores separados y más simples dedicados exclusivamente a estas tareas, dejando a la CPU con un conjunto de instrucciones mucho más pequeño. Este fue el primero de lo que más tarde se denominaría diseño de computadora con conjunto de instrucciones reducido (RISC).

Al permitir que la CPU, los procesadores periféricos (PP) y la E/S funcionaran en paralelo, el diseño mejoró considerablemente el rendimiento de la máquina. En condiciones normales, una máquina con varios procesadores también costaría mucho más. La clave del diseño del 6600 era hacer que los procesadores de E/S, conocidos como procesadores periféricos (PP), fueran lo más simples posible. Los PP se basaban en el sencillo CDC 160-A de 12 bits , que funcionaba mucho más lento que la CPU, recopilando datos y transmitiéndolos como ráfagas a la memoria principal a alta velocidad a través de hardware dedicado.

Los 10 PP se implementaron virtualmente; solo había hardware de CPU para un solo PP. [29] : pp.4-3 a 4-4 Este hardware de CPU era compartido y operaba en 10 conjuntos de registros PP que representaban cada uno de los 10 estados PP (similar a los procesadores multihilo modernos ). El barril de registros PP "rotaría", con cada conjunto de registros PP presentado en la "ranura" que ocupaba la CPU PP real. La CPU compartida ejecutaría toda o parte de la instrucción de un PP, con lo cual el barril "rotaría" nuevamente, presentando el conjunto de registros (estado) del siguiente PP. Se necesitaban múltiples "rotaciones" del barril para completar una instrucción. Una "rotación" completa del barril ocurría en 1000 nanosegundos (100 nanosegundos por PP), y una instrucción podía tomar de una a cinco "rotaciones" del barril para completarse, o más si era una instrucción de transferencia de datos.

La base de la CPU 6600 es lo que más tarde se llamaría un sistema RISC , [ disputado (por: instrucciones de longitud variable) – discutir ] uno en el que el procesador está ajustado para realizar instrucciones que son comparativamente simples y tienen un acceso limitado y bien definido a la memoria. La filosofía de muchas otras máquinas era hacia el uso de instrucciones que eran complicadas, por ejemplo, una sola instrucción que buscaría un operando de la memoria y lo agregaría a un valor en un registro. En el 6600, cargar el valor de la memoria requeriría una instrucción, y agregarlo requeriría una segunda. Si bien en teoría era más lento debido a los accesos adicionales a la memoria, el hecho de que en un código bien programado, se pudieran procesar múltiples instrucciones en paralelo alivió este gasto. Esta simplificación también obligó a los programadores a ser muy conscientes de sus accesos a la memoria y, por lo tanto, a codificar deliberadamente para reducirlos tanto como fuera posible. [ cita requerida ] El CDC 6600 CP, al ser una máquina de tres direcciones, permite la especificación de los tres operandos. [30]

La serie CDC 6000 incluía cuatro modelos básicos, el CDC 6400 , el CDC 6500 , el CDC 6600 y el CDC 6700. [ ¿cuándo? ] Los modelos de la serie 6000 se diferenciaban solo en sus CPU, que eran de dos tipos, la CPU 6400 y la CPU 6600. La CPU 6400 tenía una unidad aritmética unificada, en lugar de unidades funcionales discretas . Como tal, no podía superponer los tiempos de ejecución de las instrucciones. Por ejemplo, en una CPU 6400, si una instrucción de suma seguía inmediatamente a una instrucción de multiplicación, la instrucción de suma no podía iniciarse hasta que la instrucción de multiplicación terminara, por lo que el tiempo de ejecución neto de las dos instrucciones sería la suma de sus tiempos de ejecución individuales. La CPU 6600 tenía múltiples unidades funcionales que podían operar simultáneamente, es decir , "en paralelo ", lo que permitía a la CPU superponer los tiempos de ejecución de las instrucciones. Por ejemplo, una CPU 6600 podría comenzar a ejecutar una instrucción de suma en el siguiente ciclo de CPU después del comienzo de una instrucción de multiplicación (asumiendo, por supuesto, que el resultado de la instrucción de multiplicación no era un operando de la instrucción de suma), por lo que el tiempo de ejecución neto de las dos instrucciones sería simplemente el tiempo de ejecución (más largo) de la instrucción de multiplicación. La CPU 6600 también tenía una pila de instrucciones , una especie de caché de instrucciones , que ayudaba a aumentar el rendimiento de la CPU al reducir la cantidad de tiempo de inactividad de la CPU causado por esperar a que la memoria responda a las solicitudes de obtención de instrucciones. Los dos tipos de CPU eran compatibles con las instrucciones, de modo que un programa que se ejecutara en cualquiera de los tipos de CPU se ejecutaría de la misma manera en el otro tipo, pero se ejecutaría más rápido en la CPU 6600. De hecho, todos los modelos de la serie 6000 eran completamente compatibles entre sí. El CDC 6400 tenía una CPU (una CPU 6400), el CDC 6500 tenía dos CPU (ambas CPU 6400), el CDC 6600 tenía una CPU (una CPU 6600) y el CDC 6700 tenía dos CPU (una CPU 6600 y una CPU 6400).

El procesador central (CP) y la memoria principal de las máquinas 6400, 6500 y 6600 tenían una longitud de palabra de 60 bits. El procesador central tenía ocho registros de propósito general de 60 bits X0 a X7, ocho registros de dirección de 18 bits A0 a A7 y ocho registros de "incremento" de 18 bits B0 a B7. B0 se mantenía en cero de forma permanente por el hardware. Muchos programadores encontraron útil establecer B1 en 1 y tratarlo de manera similar como inviolable.

El CP no tenía instrucciones para la entrada y salida, que se llevan a cabo a través de procesadores periféricos (abajo). No había códigos de operación específicamente dedicados a cargar o almacenar memoria; esto ocurrió como un efecto secundario de la asignación a ciertos registros A. La configuración de A1 a A5 cargaba la palabra en esa dirección en X1 a X5 respectivamente; la configuración de A6 o A7 almacenaba una palabra de X6 o X7. No hubo efectos secundarios asociados con A0. Una unidad de carga/almacenamiento de hardware separada, llamada stunt box , manejaba el movimiento de datos real independientemente de la operación del flujo de instrucciones, lo que permitía que otras operaciones se completaran mientras se accedía a la memoria, lo que requería ocho ciclos, en el mejor de los casos.

El 6600 CP incluía diez unidades funcionales paralelas, lo que permitía trabajar con varias instrucciones al mismo tiempo. Hoy en día, [ ¿período de tiempo? ] esto se conoce como un diseño de procesador superescalar , pero era único en su época. A diferencia de la mayoría de los diseños de CPU modernos, las unidades funcionales no estaban segmentadas; la unidad funcional se ponía ocupada cuando se le "enviaba" una instrucción y permanecía ocupada durante todo el tiempo necesario para ejecutar esa instrucción. (Por el contrario, el CDC 7600 introdujo la segmentación en sus unidades funcionales). En el mejor de los casos, se podía enviar una instrucción a una unidad funcional cada ciclo de reloj de 100 ns. El sistema leía y decodificaba instrucciones de la memoria lo más rápido posible, generalmente más rápido de lo que podían completarse, y las enviaba a las unidades para su procesamiento. Las unidades eran:

Las operaciones de punto flotante ocuparon un lugar destacado en esta arquitectura : el CDC 6600 (y sus similares) son prácticamente los únicos capaces de ejecutar una multiplicación de punto flotante de 60 bits en un tiempo comparable al de una rama de programa. Un análisis reciente realizado por Mitch Alsup del libro de James Thornton, "Design of a Computer", reveló que la unidad de punto flotante del 6600 es un diseño segmentado de dos etapas.

La suma y resta de números de 60 bits en coma fija se manejaba en la unidad de suma larga, utilizando el complemento a uno para los números negativos. La multiplicación en coma fija se hacía como un caso especial en la unidad de multiplicación en coma flotante: si el exponente era cero, la unidad FP hacía una multiplicación en coma flotante de 48 bits de precisión simple y borraba la parte del exponente alto, lo que daba como resultado un entero de 48 bits. La división de enteros se realizaba mediante una macro, convirtiendo a y desde coma flotante. [31]

Las instrucciones ejecutadas previamente se guardaban en una caché de ocho palabras , llamada "pila". Los saltos dentro de la pila eran más rápidos que los saltos fuera de la pila porque no se requería recuperación de memoria. La pila se vaciaba mediante una instrucción de salto incondicional, por lo que los saltos incondicionales al final de los bucles se escribían convencionalmente como saltos condicionales que siempre se ejecutarían correctamente.

El sistema utilizaba un reloj de 10 MHz , con una señal de cuatro fases . Una multiplicación de punto flotante tardaba diez ciclos, una división tardaba 29 y el rendimiento general, teniendo en cuenta los retrasos de memoria y otros problemas, era de unos 3 MFLOPS . Utilizando los mejores compiladores disponibles, en los últimos años de la historia de la máquina, los programas FORTRAN podían esperar mantener unos 0,5 MFLOPS.

Los programas de usuario están restringidos a utilizar sólo un área contigua de la memoria principal. La porción de memoria a la que tiene acceso un programa en ejecución está controlada por los registros RA (Dirección relativa) y FL (Longitud de campo) que no son accesibles al programa de usuario. Cuando un programa de usuario intenta leer o escribir una palabra en la memoria central en la dirección a , el procesador primero verificará que a esté entre 0 y FL-1. Si es así, el procesador accede a la palabra en la memoria central en la dirección RA+a. Este proceso se conoce como reubicación de límite de base ; cada programa de usuario ve la memoria central como un bloque de palabras contiguos con longitud FL, comenzando con la dirección 0; de hecho, el programa puede estar en cualquier parte de la memoria física. Usando esta técnica, cada programa de usuario puede ser movido ("reubicado") en la memoria principal por el sistema operativo, siempre y cuando el registro RA refleje su posición en la memoria. Un programa de usuario que intenta acceder a la memoria fuera del rango permitido (es decir, con una dirección que no sea menor que FL) activará una interrupción y será finalizado por el sistema operativo. Cuando esto sucede, el sistema operativo puede crear un volcado de memoria que registra el contenido de la memoria del programa y lo registra en un archivo, lo que permite al desarrollador del programa saber qué sucedió. Nótese la distinción con los sistemas de memoria virtual ; en este caso, la totalidad del espacio direccionable de un proceso debe estar en la memoria central, debe ser contiguo y su tamaño no puede ser mayor que la capacidad de memoria real.

Todas las máquinas de la serie CDC 6000, excepto las siete primeras, podían configurarse con un sistema de almacenamiento de núcleo extendido (ECS) opcional. El ECS se construía a partir de una variedad diferente de memoria de núcleo que la utilizada en la memoria central. Esta memoria era más lenta, pero lo suficientemente barata como para que pudiera ser mucho más grande. La razón principal era que la memoria ECS estaba cableada con solo dos cables por núcleo (en contraste con los cinco de la memoria central). Debido a que realizaba transferencias muy amplias, su tasa de transferencia secuencial era la misma que la de la memoria de núcleo pequeño. Una CPU 6000 podía realizar directamente transferencias de memoria de bloque entre el programa de un usuario (o sistema operativo) y la unidad ECS. Se utilizaban rutas de datos amplias, por lo que esta era una operación muy rápida. Los límites de memoria se mantenían de manera similar a la memoria central, con un mecanismo RA/FL mantenido por el sistema operativo. El ECS se podía utilizar para una variedad de propósitos, incluyendo contener matrices de datos de usuario que eran demasiado grandes para la memoria central, almacenar archivos de uso frecuente, intercambiar e incluso como una ruta de comunicación en un complejo de múltiples mainframes.

Para manejar las tareas de "mantenimiento", que en otros diseños se asignaban a la CPU, Cray incluyó otros diez procesadores, basados en parte en su computadora anterior [ ¿cuándo? ] , la CDC 160-A. Estas máquinas, llamadas Procesadores Periféricos, o PP, eran computadoras completas por derecho propio, pero estaban ajustadas para realizar tareas de E/S y ejecutar el sistema operativo. (Partes sustanciales del sistema operativo se ejecutaban en los PP; por lo tanto, dejaban la mayor parte de la potencia del Procesador Central disponible para los programas de usuario). Solo los PP tenían acceso a los canales de E/S . Uno de los PP (PP0) tenía el control general de la máquina, incluido el control del programa que se ejecutaba en la CPU principal, mientras que los otros se dedicaban a varias tareas de E/S; PP9 estaba dedicado a la consola del sistema. Cuando el programa CP necesitaba realizar una función del sistema operativo, ponía una solicitud en una ubicación conocida ( Dirección de referencia + 1) monitoreada [32] por PP0. Si era necesario, PP0 asignaba otro PP para cargar cualquier código necesario y manejar la solicitud. Luego, el PP borraría RA+1 para informar al programa CP que la tarea estaba completa.

El papel único del PP0 en el control de la máquina era un potencial punto único de falla, ya que un mal funcionamiento aquí podría apagar toda la máquina, incluso si los otros nueve PP y la CPU seguían funcionando correctamente. Cray solucionó esto en el diseño del sucesor 7600, cuando cualquiera de los PP podía ser el controlador y la CPU podía reasignar a cualquiera a esta función. [ ¿cuándo? ]

Cada PP incluía su propia memoria de 4096 palabras de 12 bits . Esta memoria servía tanto para el almacenamiento en búfer de E/S como para el almacenamiento de programas, pero las unidades de ejecución eran compartidas por diez PP, en una configuración llamada Barrel and slot . Esto significaba que las unidades de ejecución (el "slot") ejecutarían un ciclo de instrucción del primer PP, luego un ciclo de instrucción del segundo PP, etc. en forma de round robin. Esto se hizo tanto para reducir costos como porque el acceso a la memoria del CP requería 10 ciclos de reloj del PP: cuando un PP accede a la memoria del CP, los datos están disponibles la próxima vez que el PP recibe su tiempo de slot.

Además de un conjunto de instrucciones convencionales, los PP tienen varias instrucciones diseñadas específicamente para comunicarse con el procesador central. [33] : pp.4-24–4-27

CRD d- transfiere una palabra de 60 bits desde la memoria central en la dirección especificada por el registro PP A a cinco palabras PP consecutivas comenzando en la dirección d .CRM d,m- similar a CRD, pero transfiere un bloque de palabras cuya longitud fue almacenada previamente en la ubicación d a la memoria PP comenzando en la dirección PP m .CWD d- reúne cinco palabras PP consecutivas comenzando en la ubicación d y las transfiere a la ubicación de memoria central especificada por el registro A.CWM d,m- transfiere un bloque que comienza en la dirección de memoria PP m a la memoria central. La dirección de memoria central se almacenó en el registro A y la longitud se almacenó en la ubicación d antes de la ejecución.RPN- transfiere el contenido del registro de dirección del programa del procesador central al registro A del PP .EXN- El salto de intercambio transmite una dirección desde el registro A y le indica al procesador que realice un salto de intercambio utilizando la dirección especificada. El salto de intercambio CP interrumpe al procesador, carga sus registros desde la ubicación especificada y almacena el contenido anterior en la misma ubicación. Esto realiza un cambio de tarea. [33] : pp.3-9–3-10 El procesador central tiene palabras de 60 bits , mientras que los procesadores periféricos tienen palabras de 12 bits . CDC utilizó el término "byte" para referirse a las entidades de 12 bits utilizadas por los procesadores periféricos; los caracteres son de 6 bits y las instrucciones del procesador central son de 15 bits o de 30 bits con un campo de dirección de 18 bits con signo, lo que permite un espacio de memoria directamente direccionable de 128 000 palabras de memoria central (convertido a términos modernos, con bytes de 8 bits, esto es poco menos de 1 MB). La naturaleza firmada de los registros de dirección limita un programa individual a 128 000 palabras. (Las máquinas posteriores compatibles con CDC 6000 podían tener 256 000 palabras o más de memoria central, si el presupuesto lo permitía, pero los programas de usuario individuales todavía estaban limitados a 128 000 palabras de memoria central). Las instrucciones del procesador central comienzan en un límite de palabras cuando son el objetivo de una instrucción de salto o de una instrucción de salto de retorno de subrutina, por lo que a veces se requieren instrucciones no-op para completar los últimos 15, 30 o 45 bits de una palabra. Los programadores de ensamblador experimentados podían afinar sus programas llenando estos espacios no-op con instrucciones misceláneas que serían necesarias más adelante en el programa.

Los caracteres de 6 bits , en una codificación llamada código de visualización CDC , [34] [35] [36] se podían usar para almacenar hasta 10 caracteres en una palabra. Permitían un conjunto de caracteres de 64 caracteres, lo cual es suficiente para todas las letras mayúsculas, dígitos y algo de puntuación. Ciertamente era suficiente para escribir FORTRAN o imprimir informes financieros o científicos. En realidad, había dos variaciones de los conjuntos de caracteres del código de visualización CDC en uso: 64 caracteres y 63 caracteres. El conjunto de 64 caracteres tenía la desventaja de que el carácter ":" (dos puntos) se ignoraría (se interpretaría como relleno de ceros) si fuera el último carácter de una palabra. Una variante complementaria, llamada código de visualización 6/12 , también se usó en los sistemas de tiempo compartido Kronos y NOS para permitir el uso completo del conjunto de caracteres ASCII de una manera algo compatible con el software más antiguo. [37]

Sin instrucciones de direccionamiento de bytes, era necesario escribir código para empaquetar y convertir caracteres en palabras. El gran tamaño de las palabras y la cantidad comparativamente pequeña de memoria implicaban que los programadores solían economizar memoria empaquetando datos en palabras a nivel de bits.

Debido al gran tamaño de las palabras y a que cada una tiene 10 caracteres, a menudo era más rápido procesar una palabra entera de caracteres a la vez que descomprimirlos, procesarlos y volver a empaquetarlos. Por ejemplo, el compilador COBOL de CDC era bastante bueno en el procesamiento de campos decimales utilizando esta técnica. Este tipo de técnicas se utilizan ahora [ ¿cuándo? ] con frecuencia en las instrucciones "multimedia" de los procesadores actuales.

La máquina se construyó en un gabinete con forma de signo más con una bomba y un intercambiador de calor en los 46 cm (18 pulgadas) más externos de cada uno de los cuatro brazos. La refrigeración se realizó con freón que circulaba dentro de la máquina e intercambiaba calor con un suministro externo de agua fría. Cada brazo podía sostener cuatro chasis, cada uno de aproximadamente 20 cm (8 pulgadas) de espesor, con bisagras cerca del centro y que se abrían un poco como un libro. La intersección del "más" estaba llena de cables que interconectaban el chasis. Los chasis estaban numerados del 1 (que contenía las 10 PPU y sus memorias, así como los 12 canales de E/S bastante mínimos) al 16. La memoria principal para la CPU estaba distribuida en muchos de los chasis. En un sistema con solo 64K palabras de memoria principal, se omitió uno de los brazos del "más".

La lógica de la máquina estaba empaquetada en módulos de aproximadamente 2,5 pulgadas (64 mm) de lado y aproximadamente 1 pulgada (2,5 cm) de espesor. Cada módulo tenía un conector (30 pines, dos filas verticales de 15) en un borde y seis puntos de prueba en el borde opuesto. El módulo se colocaba entre dos placas frías de aluminio para eliminar el calor. El módulo consistía en dos placas de circuito impreso paralelas, con componentes montados en una de las placas o entre las dos placas. Esto proporcionaba un paquete muy denso; generalmente imposible de reparar, pero con buenas características de transferencia de calor. Se conocía como construcción de madera de cordón .

Hubo un punto delicado con el soporte del sistema operativo 6600 : los plazos de entrega se retrasaron. Las máquinas originalmente [ ¿cuándo? ] ejecutaban un sistema de control de tareas muy simple conocido como COS ( sistema operativo Chippewa ), que se "ensambló" rápidamente basándose en el sistema operativo CDC 3000 anterior para tener algo en funcionamiento para probar los sistemas antes de la entrega. Sin embargo, las máquinas estaban destinadas a ser entregadas con un sistema mucho más potente conocido como SIPROS (sistema operativo de procesamiento simultáneo), que se estaba desarrollando en la división de ciencias de sistemas de la empresa en Los Ángeles . Los clientes quedaron impresionados con la lista de características de SIPROS, y muchos tenían SIPROS incluido en sus contratos de entrega.

SIPROS resultó ser un fiasco total. Los plazos de desarrollo se siguieron retrasando, lo que le costó a CDC importantes cantidades de beneficios en forma de penalizaciones por retrasos en las entregas. Tras varios meses de espera con las máquinas listas para ser enviadas, el proyecto acabó cancelándose. Los programadores que habían trabajado en COS tenían poca fe en SIPROS y habían seguido trabajando para mejorarlo.

El desarrollo de sistemas operativos se dividió en dos bandos. La evolución de COS, aprobada por el CDC, se llevó a cabo en el laboratorio de desarrollo de software de Sunnyvale, California . Muchos clientes acabaron recibiendo sus sistemas con este software, conocido entonces como SCOPE (Supervisory Control Of Program Execution). La versión 1 de SCOPE era, en esencia, un COS desensamblado; la versión 2 de SCOPE incluía compatibilidad con nuevos dispositivos y sistemas de archivos; la versión 3 de SCOPE incluía compatibilidad con archivos permanentes, compatibilidad con lotes remotos EI/200 y compatibilidad con tiempo compartido INTERCOM . SCOPE siempre tuvo importantes problemas de fiabilidad y mantenimiento.

La evolución subterránea de COS tuvo lugar en la planta de ensamblaje de Arden Hills, Minnesota . [ ¿Cuándo? ] MACE ([Greg] Mansfield And [Dave] Cahlander Executive) fue escrito en gran parte por un solo programador en las horas de inactividad, cuando las máquinas estaban disponibles. Su conjunto de características era esencialmente el mismo que COS y SCOPE 1. Mantenía el sistema de archivos COS anterior, pero hizo avances significativos en la modularidad del código para mejorar la confiabilidad del sistema y la adaptabilidad a nuevos dispositivos de almacenamiento. MACE nunca fue un producto oficial, aunque muchos clientes pudieron conseguir una copia de CDC.

El software no oficial de MACE fue elegido más tarde en lugar del producto oficial SCOPE como base del siguiente sistema operativo CDC, Kronos , llamado así por el dios griego del tiempo . La historia cuenta [¿ cuándo? ] que Dave Mansfield llamó a la biblioteca de la Universidad de Minnesota y pidió una palabra antigua que significara "tiempo". Escribió "Kronos" en lugar de "Chronos". La principal razón de marketing para su adopción fue el desarrollo de su función de tiempo compartido TELEX y su función de lotes remotos BATCHIO. Kronos continuó utilizando el sistema de archivos COS/SCOPE 1 con la adición de una función de archivo permanente.

Un intento de unificar los productos de los sistemas operativos SCOPE y Kronos produjo NOS (Network Operating System). [ ¿Cuándo? ] NOS estaba destinado a ser el único sistema operativo para todas las máquinas CDC, un hecho que CDC promovió intensamente. Muchos clientes de SCOPE siguieron dependiendo del software de la arquitectura SCOPE, por lo que CDC simplemente lo renombró NOS/BE (Batch Environment), y pudieron afirmar que todos estaban ejecutando NOS. En la práctica, era mucho más fácil modificar la base de código de Kronos para agregar características de SCOPE que a la inversa.

El entorno de la planta de ensamblaje también produjo otros sistemas operativos que nunca estuvieron destinados al uso del cliente. [¿ cuándo? ] Estos incluían las herramientas de ingeniería SMM para pruebas de hardware y KALEIDOSCOPE, para pruebas de humo de software . Otra herramienta utilizada comúnmente por los ingenieros de campo de CDC durante las pruebas era MALET (lenguaje de aplicación de mantenimiento para pruebas de equipos), que se utilizaba para probar componentes y dispositivos después de reparaciones o mantenimiento por parte de los ingenieros. Las condiciones de prueba a menudo utilizaban paquetes de discos duros y cintas magnéticas que se marcaban deliberadamente con errores para determinar si MALET y el ingeniero los detectarían.

CDC utilizó los nombres SCOPE y COMPASS tanto para la serie CDC 6000 , incluida la 6600, como para la serie CDC 3000 :

El CDC 7600 fue originalmente [ ¿cuándo? ] pensado para ser totalmente compatible también con las máquinas de la serie 6000 existentes; comenzó su vida conociendo al CDC 6800. Pero durante su diseño, los diseñadores determinaron que mantener una compatibilidad completa con las máquinas de la serie 6000 existentes limitaría la mejora de rendimiento que podrían lograr y decidieron sacrificar la compatibilidad por el rendimiento. Mientras que la CPU del CDC 7600 era básicamente compatible en cuanto a instrucciones con las CPU 6400 y 6600, lo que permitía la portabilidad de código a nivel de código fuente de lenguaje de alto nivel , el hardware del CDC 7600, especialmente el de sus Unidades de Procesamiento Periférico (PPU), era bastante diferente, y el CDC 7600 requería un sistema operativo diferente. Esto resultó ser algo fortuito, ya que permitió a los diseñadores mejorar algunas de las características del diseño de la serie 6000, como la dependencia total de este último de los procesadores periféricos (PP), en particular el primero (llamado PP0), para controlar el funcionamiento de todo el sistema informático, incluidas las CPU. A diferencia de la CPU 6600, la CPU del CDC 7600 podía controlar su propio funcionamiento a través de una instrucción de salto de intercambio central (XJ) que intercambiaba todo el contenido de los registros con la memoria central. De hecho, las máquinas de la serie 6000 fueron modernizadas con esta capacidad.

{{cite web}}: CS1 maint: copia archivada como título ( enlace )El 6600 tenía 400.000 transistores y más de 160 kilómetros de cableado.– descripción general con imágenes