La modulación delta-sigma ( ΔΣ ; o sigma-delta , ΣΔ ) es un método de sobremuestreo para codificar señales en señales digitales de baja profundidad de bits a una frecuencia de muestreo muy alta como parte del proceso de los convertidores analógico-digitales (ADC) y digital-analógicos (DAC) delta-sigma. La modulación delta-sigma logra una alta calidad al utilizar un bucle de retroalimentación negativa durante la cuantificación a la profundidad de bits más baja que corrige continuamente los errores de cuantificación y mueve el ruido de cuantificación a frecuencias más altas muy por encima del ancho de banda de la señal original . El filtrado de paso bajo posterior para la demodulación elimina fácilmente este ruido de alta frecuencia y los promedios de tiempo para lograr una alta precisión en amplitud que finalmente se puede codificar como modulación de código de pulso (PCM).

Tanto los ADC como los DAC pueden emplear modulación delta-sigma. Un ADC delta-sigma (por ejemplo, la Figura 1 superior) codifica una señal analógica utilizando modulación delta-sigma de alta frecuencia y luego aplica un filtro digital para demodularla a una salida digital de bits altos a una frecuencia de muestreo más baja. Un DAC delta-sigma (por ejemplo, la Figura 1 inferior) codifica una señal de entrada digital de alta resolución en una señal de resolución más baja pero con una frecuencia de muestreo más alta que luego puede asignarse a voltajes y suavizarse con un filtro analógico para la demodulación. En ambos casos, el uso temporal de una señal de baja profundidad de bits a una frecuencia de muestreo más alta simplifica el diseño del circuito y aprovecha la eficiencia y la alta precisión en el tiempo de la electrónica digital .

Principalmente debido a su eficiencia de costos y complejidad de circuito reducida, esta técnica ha encontrado un uso creciente en componentes electrónicos modernos como DAC, ADC, sintetizadores de frecuencia , fuentes de alimentación de modo conmutado y controladores de motores . [1] La salida cuantificada gruesa de un ADC delta-sigma se usa ocasionalmente directamente en el procesamiento de señales o como una representación para el almacenamiento de señales (por ejemplo, Super Audio CD almacena la salida sin procesar de un modulador delta-sigma de 1 bit).

Si bien este artículo se centra en la modulación sincrónica , que requiere un reloj preciso para la cuantificación, la modulación delta-sigma asincrónica se ejecuta sin reloj.

Al transmitir una señal analógica directamente, todo el ruido del sistema y de la transmisión se suma a la señal analógica, lo que reduce su calidad. La digitalización permite una transmisión, un almacenamiento y un procesamiento sin ruido. Existen muchos métodos de digitalización.

En los ADC de tasa de Nyquist, una señal analógica se muestrea a una frecuencia de muestreo relativamente baja, justo por encima de su tasa de Nyquist (el doble de la frecuencia más alta de la señal) y se cuantifica mediante un cuantificador multinivel para producir una señal digital de múltiples bits . Estos métodos de bits más altos buscan precisión en la amplitud directamente, pero requieren componentes extremadamente precisos y, por lo tanto, pueden sufrir de una linealidad deficiente.

En cambio, los convertidores de sobremuestreo producen un resultado de menor profundidad de bits a una frecuencia de muestreo mucho más alta. Esto permite lograr una calidad comparable aprovechando:

Otro aspecto clave que proporciona el sobremuestreo es el equilibrio entre frecuencia y resolución. El filtro de diezmado colocado después del modulador no solo filtra toda la señal muestreada en la banda de interés (reduciendo el ruido en frecuencias más altas), sino que también reduce la frecuencia de muestreo y, por lo tanto, el rango de frecuencia representable de la señal, al tiempo que aumenta la resolución de amplitud de la muestra. Esta mejora en la resolución de amplitud se obtiene mediante una especie de promediado del flujo de bits de mayor velocidad de datos.

La modulación delta es un método de sobremuestreo de bits bajos relacionado anteriormente que también utiliza retroalimentación negativa , pero solo codifica la derivada de la señal (su delta ) en lugar de su amplitud . El resultado es una secuencia de marcas y espacios que representan hacia arriba o hacia abajo el movimiento de la señal, que debe integrarse para reconstruir la amplitud de la señal. La modulación delta tiene varias desventajas. La diferenciación altera el espectro de la señal amplificando el ruido de alta frecuencia, atenuando las frecuencias bajas [2] y eliminando el componente de CC . Esto hace que su rango dinámico y su relación señal-ruido sean inversamente proporcionales a la frecuencia de la señal. La modulación delta sufre una sobrecarga de pendiente si las señales se mueven demasiado rápido y es susceptible a perturbaciones de transmisión que resultan en un error acumulativo .

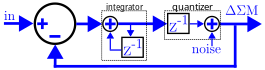

La modulación delta-sigma reorganiza el integrador y el cuantificador de un modulador delta, de modo que la salida lleva información correspondiente a la amplitud de la señal de entrada en lugar de solo su derivada. [3] Esto también tiene el beneficio de incorporar una modelación de ruido deseable en el proceso de conversión, para mover deliberadamente el ruido de cuantificación a frecuencias más altas que la señal. Dado que la señal de error acumulada es filtrada por paso bajo por el integrador del modulador delta-sigma antes de ser cuantificada, la retroalimentación negativa posterior de su resultado cuantificado resta efectivamente los componentes de baja frecuencia del ruido de cuantificación mientras deja los componentes de frecuencia más alta del ruido.

En el caso específico de un ADC ΔΣ sincrónico de un solo bit, una señal de voltaje analógica se convierte efectivamente en una frecuencia de pulso, o densidad de pulso, que puede entenderse como modulación de densidad de pulso (PDM). Una secuencia de pulsos positivos y negativos, que representan bits a una tasa fija conocida, es muy fácil de generar, transmitir y regenerar con precisión en el receptor, siempre que se pueda recuperar la sincronización y el signo de los pulsos. Dada una secuencia de pulsos de este tipo de un modulador delta-sigma, la forma de onda original se puede reconstruir con la precisión adecuada.

El uso de PDM como representación de señal es una alternativa a PCM. Alternativamente, el PDM de alta frecuencia puede ser posteriormente muestreado a menor frecuencia mediante un proceso llamado decimación y recuantificado para convertirlo en un código PCM de múltiples bits a una frecuencia de muestreo más baja, más cercana a la tasa de Nyquist de la banda de frecuencia de interés.

El artículo seminal [4] que combina la retroalimentación con el sobremuestreo para lograr la modulación delta fue escrito por F. de Jager de Philips Research Laboratories en 1952. [5]

El principio de mejorar la resolución de un cuantificador grueso mediante el uso de retroalimentación, que es el principio básico de la conversión delta-sigma, fue descrito por primera vez en una patente presentada en 1954 por C. Chapin Cutler de Bell Labs . [6] No fue nombrado como tal hasta un artículo de 1962 [7] por Inose et al. de la Universidad de Tokio , que propuso la idea de agregar un filtro en la ruta de avance del modulador delta. [8] [nota 1] Sin embargo, Charles B Brahm de United Aircraft Corp [9] presentó en 1961 una patente "Sistema de integración de retroalimentación" [10] con un bucle de retroalimentación que contiene un integrador con cuantificación de múltiples bits que se muestra en su Fig. 1. [2]

En "La evolución de los convertidores analógico-digitales con sobremuestreo" [4] de Wooley se ofrece más información y se hacen referencias a patentes relevantes. Algunas de las formas de variación (que pueden aplicarse en diferentes combinaciones) son el orden del modulador, la profundidad de bits del cuantificador, la forma de diezmar y la relación de sobremuestreo.

El ruido del cuantificador se puede moldear aún más reemplazando el cuantificador mismo con otro modulador ΔΣ. Esto crea un modulador de segundo orden , que se puede reorganizar en cascada (Figura 2). [2] Este proceso se puede repetir para aumentar el orden aún más.

Si bien los moduladores de primer orden son incondicionalmente estables, se debe realizar un análisis de estabilidad para moduladores de retroalimentación de ruido de orden superior. Alternativamente, las configuraciones de retroalimentación de ruido siempre son estables y tienen un análisis más simple. [11] §6.1

El modulador también se puede clasificar por la profundidad de bits de su cuantificador. Un cuantificador que distingue entre N niveles se denomina cuantificador de bit log 2 N. Por ejemplo, un comparador simple tiene 2 niveles y, por lo tanto, es un cuantificador de 1 bit; un cuantificador de 3 niveles se denomina cuantificador de bit "1,5"; un cuantificador de 4 niveles es un cuantificador de 2 bits; un cuantificador de 5 niveles se denomina cuantificador de 2,5 bits . [12] Los cuantificadores de bits más altos producen inherentemente menos ruido de cuantificación.

Una crítica a la cuantificación de 1 bit es que no se pueden utilizar cantidades adecuadas de tramado en el bucle de retroalimentación, por lo que se puede escuchar distorsión en algunas condiciones (más discusión en Direct Stream Digital § DSD vs. PCM ). [13] [14]

La decimación está fuertemente asociada con la modulación delta-sigma, pero es distinta y está fuera del alcance de este artículo. El artículo original de 1962 no describía la decimación. Los datos sobremuestreados en los primeros días se enviaban tal cual. La propuesta de diezmar los datos delta-sigma sobremuestreados usando filtrado digital antes de convertirlos en audio PCM fue hecha por D. J. Goodman en Bell Labs en 1969, [15] para reducir la señal ΔΣ de su alta frecuencia de muestreo mientras se aumenta su profundidad de bits . La decimación se puede hacer en un chip separado en el extremo receptor del flujo de bits delta-sigma, a veces por un módulo dedicado dentro de un microcontrolador , [16] que es útil para interactuar con micrófonos MEMS PDM , [17] aunque muchos circuitos integrados ADC ΔΣ incluyen la decimación. Algunos microcontroladores incluso incorporan tanto el modulador como el decimador. [18]

Los filtros de decimación más comúnmente utilizados para los ADC ΔΣ, en orden creciente de complejidad y calidad, son:

Cuando se cuantifica una señal, la señal resultante se puede aproximar mediante la adición de ruido blanco con una intensidad aproximadamente igual en todo el espectro. En realidad, el ruido de cuantificación, por supuesto, no es independiente de la señal y esta dependencia da como resultado ciclos límite y es la fuente de tonos inactivos y ruido de patrón en los convertidores delta-sigma. Sin embargo, la adición de ruido de tramado (Figura 3) reduce dicha distorsión al hacer que el ruido de cuantificación sea más aleatorio.

Los ADC ΔΣ reducen la cantidad de este ruido en la banda base distribuyéndolo y dándole forma de modo que se encuentre principalmente en frecuencias más altas. Luego, se puede filtrar fácilmente con filtros digitales económicos, sin los circuitos analógicos de alta precisión que necesitan los ADC Nyquist.

El ruido de cuantificación en el rango de frecuencia de banda base (de DC a ) se puede reducir aumentando la relación de sobremuestreo (OSR) definida por

donde es la frecuencia de muestreo y es la tasa de Nyquist (la tasa de muestreo mínima necesaria para evitar el aliasing, que es el doble de la frecuencia máxima de la señal original ). Dado que el sobremuestreo se realiza normalmente en potencias de dos, representa cuántas veces se duplica el OSR.

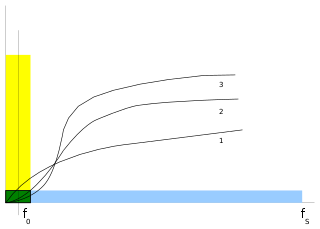

Como se ilustra en la Figura 4, la cantidad total de ruido de cuantificación es la misma tanto en un convertidor Nyquist (áreas amarillas + verdes) como en un convertidor de sobremuestreo (áreas azules + verdes). Pero los convertidores de sobremuestreo distribuyen ese ruido en un rango de frecuencia mucho más amplio. La ventaja es que la cantidad total de ruido en la banda de frecuencia de interés es drásticamente menor para los convertidores de sobremuestreo (solo el área verde pequeña) que para un convertidor Nyquist (área total amarilla + verde).

La figura 4 muestra cómo la modulación ΔΣ moldea el ruido para reducir aún más la cantidad de ruido de cuantificación en la banda base a cambio de aumentar el ruido en frecuencias más altas (donde se puede filtrar fácilmente). Las curvas de los moduladores ΔΣ de orden superior logran una reducción aún mayor del ruido en la banda base.

Estas curvas se derivan utilizando herramientas matemáticas llamadas transformada de Laplace (para señales de tiempo continuo , por ejemplo, en el bucle de modulación de un ADC) o transformada Z (para señales de tiempo discreto , por ejemplo, en el bucle de modulación de un DAC). Estas transformadas son útiles para convertir matemáticas más difíciles del dominio del tiempo en matemáticas más simples en el dominio de frecuencia complejo de la variable compleja (en el dominio de Laplace) o (en el dominio z).

La figura 5 representa el bucle de modulación ADC ΔΣ de primer orden (de la figura 1) como un sistema lineal invariante en el tiempo de tiempo continuo en el dominio de Laplace con la ecuación:

La transformada de Laplace de integración de una función del tiempo corresponde simplemente a la multiplicación por en notación de Laplace. Se supone que el integrador es un integrador ideal para simplificar las matemáticas, pero un integrador real (o un filtro similar) puede tener una expresión más complicada.

El proceso de cuantificación se aproxima a una adición con una fuente de ruido de error de cuantificación. A menudo se supone que el ruido es blanco e independiente de la señal, aunque, como explica el apartado sobre cuantificación (procesamiento de señales) § Modelo de ruido aditivo , esto no siempre es una suposición válida (en particular para la cuantificación de bits bajos).

Dado que el sistema y la transformada de Laplace son lineales, el comportamiento total de este sistema se puede analizar separando cómo afecta la entrada de cómo afecta el ruido: [11] §6

Para entender cómo el sistema afecta únicamente a la señal de entrada, imaginamos temporalmente que el ruido es 0:

que puede reorganizarse para producir la siguiente función de transferencia :

Esta función de transferencia tiene un solo polo en el plano complejo , por lo que actúa efectivamente como un filtro de paso bajo de primer orden en la señal de entrada. (Nota: su frecuencia de corte se puede ajustar como se desee incluyendo la multiplicación por una constante en el bucle).

Para entender cómo el sistema afecta únicamente al ruido, imaginamos temporalmente que la entrada es 0:

que puede reorganizarse para producir la siguiente función de transferencia:

Esta función de transferencia tiene un solo cero en y un solo polo en por lo que el sistema actúa efectivamente como un filtro de paso alto en el ruido que comienza en 0 en DC , luego aumenta gradualmente hasta alcanzar la frecuencia de corte y luego se nivela.

Mientras tanto, el bucle de modulación del DAC ΔΣ sincrónico (Figura 6) está en tiempo discreto y, por lo tanto, su análisis está en el dominio z. Es muy similar al análisis anterior en el dominio de Laplace y produce curvas similares. Nota: muchas fuentes [11] §6.1 [25] [26] también analizan el bucle de modulación de un ADC ΔΣ en el dominio z, que trata implícitamente la entrada analógica continua como una señal de tiempo discreto. Esta puede ser una aproximación válida siempre que la señal de entrada ya esté limitada en banda y se pueda suponer que no cambia en escalas de tiempo superiores a la frecuencia de muestreo. Es particularmente apropiado cuando el modulador se implementa como un circuito de condensador conmutado , que funciona transfiriendo carga entre condensadores en pasos de tiempo sincronizados.

La integración en tiempo discreto puede ser un acumulador que suma repetidamente su entrada con el resultado anterior de su suma. Esto se representa en el dominio z al realimentar la salida de un nodo sumador a través de una etapa de retardo de 1 ciclo de reloj (anotada como ) en otra entrada del nodo sumador, lo que produce . Su función de transferencia se utiliza a menudo para etiquetar integradores en diagramas de bloques.

En un DAC ΔΣ, el cuantificador puede denominarse recuantificador o convertidor digital a digital (DDC), porque su entrada ya es digital y está cuantificada, pero simplemente está reduciendo de una señal digital de mayor profundidad de bits a una de menor profundidad de bits. Esto se representa en el dominio z mediante otra etapa de retardo en serie con la adición de ruido de cuantificación. (Nota: algunas fuentes pueden haber intercambiado el orden de las etapas de ruido aditivo y de cuantificación).

La ecuación del dominio z del modulador, organizada como en la Figura 6, es: que se puede reorganizar para expresar la salida en términos de la entrada y el ruido: La entrada simplemente sale del sistema con un retraso de un ciclo de reloj. La multiplicación del término de ruido por representa un filtro inverso de primera diferencia (que tiene un solo polo en el origen y un solo cero en ) y, por lo tanto, filtra el ruido con un filtro paso alto.

Sin entrar en detalles matemáticos, [25] (ecuaciones 8-11) los integradores en cascada para crear un modulador de orden α dan como resultado: Dado que este filtro de primera diferencia hacia atrás ahora se eleva a la potencia , tendrá una curva de modelado de ruido más pronunciada, para propiedades mejoradas de mayor atenuación en la banda base, por lo que una porción dramáticamente más grande del ruido está por encima de la banda base y se puede filtrar fácilmente con un filtro de paso bajo ideal.

La relación señal-ruido (SNR) teórica en decibeles (dB) para una entrada sinusoidal que viaja a través de un modulador de orden con un OSR (y seguido por un filtro decimador de paso bajo ideal) se puede derivar matemáticamente para ser aproximadamente: [25] (ecuaciones 12-21)

De esta manera, la resolución teórica del número efectivo de bits (ENOB) mejora en bits al duplicar el OSR (incrementando ), y en bits al incrementar el orden. A modo de comparación, el sobremuestreo de un ADC Nyquist (sin ninguna modelación de ruido) solo mejora su ENOB en bits por cada duplicación del OSR, [27] que es solo 1 ⁄ 3 de la tasa de crecimiento de ENOB de un ΔΣM de primer orden.

Estos puntos de datos son teóricos. En la práctica, los circuitos inevitablemente experimentan otras fuentes de ruido que limitan la resolución, lo que hace que las celdas de mayor resolución sean poco prácticas.

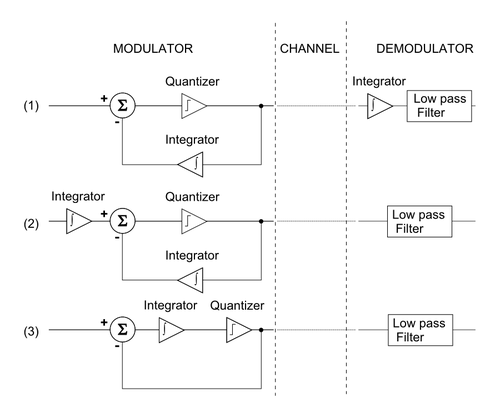

La modulación delta-sigma está relacionada con la modulación delta mediante los siguientes pasos (Figura 7): [11] §6

Si la cuantificación fuera homogénea (por ejemplo, si fuera lineal ), lo anterior sería una derivación suficiente de su equivalencia hipotética. Pero como el cuantificador no es homogéneo, delta-sigma se inspira en la modulación delta, pero ambos funcionan de forma distinta.

Del primer diagrama de bloques de la Figura 7, el integrador en la ruta de retroalimentación se puede eliminar si la retroalimentación se toma directamente de la entrada del filtro de paso bajo. Por lo tanto, para la modulación delta de la señal de entrada v en , el filtro de paso bajo ve la señal

Sin embargo, la modulación delta-sigma de la misma señal de entrada se coloca en el filtro de paso bajo.

En otras palabras, realizar una modulación delta-sigma en lugar de una modulación delta ha intercambiado de manera efectiva el orden de las operaciones del integrador y del cuantificador. El efecto neto es una implementación más simple que tiene el beneficio adicional de moldear el ruido de cuantificación para que se encuentre principalmente en frecuencias por encima de las señales de interés. Este efecto se vuelve más dramático con un mayor sobremuestreo , lo que permite que el ruido de cuantificación sea algo programable. Por otro lado, la modulación delta moldea tanto el ruido como la señal por igual.

Además, el cuantificador (por ejemplo, el comparador ) utilizado en la modulación delta tiene una salida pequeña que representa un pequeño paso hacia arriba y hacia abajo en la aproximación cuantificada de la entrada, mientras que el cuantificador utilizado en delta-sigma debe tomar valores fuera del rango de la señal de entrada.

En general, delta-sigma tiene algunas ventajas frente a la modulación delta:

Los conversores analógicos delta-sigma varían en complejidad. El circuito que se muestra a continuación se centra en un conversor analógico delta-sigma sincrónico de cuantificación de dos niveles y primer orden simple sin diezmado.

Para facilitar la comprensión, se simula un circuito esquemático simple (Figura 8a) que utiliza elementos ideales (voltajes en la Figura 8b). Funcionalmente, es el mismo bucle de modulación de analógico a digital ΔΣ de la Figura 1 (nota: el integrador inversor de 2 entradas combina la unión sumadora y el integrador y produce un resultado de retroalimentación negativa, y el flip-flop combina el cuantificador muestreado y, naturalmente, funciona también como un DAC de 1 bit).

La onda sinusoidal de entrada de 20 kHz s(t) se convierte en un resultado digital PDM de 1 bit Q(t) . Se utilizan 20 kHz como ejemplo porque se considera el límite superior de la audición humana .

Este circuito se puede diseñar en una placa de pruebas con componentes discretos económicos (tenga en cuenta que algunas variaciones utilizan polarizaciones diferentes y usan filtros de paso bajo RC más simples para la integración en lugar de amplificadores operacionales ). [28] [29]

Para simplificar, el flip-flop D está alimentado por voltajes de suministro duales de V DD = +1 V y V SS = -1 V, por lo que su salida binaria Q(t) es +1 V o -1 V.

El integrador de amplificador operacional inversor de 2 entradas combina s(t) con Q(t) para producir Ɛ(t) : Se utiliza la letra griega épsilon porque Ɛ(t) contiene el error acumulado que se corrige repetidamente mediante el mecanismo de retroalimentación. Mientras que sus dos entradas s(t) y Q(t) varían entre -1 y 1 voltio, Ɛ(t) en cambio solo varía en un par de milivoltios , aproximadamente 0 V.

Debido al signo negativo del integrador , cuando Ɛ(t) se muestrea a continuación para producir Q(t) , el + Q(t) en esta integral en realidad representa una retroalimentación negativa del ciclo de reloj anterior.

Un flip-flop D ideal muestrea Ɛ(t) a una frecuencia de reloj de 1 MHz . La vista de osciloscopio (Figura 8b) tiene una división menor igual al período de muestreo de 1 μs, por lo que cada división menor corresponde a un evento de muestreo. Dado que se supone que el flip-flop es ideal, trata cualquier voltaje de entrada mayor que 0 V como alto lógico y cualquier voltaje de entrada menor que 0 V como bajo lógico, sin importar qué tan cerca esté de 0 V (ignorando problemas de violaciones del tiempo de muestreo y retención y metaestabilidad ).

Siempre que se produzca un evento de muestreo:

Q(t) se envía como salida PDM resultante y también se devuelve al integrador inversor de 2 entradas.

El integrador situado más a la derecha realiza una conversión de digital a analógico en Q(t) para producir una salida analógica demodulada r(t) , que reconstruye la entrada de onda sinusoidal original como segmentos diagonales lineales por partes. Aunque r(t) parece burdo a esta frecuencia de sobremuestreo de 50x, r(t) se puede filtrar con un filtro de paso bajo para aislar la señal original. A medida que aumenta la frecuencia de muestreo en relación con la frecuencia máxima de la señal de entrada, r(t) se aproximará más a la entrada original s(t) .

Vale la pena señalar que si nunca se produjo una decimación, la representación digital de un modulador delta-sigma de 1 bit es simplemente una señal PDM, que se puede convertir fácilmente en analógica utilizando un filtro de paso bajo , tan simple como una resistencia y un condensador . [29]

Sin embargo, en general, un DAC delta-sigma convierte una señal de series temporales discretas de muestras digitales con una gran profundidad de bits en una señal con una profundidad de bits baja (a menudo de 1 bit), normalmente a una frecuencia de muestreo mucho mayor. Esa señal modulada en delta se puede convertir con precisión en analógica (ya que los DAC con una profundidad de bits más baja son más fáciles de convertir en altamente lineales), que luego pasa por un filtrado de paso bajo económico en el dominio analógico para eliminar el ruido de cuantificación de alta frecuencia inherente al proceso de modulación delta-sigma.

Como explican los artículos sobre la transformada de Fourier discreta y la transformada de Fourier de tiempo discreto , una señal muestreada periódicamente contiene inherentemente múltiples copias o "imágenes" de la señal con frecuencias más altas. A menudo es deseable eliminar estas imágenes de frecuencias más altas antes de realizar la etapa de modulación delta-sigma real, para facilitar los requisitos del eventual filtro de paso bajo analógico. Esto se puede hacer mediante un sobremuestreo utilizando un filtro de interpolación y, a menudo, es el primer paso antes de realizar la modulación delta-sigma en los DAC. El sobremuestreo está fuertemente asociado con los DAC delta-sigma, pero no es estrictamente parte de la etapa real de modulación delta-sigma (de manera similar a cómo la decimación está fuertemente asociada con los ADC delta-sigma, pero tampoco es estrictamente parte de la modulación delta-sigma), y los detalles están fuera del alcance de este artículo.

El bucle de modulación de la Figura 6 en § Modelado de ruido se puede diseñar fácilmente con elementos digitales básicos de un restador para la diferencia, un acumulador para el integrador y un registro de bits inferior para la cuantificación, que transporta los bits más significativos del integrador para que sean la retroalimentación para el siguiente ciclo.

Esta modulación simple de primer orden se puede mejorar conectando en cascada dos o más acumuladores de desbordamiento, cada uno de los cuales es equivalente a un modulador delta-sigma de primer orden. La estructura de modelado de ruido multietapa (MASH) [30] resultante tiene una propiedad de modelado de ruido más pronunciada , por lo que se utiliza comúnmente en audio digital. Las salidas de acarreo se combinan a través de sumas y retrasos para producir una salida binaria, cuyo ancho depende del número de etapas (orden) del MASH. Además de su función de modelado de ruido, tiene dos propiedades más atractivas:

La técnica fue presentada por primera vez a principios de la década de 1960 por el profesor Yasuhiko Yasuda mientras era estudiante en la Universidad de Tokio . [31] [11] El nombre delta-sigma proviene directamente de la presencia de un modulador delta y un integrador, como lo introdujeron por primera vez Inose et al. en su solicitud de patente [ aclaración necesaria ] . [7] Es decir, el nombre proviene de integrar o sumar diferencias , que, en matemáticas, son operaciones generalmente asociadas con las letras griegas sigma y delta respectivamente.

En la década de 1970, los ingenieros de Bell Labs utilizaron los términos "sigma-delta" porque el precedente era nombrar las variaciones en la modulación delta con adjetivos que precedían a "delta", y un editor de la revista Analog Devices justificó en 1990 que la jerarquía funcional es "sigma-delta", porque calcula la integral de una diferencia. [32]

Ambos nombres, sigma-delta y delta-sigma, se utilizan con frecuencia.

Kirkkert y Miller publicaron una variante de tiempo continuo llamada "Modulación Delta Sigma Asincrónica" (ADSM o ASDM) en 1975, que utiliza un disparador Schmitt (es decir, un comparador con histéresis ) o (como sostiene el artículo que es equivalente) un comparador con retardo fijo. [33]

En el ejemplo de la Figura 9, cuando la integral del error excede sus límites, la salida cambia de estado y produce una onda de salida modulada por ancho de pulso (PWM).

La información de amplitud se convierte, sin ruido de cuantificación, en información de tiempo del PWM de salida. [34] Para convertir este PWM de tiempo continuo a tiempo discreto, el PWM puede ser muestreado por un convertidor de tiempo a digital, cuya resolución limitada agrega ruido que puede moldearse al realimentarlo. [35]