En electrónica , el transistor de efecto de campo de metal-óxido-semiconductor ( MOSFET , MOS-FET , MOS FET o transistor MOS ) es un tipo de transistor de efecto de campo (FET), que se fabrica habitualmente mediante la oxidación controlada de silicio . Tiene una compuerta aislada, cuyo voltaje determina la conductividad del dispositivo. Esta capacidad de cambiar la conductividad con la cantidad de voltaje aplicado se puede utilizar para amplificar o conmutar señales electrónicas . El término transistor de efecto de campo de metal-aislante-semiconductor ( MISFET ) es casi sinónimo de MOSFET . Otro casi sinónimo es transistor de efecto de campo de compuerta aislada ( IGFET ).

La principal ventaja de un MOSFET es que prácticamente no requiere corriente de entrada para controlar la corriente de carga, en comparación con los transistores de unión bipolar (BJT). En un MOSFET de modo de mejora , el voltaje aplicado a la terminal de compuerta aumenta la conductividad del dispositivo. En los transistores de modo de agotamiento , el voltaje aplicado en la compuerta reduce la conductividad. [1]

El término "metal" en el nombre MOSFET es a veces un término inapropiado , ya que el material de la compuerta puede ser una capa de polisilicio (silicio policristalino). De manera similar, el término "óxido" en el nombre también puede ser un término inapropiado, ya que se utilizan diferentes materiales dieléctricos con el objetivo de obtener canales fuertes con voltajes aplicados más pequeños.

El MOSFET es, con diferencia, el transistor más común en los circuitos digitales , ya que se pueden incluir miles de millones en un chip de memoria o un microprocesador. Dado que los MOSFET pueden fabricarse con semiconductores de tipo p o de tipo n, se pueden utilizar pares complementarios de transistores MOS para crear circuitos de conmutación con un consumo de energía muy bajo, en forma de lógica CMOS .

El principio básico del transistor de efecto de campo fue patentado por primera vez por Julius Edgar Lilienfeld en 1925. [2] En 1934, el inventor Oskar Heil patentó de forma independiente un dispositivo similar en Europa. [3]

En la década de 1940, los científicos de Bell Labs William Shockley , John Bardeen y Walter Houser Brattain intentaron construir un dispositivo de efecto de campo, lo que les llevó a descubrir el efecto transistor . Sin embargo, la estructura no logró mostrar los efectos esperados, debido al problema de los estados superficiales : trampas en la superficie del semiconductor que mantienen inmóviles a los electrones. Sin pasivación superficial , solo pudieron construir los transistores BJT y de tiristores .

En 1955, Carl Frosch y Lincoln Derick accidentalmente hicieron crecer una capa de dióxido de silicio sobre la oblea de silicio, para lo cual observaron efectos de pasivación superficial. [4] [5] Para 1957, Frosch y Derick, usando enmascaramiento y predeposición, pudieron fabricar transistores de efecto de campo de dióxido de silicio; los primeros transistores planares, en los que el drenaje y la fuente estaban adyacentes en la misma superficie. [6] Demostraron que el dióxido de silicio aislaba, protegía las obleas de silicio y evitaba que los dopantes se difundieran en la oblea. [4] [7] En Bell Labs, la importancia de la técnica y los transistores de Frosch y Derick se comprendió inmediatamente. Los resultados de su trabajo circularon por Bell Labs en forma de memorandos BTL antes de ser publicados en 1957. En Shockley Semiconductor , Shockley había hecho circular la preimpresión de su artículo en diciembre de 1956 a todo su personal superior, incluido Jean Hoerni , [8] [9] [10] [11] quien más tarde inventaría el proceso planar en 1959 mientras estaba en Fairchild Semiconductor . [12] [13]

Después de esto, JR Ligenza y WG Spitzer estudiaron el mecanismo de los óxidos cultivados térmicamente, fabricaron una pila Si/ SiO2 de alta calidad y publicaron sus resultados en 1960. [15] [16] [17] Después de esta investigación, Mohamed Atalla y Dawon Kahng propusieron un transistor MOS de silicio en 1959 [18] y demostraron con éxito un dispositivo MOS funcional con su equipo de Bell Labs en 1960. [19] [20] Su equipo incluía a EE LaBate y EI Povilonis, quienes fabricaron el dispositivo; MO Thurston, LA D'Asaro y JR Ligenza, quienes desarrollaron los procesos de difusión, y HK Gummel y R. Lindner, quienes caracterizaron el dispositivo. [21] [22] Esta fue la culminación de décadas de investigación sobre el efecto de campo que comenzó con Lilienfeld.

El primer transistor MOS de Bell Labs era aproximadamente 100 veces más lento que los transistores bipolares contemporáneos y en un principio se lo consideró inferior. Sin embargo, Kahng destacó varias ventajas del dispositivo, en particular la facilidad de fabricación y su aplicación en circuitos integrados . [23]

Por lo general, el semiconductor de elección es el silicio . Algunos fabricantes de chips, en particular IBM e Intel , utilizan una aleación de silicio y germanio ( SiGe ) en los canales MOSFET. [ cita requerida ] Muchos semiconductores con mejores propiedades eléctricas que el silicio, como el arseniuro de galio , no forman buenas interfaces semiconductor-aislante y, por lo tanto, no son adecuados para los MOSFET. Se continúa investigando para crear aislantes con características eléctricas aceptables en otros materiales semiconductores.

Para superar el aumento en el consumo de energía debido a la fuga de corriente de la compuerta, se utiliza un dieléctrico de alto κ en lugar de dióxido de silicio para el aislante de la compuerta, mientras que el polisilicio se reemplaza por compuertas metálicas (por ejemplo, Intel , 2009). [24]

La compuerta está separada del canal por una fina capa aislante, tradicionalmente de dióxido de silicio y más tarde de oxinitruro de silicio . Algunas empresas utilizan una combinación de dieléctrico de alto κ y compuerta metálica en el nodo de 45 nanómetros .

Cuando se aplica un voltaje entre la compuerta y la fuente, el campo eléctrico generado penetra a través del óxido y crea una capa o canal de inversión en la interfaz semiconductor-aislante. La capa de inversión proporciona un canal a través del cual puede pasar la corriente entre los terminales de la fuente y el drenador. Al variar el voltaje entre la compuerta y el cuerpo se modula la conductividad de esta capa y, por lo tanto, se controla el flujo de corriente entre el drenador y la fuente. Esto se conoce como modo de mejora.

La estructura tradicional de metal-óxido-semiconductor (MOS) se obtiene haciendo crecer una capa de dióxido de silicio ( SiO

2) sobre un sustrato de silicio, habitualmente por oxidación térmica y deposición de una capa de metal o silicio policristalino (este último es el de uso común). Como el dióxido de silicio es un material dieléctrico , su estructura es equivalente a la de un condensador plano , con uno de los electrodos sustituido por un semiconductor.

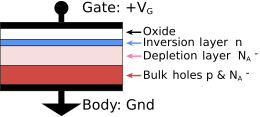

Cuando se aplica un voltaje a través de una estructura MOS, se modifica la distribución de cargas en el semiconductor. Si consideramos un semiconductor de tipo p (con N A la densidad de aceptores , p la densidad de huecos; p = N A en masa neutra), un voltaje positivo, V G , desde la compuerta al cuerpo (ver figura) crea una capa de agotamiento al forzar a los huecos cargados positivamente a alejarse de la interfaz compuerta-aislante/semiconductor, dejando expuesta una región libre de portadores de iones aceptores inmóviles, cargados negativamente (ver dopaje ). Si V G es lo suficientemente alto, se forma una alta concentración de portadores de carga negativa en una capa de inversión ubicada en una capa delgada junto a la interfaz entre el semiconductor y el aislante.

Convencionalmente, el voltaje de compuerta en el que la densidad de volumen de electrones en la capa de inversión es la misma que la densidad de volumen de huecos en el cuerpo se denomina voltaje umbral . Cuando el voltaje entre la compuerta del transistor y la fuente ( V G ) excede el voltaje umbral ( V th ), la diferencia se conoce como voltaje de sobremarcha .

Esta estructura con cuerpo tipo p es la base del MOSFET tipo n, que requiere la adición de regiones de fuente y drenaje tipo n.

La estructura del condensador MOS es el corazón del MOSFET. Consideremos un condensador MOS donde la base de silicio es de tipo p. Si se aplica un voltaje positivo en la compuerta, los huecos que están en la superficie del sustrato de tipo p serán repelidos por el campo eléctrico generado por el voltaje aplicado. Al principio, los huecos simplemente serán repelidos y lo que permanecerá en la superficie serán átomos inmóviles (negativos) del tipo aceptor, lo que crea una región de agotamiento en la superficie. Un hueco es creado por un átomo aceptor, por ejemplo, el boro, que tiene un electrón menos que un átomo de silicio. Los huecos en realidad no son repelidos, ya que no son entidades; los electrones son atraídos por el campo positivo y llenan estos huecos. Esto crea una región de agotamiento donde no existen portadores de carga porque el electrón ahora está fijado al átomo e inmóvil.

A medida que aumenta el voltaje en la compuerta, habrá un punto en el que la superficie sobre la región de agotamiento se convertirá de tipo p a tipo n, ya que los electrones del área principal comenzarán a ser atraídos por el campo eléctrico más grande. Esto se conoce como inversión . El voltaje umbral en el que ocurre esta conversión es uno de los parámetros más importantes en un MOSFET.

En el caso de un MOSFET de tipo p, la inversión de masa ocurre cuando el nivel de energía intrínseca en la superficie se vuelve más pequeño que el nivel de Fermi en la superficie. Esto se puede ver en un diagrama de bandas. El nivel de Fermi define el tipo de semiconductor en cuestión. Si el nivel de Fermi es igual al nivel intrínseco, el semiconductor es de tipo intrínseco o puro. Si el nivel de Fermi se encuentra más cerca de la banda de conducción (banda de valencia), entonces el tipo de semiconductor será de tipo n (tipo p).

Cuando el voltaje de la compuerta aumenta en un sentido positivo (para el ejemplo dado), [ aclarar ] esto desplazará la banda del nivel de energía intrínseca de modo que se curvará hacia abajo en dirección a la banda de valencia. Si el nivel de Fermi se encuentra más cerca de la banda de valencia (para el tipo p), habrá un punto en el que el nivel intrínseco comenzará a cruzar el nivel de Fermi y cuando el voltaje alcance el voltaje umbral, el nivel intrínseco cruzará el nivel de Fermi, y eso es lo que se conoce como inversión. En ese punto, la superficie del semiconductor se invierte de tipo p a tipo n.

Si el nivel de Fermi se encuentra por encima del nivel intrínseco, el semiconductor es de tipo n, por lo tanto, en la inversión, cuando el nivel intrínseco alcanza y cruza el nivel de Fermi (que se encuentra más cerca de la banda de valencia), el tipo de semiconductor cambia en la superficie según lo dictado por las posiciones relativas de los niveles de energía de Fermi e intrínseco.

Un MOSFET se basa en la modulación de la concentración de carga por una capacitancia MOS entre un electrodo del cuerpo y un electrodo de compuerta ubicado sobre el cuerpo y aislado de todas las demás regiones del dispositivo por una capa dieléctrica de compuerta. Si se emplean dieléctricos distintos de un óxido, el dispositivo puede denominarse FET semiconductor de metal aislante (MISFET). En comparación con el condensador MOS, el MOSFET incluye dos terminales adicionales ( fuente y drenaje ), cada uno conectado a regiones individuales altamente dopadas que están separadas por la región del cuerpo. Estas regiones pueden ser de tipo p o n, pero ambas deben ser del mismo tipo y de tipo opuesto a la región del cuerpo. La fuente y el drenaje (a diferencia del cuerpo) están altamente dopados, como lo indica un signo "+" después del tipo de dopaje.

Si el MOSFET es un canal n o un FET nMOS, entonces la fuente y el drenador son regiones n+ y el cuerpo es una región p . Si el MOSFET es un canal p o un FET pMOS, entonces la fuente y el drenador son regiones p+ y el cuerpo es una región n . La fuente se llama así porque es la fuente de los portadores de carga (electrones para el canal n, huecos para el canal p) que fluyen a través del canal; de manera similar, el drenador es donde los portadores de carga salen del canal.

La ocupación de las bandas de energía en un semiconductor está determinada por la posición del nivel de Fermi en relación con los bordes de la banda de energía del semiconductor.

Con suficiente voltaje de compuerta, el borde de la banda de valencia se aleja del nivel de Fermi y los agujeros del cuerpo se alejan de la compuerta.

En el caso de una polarización de compuerta aún mayor, cerca de la superficie del semiconductor, el borde de la banda de conducción se acerca al nivel de Fermi, llenando la superficie con electrones en una capa de inversión o canal n en la interfaz entre la región p y el óxido. Este canal conductor se extiende entre la fuente y el drenador, y la corriente se conduce a través de él cuando se aplica un voltaje entre los dos electrodos. El aumento del voltaje en la compuerta conduce a una mayor densidad de electrones en la capa de inversión y, por lo tanto, aumenta el flujo de corriente entre la fuente y el drenador. Para voltajes de compuerta por debajo del valor umbral, el canal está ligeramente poblado y solo una corriente de fuga subumbral muy pequeña puede fluir entre la fuente y el drenador.

Cuando se aplica un voltaje negativo de compuerta-fuente (compuerta-fuente positiva), se crea un canal p en la superficie de la región n, análogo al caso del canal n, pero con polaridades opuestas de cargas y voltajes. Cuando se aplica un voltaje menos negativo que el valor umbral (un voltaje negativo para el canal p) entre la compuerta y la fuente, el canal desaparece y solo puede fluir una corriente subumbral muy pequeña entre la fuente y el drenador. El dispositivo puede comprender un dispositivo de silicio sobre aislante en el que se forma un óxido enterrado debajo de una capa semiconductora delgada. Si la región del canal entre el dieléctrico de la compuerta y la región de óxido enterrado es muy delgada, el canal se denomina región de canal ultradelgada con las regiones de fuente y drenador formadas a cada lado en o por encima de la capa semiconductora delgada. Se pueden emplear otros materiales semiconductores. Cuando las regiones de fuente y drenador se forman por encima del canal en su totalidad o en parte, se denominan regiones de fuente/drenaje elevadas.

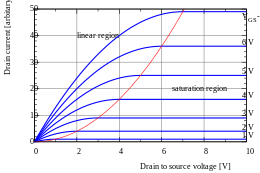

El funcionamiento de un MOSFET se puede dividir en tres modos diferentes, dependiendo de los voltajes en los terminales. En la siguiente discusión, se utiliza un modelo algebraico simplificado. [27] Las características de los MOSFET modernos son más complejas que el modelo algebraico presentado aquí. [28]

Para un MOSFET de canal n con modo de mejora , los tres modos operativos son:

Cuando V GS < V th :

donde es la polarización de puerta a fuente y es el voltaje umbral del dispositivo.

Según el modelo de umbral básico, el transistor está apagado y no hay conducción entre el drenaje y la fuente. Un modelo más preciso considera el efecto de la energía térmica en la distribución de Fermi-Dirac de las energías de los electrones, que permite que algunos de los electrones más energéticos de la fuente entren en el canal y fluyan hacia el drenaje. Esto da como resultado una corriente de subumbral que es una función exponencial del voltaje de la compuerta-fuente. Si bien la corriente entre el drenaje y la fuente debería ser idealmente cero cuando el transistor se usa como un interruptor apagado, existe una corriente de inversión débil, a veces llamada fuga de subumbral.

En la inversión débil donde la fuente está ligada al volumen, la corriente varía exponencialmente como se indica aproximadamente en: [29] [30]

donde = corriente en , el voltaje térmico y el factor de pendiente n viene dado por:

con = capacitancia de la capa de agotamiento y = capacitancia de la capa de óxido. Esta ecuación se utiliza generalmente, pero es solo una aproximación adecuada para la fuente ligada al volumen. Para la fuente no ligada al volumen, la ecuación de subumbral para la corriente de drenaje en saturación es [31] [32]

En un dispositivo de canal largo, no existe dependencia del voltaje de drenaje de la corriente una vez , pero a medida que se reduce la longitud del canal, la reducción de la barrera inducida por el drenaje introduce una dependencia del voltaje de drenaje que depende de manera compleja de la geometría del dispositivo (por ejemplo, el dopaje del canal, el dopaje de la unión, etc.). Con frecuencia, el voltaje umbral V th para este modo se define como el voltaje de compuerta en el que ocurre un valor seleccionado de corriente I D0 , por ejemplo, I D0 = 1 μA, que puede no ser el mismo valor V th utilizado en las ecuaciones para los siguientes modos.

Algunos circuitos analógicos de micropotencia están diseñados para aprovechar la conducción subumbral. [33] [34] [35] Al trabajar en la región de inversión débil, los MOSFET en estos circuitos ofrecen la relación transconductancia-corriente más alta posible, es decir: , casi la de un transistor bipolar. [36]

La curva subumbral I–V depende exponencialmente del voltaje umbral, lo que introduce una fuerte dependencia de cualquier variación de fabricación que afecte al voltaje umbral; por ejemplo: variaciones en el espesor del óxido, la profundidad de la unión o el dopaje del cuerpo que cambian el grado de reducción de la barrera inducida por el drenaje. La sensibilidad resultante a las variaciones de fabricación complica la optimización de las fugas y el rendimiento. [37] [38]

Cuando V GS > V th y V DS < V GS − V th :

El transistor está encendido y se ha creado un canal que permite el paso de corriente entre el drenador y la fuente. El MOSFET funciona como una resistencia, controlada por el voltaje de compuerta en relación con los voltajes de la fuente y el drenador. La corriente del drenador a la fuente se modela como:

donde es la movilidad efectiva del portador de carga, es el ancho de la compuerta, es la longitud de la compuerta y es la capacitancia del óxido de la compuerta por unidad de área. La transición de la región subumbral exponencial a la región de triodo no es tan nítida como sugieren las ecuaciones. [39] [40] [ verificación necesaria ]

Cuando V GS > V th y V DS ≥ (V GS – V th ):

El interruptor se enciende y se crea un canal que permite el paso de corriente entre el drenaje y la fuente. Como el voltaje del drenaje es mayor que el voltaje de la fuente, los electrones se dispersan y la conducción no se produce a través de un canal estrecho, sino a través de una distribución de corriente bidimensional o tridimensional más amplia que se extiende desde la interfaz hasta una zona más profunda del sustrato. El inicio de esta región también se conoce como " estrangulamiento" para indicar la falta de una región de canal cerca del drenaje. Aunque el canal no se extiende por toda la longitud del dispositivo, el campo eléctrico entre el drenaje y el canal es muy alto y la conducción continúa. La corriente del drenaje ahora depende débilmente del voltaje del drenaje y está controlada principalmente por el voltaje de la compuerta-fuente, y se modela aproximadamente como:

El factor adicional que involucra λ, el parámetro de modulación de longitud de canal, modela la dependencia de la corriente con respecto al voltaje de drenaje debido al efecto Early o modulación de longitud de canal . Según esta ecuación, un parámetro de diseño clave, la transconductancia del MOSFET es:

donde la combinación V ov = V GS − V th se denomina voltaje de sobreexcitación , [41] y donde V DSsat = V GS − V th representa una pequeña discontinuidad que de otro modo aparecería en la transición entre las regiones de triodo y saturación.

Otro parámetro de diseño clave es la resistencia de salida del MOSFET rout dada por:

.

r out es la inversa de g DS donde I D es la expresión en la región de saturación .

Si λ se toma como cero, el resultado es una resistencia de salida infinita del dispositivo, lo que lleva a predicciones de circuitos poco realistas, particularmente en circuitos analógicos.

A medida que la longitud del canal se hace muy corta, estas ecuaciones se vuelven bastante inexactas. Surgen nuevos efectos físicos. Por ejemplo, el transporte de portadores en el modo activo puede verse limitado por la saturación de velocidad . Cuando domina la saturación de velocidad, la corriente de drenaje de saturación es más casi lineal que cuadrática en V GS . En longitudes incluso más cortas, los portadores se transportan con una dispersión cercana a cero, conocida como transporte cuasibalístico . En el régimen balístico, los portadores viajan a una velocidad de inyección que puede superar la velocidad de saturación y se acerca a la velocidad de Fermi a alta densidad de carga de inversión. Además, la reducción de barrera inducida por el drenaje aumenta la corriente de estado fuera de estado (corte) y requiere un aumento en el voltaje de umbral para compensar, lo que a su vez reduce la corriente de saturación. [42] [43] [ verificación necesaria ]

La ocupación de las bandas de energía en un semiconductor está determinada por la posición del nivel de Fermi en relación con los bordes de la banda de energía del semiconductor. La aplicación de una polarización inversa de la unión pn entre fuente y sustrato introduce una división entre los niveles de Fermi para electrones y huecos, alejando el nivel de Fermi del canal del borde de la banda y reduciendo la ocupación del canal. El efecto es aumentar el voltaje de compuerta necesario para establecer el canal, como se ve en la figura. Este cambio en la intensidad del canal mediante la aplicación de una polarización inversa se denomina "efecto de cuerpo".

Usando un ejemplo nMOS, el sesgo de puerta a cuerpo V GB posiciona los niveles de energía de la banda de conducción, mientras que el sesgo de fuente a cuerpo V SB posiciona el nivel de Fermi del electrón cerca de la interfaz, decidiendo la ocupación de estos niveles cerca de la interfaz y, por lo tanto, la fuerza de la capa o canal de inversión.

El efecto del cuerpo sobre el canal se puede describir utilizando una modificación del voltaje umbral, aproximada por la siguiente ecuación:

donde V TB es el voltaje umbral con polarización del sustrato presente, y V T0 es el valor cero de V SB del voltaje umbral, es el parámetro de efecto corporal, y 2 φ B es la caída de potencial aproximada entre la superficie y el volumen a través de la capa de agotamiento cuando V SB = 0 y la polarización de la compuerta es suficiente para garantizar que haya un canal presente. [44] Como muestra esta ecuación, una polarización inversa V SB > 0 provoca un aumento en el voltaje umbral V TB y, por lo tanto, exige un voltaje de compuerta más grande antes de que el canal se llene.

El cuerpo puede funcionar como una segunda puerta y a veces se lo denomina "puerta trasera"; el efecto del cuerpo a veces se denomina "efecto de puerta trasera". [45]

Se utilizan diversos símbolos para el MOSFET. El diseño básico es generalmente una línea para el canal con la fuente y el drenaje que salen de él en ángulos rectos y luego se doblan hacia atrás en ángulos rectos en la misma dirección que el canal. A veces se utilizan tres segmentos de línea para el modo de mejora y una línea sólida para el modo de agotamiento (consulte los modos de agotamiento y mejora ). Se dibuja otra línea paralela al canal para la compuerta.

La conexión del cuerpo o del bulto , si se muestra, se muestra conectada a la parte posterior del canal con una flecha que indica pMOS o nMOS. Las flechas siempre apuntan de P a N, por lo que un NMOS (canal N en pozo P o sustrato P) tiene la flecha apuntando hacia adentro (del bulto al canal). Si el bulto está conectado a la fuente (como suele ser el caso con los dispositivos discretos), a veces está en ángulo para encontrarse con la fuente que sale del transistor. Si el bulto no se muestra (como suele ser el caso en el diseño de CI, ya que generalmente son bultos comunes), a veces se usa un símbolo de inversión para indicar PMOS; alternativamente, se puede usar una flecha en la fuente de la misma manera que para los transistores bipolares (hacia afuera para nMOS, hacia adentro para pMOS).

Comparación de los símbolos de MOSFET en modo de mejora y en modo de agotamiento, junto con los símbolos de JFET . La orientación de los símbolos (y más significativamente la posición de la fuente en relación con el drenador) es tal que los voltajes más positivos aparecen más arriba en la página que los voltajes menos positivos, lo que implica que la corriente convencional fluye "hacia abajo" por la página: [46] [47] [48]

En los esquemas en los que no se indican G, S y D, las características detalladas del símbolo indican qué terminal es la fuente y cuál es el drenador. En los símbolos MOSFET en modo de mejora y modo de agotamiento (en las columnas dos y cinco), el terminal de la fuente es el que está conectado al triángulo. Además, en este diagrama, la compuerta se muestra en forma de "L", cuyo lado de entrada está más cerca de S que de D, lo que también indica cuál es cuál. Sin embargo, estos símbolos a menudo se dibujan con una compuerta en forma de T (como en otras partes de esta página), por lo que es el triángulo en el que se debe confiar para indicar el terminal de la fuente.

En los símbolos en los que se muestra el terminal de masa o cuerpo, se muestra conectado internamente a la fuente (es decir, los triángulos negros en los diagramas de las columnas 2 y 5). Esta es una configuración típica, pero de ninguna manera la única configuración importante. En general, el MOSFET es un dispositivo de cuatro terminales y, en los circuitos integrados, muchos de los MOSFET comparten una conexión de cuerpo, no necesariamente conectada a los terminales de fuente de todos los transistores.

Los circuitos integrados digitales , como los microprocesadores y los dispositivos de memoria, contienen miles o miles de millones de transistores MOSFET integrados en cada dispositivo, que proporcionan las funciones de conmutación básicas necesarias para implementar puertas lógicas y almacenamiento de datos . Los dispositivos discretos se utilizan ampliamente en aplicaciones como fuentes de alimentación conmutadas , variadores de frecuencia y otras aplicaciones de electrónica de potencia en las que cada dispositivo puede conmutar miles de vatios. Los amplificadores de radiofrecuencia hasta el espectro UHF utilizan transistores MOSFET como amplificadores de potencia y de señal analógica. Los sistemas de radio también utilizan MOSFET como osciladores o mezcladores para convertir frecuencias. Los dispositivos MOSFET también se aplican en amplificadores de potencia de audiofrecuencia para sistemas de megafonía, refuerzo de sonido y sistemas de sonido domésticos y de automóviles [ cita requerida ]

Tras el desarrollo de las salas blancas para reducir la contaminación a niveles nunca antes considerados necesarios, y de la fotolitografía [49] y el proceso planar para permitir la fabricación de circuitos en muy pocos pasos, el sistema Si–SiO2 poseía los atractivos técnicos de un bajo coste de producción (por circuito) y una fácil integración. En gran medida debido a estos dos factores, el MOSFET se ha convertido en el tipo de transistor más utilizado en la Institución de Ingeniería y Tecnología (IET). [ cita requerida ]

General Microelectronics introdujo el primer circuito integrado MOS comercial en 1964. [50] Además, el método de acoplar dos MOSFET complementarios (canal P y canal N) en un interruptor alto/bajo, conocido como CMOS, significa que los circuitos digitales disipan muy poca energía excepto cuando están realmente conmutados.

Los primeros microprocesadores que aparecieron en 1970 eran todos microprocesadores MOS , es decir, fabricados completamente con lógica PMOS o fabricados completamente con lógica NMOS . En la década de 1970, los microprocesadores MOS se contrastaban a menudo con los microprocesadores CMOS y los procesadores bipolares de corte de bits . [51]

El MOSFET se utiliza en la lógica complementaria digital de semiconductores de óxido metálico ( CMOS ), [52] que utiliza MOSFET de canal p y n como bloques de construcción. El sobrecalentamiento es una preocupación importante en los circuitos integrados , ya que cada vez se empaquetan más transistores en chips cada vez más pequeños. La lógica CMOS reduce el consumo de energía porque no fluye corriente (idealmente) y, por lo tanto, no se consume energía , excepto cuando se conmutan las entradas a las puertas lógicas . CMOS logra esta reducción de corriente complementando cada nMOSFET con un pMOSFET y conectando ambas puertas y ambos drenadores juntos. Un alto voltaje en las puertas hará que el nMOSFET conduzca y el pMOSFET no conduzca y un bajo voltaje en las puertas provoca lo contrario. Durante el tiempo de conmutación a medida que el voltaje pasa de un estado a otro, ambos MOSFET conducirán brevemente. Esta disposición reduce en gran medida el consumo de energía y la generación de calor.

El crecimiento de las tecnologías digitales como el microprocesador ha proporcionado la motivación para avanzar en la tecnología MOSFET más rápido que cualquier otro tipo de transistor basado en silicio. [53] Una gran ventaja de los MOSFET para la conmutación digital es que la capa de óxido entre la compuerta y el canal evita que la corriente continua fluya a través de la compuerta, lo que reduce aún más el consumo de energía y proporciona una impedancia de entrada muy grande. El óxido aislante entre la compuerta y el canal aísla eficazmente un MOSFET en una etapa lógica de las etapas anteriores y posteriores, lo que permite que una sola salida MOSFET controle una cantidad considerable de entradas MOSFET. La lógica basada en transistores bipolares (como TTL ) no tiene una capacidad de abanico de salida tan alta. Este aislamiento también hace que sea más fácil para los diseñadores ignorar hasta cierto punto los efectos de carga entre las etapas lógicas de forma independiente. Esa medida está definida por la frecuencia de operación: a medida que aumentan las frecuencias, la impedancia de entrada de los MOSFET disminuye.

Las ventajas del MOSFET en los circuitos digitales no se traducen en supremacía en todos los circuitos analógicos . Los dos tipos de circuitos se basan en diferentes características del comportamiento del transistor. Los circuitos digitales conmutan, pasando la mayor parte del tiempo totalmente encendidos o totalmente apagados. La transición de uno a otro solo es preocupante en lo que respecta a la velocidad y la carga requerida. Los circuitos analógicos dependen del funcionamiento en la región de transición donde pequeños cambios en V gs pueden modular la corriente de salida (drenaje). El JFET y el transistor de unión bipolar (BJT) son los preferidos por su coincidencia precisa (de dispositivos adyacentes en circuitos integrados), mayor transconductancia y ciertas características de temperatura que simplifican el mantenimiento del rendimiento predecible a medida que varía la temperatura del circuito.

Sin embargo, los MOSFET se utilizan ampliamente en muchos tipos de circuitos analógicos debido a sus propias ventajas (corriente de compuerta cero, impedancia de salida alta y ajustable y robustez mejorada frente a los BJT que pueden degradarse permanentemente incluso rompiendo ligeramente el emisor-base). [ vago ] Las características y el rendimiento de muchos circuitos analógicos se pueden escalar hacia arriba o hacia abajo cambiando los tamaños (longitud y anchura) de los MOSFET utilizados. En comparación, en los transistores bipolares siguen una ley de escala diferente . Las características ideales de los MOSFET con respecto a la corriente de compuerta (cero) y la tensión de compensación de drenaje-fuente (cero) también los convierten en elementos de conmutación casi ideales, y también hacen prácticos los circuitos analógicos de condensadores conmutados . En su región lineal, los MOSFET se pueden utilizar como resistencias de precisión, que pueden tener una resistencia controlada mucho mayor que los BJT. En circuitos de alta potencia, los MOSFET a veces tienen la ventaja de no sufrir fugas térmicas como lo hacen los BJT. [ dudoso – discutir ] Esto significa que se pueden hacer circuitos analógicos completos en un chip de silicio en un espacio mucho más pequeño y con técnicas de fabricación más simples. Los MOSFET son ideales para conmutar cargas inductivas debido a su tolerancia al retroceso inductivo .

Algunos circuitos integrados combinan circuitos MOSFET analógicos y digitales en un único circuito integrado de señal mixta , lo que hace que el espacio necesario en la placa sea aún menor. Esto crea la necesidad de aislar los circuitos analógicos de los circuitos digitales a nivel de chip, lo que lleva al uso de anillos de aislamiento y silicio sobre aislante (SOI). Dado que los MOSFET requieren más espacio para manejar una cantidad determinada de energía que un BJT, los procesos de fabricación pueden incorporar BJT y MOSFET en un único dispositivo. Los dispositivos de transistores mixtos se denominan bi-FET (FET bipolares) si contienen solo un BJT-FET y BiCMOS (CMOS bipolar) si contienen BJT-FET complementarios. Dichos dispositivos tienen las ventajas de puertas aisladas y una mayor densidad de corriente.

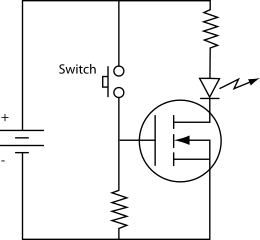

Los interruptores analógicos MOSFET utilizan el MOSFET para pasar señales analógicas cuando están encendidos y como una alta impedancia cuando están apagados. Las señales fluyen en ambas direcciones a través de un interruptor MOSFET. En esta aplicación, el drenaje y la fuente de un MOSFET intercambian posiciones según los voltajes relativos de los electrodos de fuente y drenaje. La fuente es el lado más negativo para un N-MOS o el lado más positivo para un P-MOS. Todos estos interruptores están limitados en cuanto a las señales que pueden pasar o detener por sus voltajes de compuerta-fuente, compuerta-drenaje y fuente-drenaje; exceder los límites de voltaje, corriente o potencia dañará potencialmente el interruptor.

Este interruptor analógico utiliza un MOSFET simple de cuatro terminales de tipo P o N.

En el caso de un interruptor de tipo n, el cuerpo está conectado a la fuente de alimentación más negativa (normalmente GND) y la compuerta se utiliza como control del interruptor. Siempre que el voltaje de la compuerta supere el voltaje de la fuente en al menos un voltaje umbral, el MOSFET conduce. Cuanto mayor sea el voltaje, más puede conducir el MOSFET. Un interruptor N-MOS deja pasar todos los voltajes menores que V gate − V tn . Cuando el interruptor conduce, normalmente funciona en modo de funcionamiento lineal (u óhmico), ya que los voltajes de fuente y drenaje normalmente serán casi iguales.

En el caso de un P-MOS, el cuerpo se conecta al voltaje más positivo y la compuerta se lleva a un potencial más bajo para activar el interruptor. El interruptor P-MOS deja pasar todos los voltajes superiores a V compuerta − V tp (el voltaje umbral V tp es negativo en el caso de P-MOS en modo de mejora).

Este tipo de interruptor "complementario" o CMOS utiliza un FET P-MOS y un FET N-MOS para contrarrestar las limitaciones del interruptor de tipo único. Los FET tienen sus drenajes y fuentes conectados en paralelo, el cuerpo del P-MOS está conectado al potencial alto ( V DD ) y el cuerpo del N-MOS está conectado al potencial bajo ( gnd ). Para encender el interruptor, la compuerta del P-MOS se lleva al potencial bajo y la compuerta del N-MOS se lleva al potencial alto. Para voltajes entre V DD − V tn y gnd − V tp , ambos FET conducen la señal; para voltajes menores que gnd − V tp , el N-MOS conduce solo; y para voltajes mayores que V DD − V tn , el P-MOS conduce solo.

Los límites de voltaje para este interruptor son los límites de voltaje de compuerta-fuente, compuerta-drenaje y fuente-drenaje para ambos FET. Además, el P-MOS es típicamente dos o tres veces más ancho que el N-MOS, por lo que el interruptor estará equilibrado para la velocidad en las dos direcciones.

Los circuitos triestado a veces incorporan un interruptor CMOS MOSFET en su salida para proporcionar una salida de rango completo y de bajo valor óhmico cuando está encendido, y una señal de nivel medio y alto valor óhmico cuando está apagado.

El criterio principal para el material de la compuerta es que sea un buen conductor . El silicio policristalino altamente dopado es un conductor aceptable, pero ciertamente no ideal, y también sufre algunas deficiencias más técnicas en su función como material de compuerta estándar. Sin embargo, hay varias razones que favorecen el uso del polisilicio:

Si bien las compuertas de polisilicio han sido el estándar de facto durante los últimos veinte años, tienen algunas desventajas que han llevado a su probable reemplazo en el futuro por compuertas de metal. Estas desventajas incluyen:

Las CPU de alto rendimiento actuales utilizan tecnología de compuerta metálica, junto con dieléctricos de alto κ , una combinación conocida como compuerta metálica de alto κ (HKMG). Las desventajas de las compuertas metálicas se superan con algunas técnicas: [54]

A medida que los dispositivos se hacen más pequeños, las capas aislantes se hacen más delgadas, a menudo a través de pasos de oxidación térmica u oxidación localizada del silicio ( LOCOS ). Para los dispositivos a escala nanométrica, en algún punto se produce la tunelización de los portadores a través del aislante desde el canal hasta el electrodo de compuerta. Para reducir la corriente de fuga resultante , el aislante se puede hacer más delgado eligiendo un material con una constante dieléctrica más alta. Para ver cómo se relacionan el espesor y la constante dieléctrica, observe que la ley de Gauss conecta el campo con la carga como:

con Q = densidad de carga, κ = constante dieléctrica, ε 0 = permitividad del espacio vacío y E = campo eléctrico. De esta ley se desprende que la misma carga puede mantenerse en el canal a un campo menor siempre que κ aumente. El voltaje en la compuerta viene dado por:

donde V G = voltaje de compuerta, V ch = voltaje en el lado del canal del aislador y t ins = espesor del aislador. Esta ecuación muestra que el voltaje de compuerta no aumentará cuando el espesor del aislador aumente, siempre que κ aumente para mantener t ins / κ = constante (consulte el artículo sobre dieléctricos de alto κ para obtener más detalles y la sección de este artículo sobre fuga de óxido de compuerta).

El aislante de un MOSFET es un dieléctrico que puede ser en cualquier caso óxido de silicio, formado por LOCOS , pero se emplean muchos otros materiales dieléctricos. El término genérico para el dieléctrico es dieléctrico de compuerta, ya que el dieléctrico se encuentra directamente debajo del electrodo de compuerta y encima del canal del MOSFET.

Las uniones fuente-cuerpo y drenaje-cuerpo son objeto de mucha atención debido a tres factores principales: su diseño afecta las características de corriente-voltaje ( IV ) del dispositivo, reduciendo la resistencia de salida y también la velocidad del dispositivo a través del efecto de carga de las capacitancias de la unión y, finalmente, el componente de disipación de potencia en espera debido a la fuga de la unión.

La reducción de la barrera inducida por el drenaje de la tensión de umbral y los efectos de modulación de la longitud del canal sobre las curvas IV se reducen mediante el uso de extensiones de unión poco profundas. Además, se puede utilizar el dopaje de halo , es decir, la adición de regiones muy delgadas y muy dopadas del mismo tipo de dopaje que el cuerpo, ajustadas contra las paredes de la unión, para limitar la extensión de las regiones de agotamiento . [55]

Los efectos capacitivos se limitan mediante el uso de geometrías de fuente y drenaje elevadas que hacen que la mayor parte del borde del área de contacto sea dieléctrico grueso en lugar de silicio. [56]

Estas diversas características del diseño de uniones se muestran (con licencia artística ) en la figura.

En las últimas décadas, el MOSFET (tal como se utiliza para la lógica digital) ha sido continuamente reducido en tamaño; las longitudes típicas de canal de MOSFET alguna vez fueron de varios micrómetros , pero los circuitos integrados modernos están incorporando MOSFET con longitudes de canal de decenas de nanómetros. El trabajo de Robert Dennard sobre la teoría de escala fue fundamental para reconocer que esta reducción continua era posible. Intel comenzó la producción de un proceso con un tamaño de característica de 32 nm (con el canal siendo incluso más corto) a fines de 2009. La industria de semiconductores mantiene una "hoja de ruta", el ITRS , [57] que marca el ritmo para el desarrollo de MOSFET. Históricamente, las dificultades para disminuir el tamaño del MOSFET se han asociado con el proceso de fabricación de dispositivos semiconductores, la necesidad de usar voltajes muy bajos y con un rendimiento eléctrico más pobre que requiere rediseño e innovación de circuitos (los MOSFET pequeños exhiben corrientes de fuga más altas y menor resistencia de salida).

Los MOSFET más pequeños son deseables por varias razones. La razón principal para hacer transistores más pequeños es empaquetar más y más dispositivos en un área determinada del chip. Esto da como resultado un chip con la misma funcionalidad en un área más pequeña, o chips con más funcionalidad en la misma área. Dado que los costos de fabricación de una oblea de semiconductores son relativamente fijos, el costo por circuito integrado está relacionado principalmente con la cantidad de chips que se pueden producir por oblea. Por lo tanto, los CI más pequeños permiten más chips por oblea, lo que reduce el precio por chip. De hecho, durante los últimos 30 años, la cantidad de transistores por chip se ha duplicado cada 2 o 3 años una vez que se introduce un nuevo nodo tecnológico. Por ejemplo, la cantidad de MOSFET en un microprocesador fabricado en una tecnología de 45 nm puede ser el doble que en un chip de 65 nm . Esta duplicación de la densidad de transistores fue observada por primera vez por Gordon Moore en 1965 y se conoce comúnmente como la ley de Moore . [58] También se espera que los transistores más pequeños conmuten más rápido. Por ejemplo, un enfoque para la reducción de tamaño es un escalado del MOSFET que requiere que todas las dimensiones del dispositivo se reduzcan proporcionalmente. Las dimensiones principales del dispositivo son la longitud del canal, el ancho del canal y el espesor del óxido. Cuando se reducen en factores iguales, la resistencia del canal del transistor no cambia, mientras que la capacitancia de la compuerta se reduce en ese factor. Por lo tanto, el retardo RC del transistor se escala con un factor similar. Si bien este ha sido tradicionalmente el caso para las tecnologías más antiguas, para los MOSFET de última generación la reducción de las dimensiones del transistor no se traduce necesariamente en una mayor velocidad del chip porque el retraso debido a las interconexiones es más significativo.

La producción de MOSFET con longitudes de canal mucho más pequeñas que un micrómetro es un desafío, y las dificultades de fabricación de dispositivos semiconductores son siempre un factor limitante en el avance de la tecnología de circuitos integrados. Aunque procesos como la ALD han mejorado la fabricación de componentes pequeños, el pequeño tamaño del MOSFET (menos de unas pocas decenas de nanómetros) ha creado problemas operativos:

A medida que las geometrías de los MOSFET se reducen, el voltaje que se puede aplicar a la compuerta debe reducirse para mantener la confiabilidad. Para mantener el rendimiento, también se debe reducir el voltaje umbral del MOSFET. A medida que se reduce el voltaje umbral, el transistor no puede pasar de apagado completo a encendido completo con la oscilación de voltaje limitada disponible; el diseño del circuito es un compromiso entre una corriente fuerte en el caso de encendido y una corriente baja en el caso de apagado , y la aplicación determina si se favorece una sobre la otra. La fuga subumbral (incluida la conducción subumbral, la fuga de óxido de compuerta y la fuga de unión con polarización inversa), que se ignoraba en el pasado, ahora puede consumir más de la mitad del consumo total de energía de los chips VLSI de alto rendimiento modernos. [59] [60]

El óxido de compuerta, que sirve como aislante entre la compuerta y el canal, debe hacerse lo más fino posible para aumentar la conductividad y el rendimiento del canal cuando el transistor está encendido y para reducir la fuga por debajo del umbral cuando el transistor está apagado. Sin embargo, con óxidos de compuerta actuales con un espesor de alrededor de 1,2 nm (que en el silicio es de ~5 átomos de espesor) se produce el fenómeno mecánico cuántico de tunelización de electrones entre la compuerta y el canal, lo que conduce a un mayor consumo de energía. El dióxido de silicio se ha utilizado tradicionalmente como aislante de la compuerta. Sin embargo, el dióxido de silicio tiene una constante dieléctrica modesta. Aumentar la constante dieléctrica del dieléctrico de la compuerta permite una capa más gruesa manteniendo una alta capacitancia (la capacitancia es proporcional a la constante dieléctrica e inversamente proporcional al espesor dieléctrico). En igualdad de condiciones, un mayor espesor dieléctrico reduce la corriente de tunelización cuántica a través del dieléctrico entre la compuerta y el canal.

Los aislantes que tienen una constante dieléctrica mayor que el dióxido de silicio (denominados dieléctricos de alto κ ), como los silicatos metálicos del grupo IVb, por ejemplo, los silicatos y óxidos de hafnio y circonio, se están utilizando para reducir la fuga de la compuerta a partir del nodo de tecnología de 45 nanómetros en adelante. Por otro lado, la altura de la barrera del nuevo aislante de la compuerta es una consideración importante; la diferencia en la energía de la banda de conducción entre el semiconductor y el dieléctrico (y la diferencia correspondiente en la energía de la banda de valencia ) también afecta el nivel de corriente de fuga. Para el óxido de compuerta tradicional, el dióxido de silicio, la barrera anterior es de aproximadamente 8 eV . Para muchos dieléctricos alternativos, el valor es significativamente menor, lo que tiende a aumentar la corriente de tunelización, anulando en cierta medida la ventaja de una constante dieléctrica más alta. El voltaje máximo de la compuerta-fuente está determinado por la intensidad del campo eléctrico que puede sostener el dieléctrico de la compuerta antes de que se produzca una fuga significativa. A medida que el dieléctrico aislante se hace más delgado, la intensidad del campo eléctrico dentro de él aumenta para un voltaje fijo. Esto requiere utilizar voltajes más bajos con el dieléctrico más delgado.

Para hacer dispositivos más pequeños, el diseño de las uniones se ha vuelto más complejo, lo que lleva a mayores niveles de dopaje , uniones menos profundas, dopaje de "halo", etc., [61] [62] todo para disminuir la reducción de la barrera inducida por el drenaje (consulte la sección sobre el diseño de las uniones). Para mantener estas uniones complejas en su lugar, los pasos de recocido que se usaban anteriormente para eliminar daños y defectos eléctricamente activos deben reducirse [63] , lo que aumenta la fuga de las uniones. Un dopaje más pesado también se asocia con capas de agotamiento más delgadas y más centros de recombinación que dan como resultado una mayor corriente de fuga, incluso sin daño en la red.

Reducción de barrera inducida por drenaje (DIBL) y reducción gradual de VT : debido al efecto de canal corto , la formación del canal no la realiza completamente la compuerta, sino que ahora el drenador y la fuente también afectan la formación del canal. A medida que disminuye la longitud del canal, las regiones de agotamiento de la fuente y el drenador se acercan y hacen que el voltaje umbral ( VT) sea una función de la longitud del canal. Esto se llama reducción gradual de VT. VT también se convierte en función del voltaje de drenador a fuente VDS . A medida que aumentamos VDS , las regiones de agotamiento aumentan de tamaño y VDS agota una cantidad considerable de carga . Luego, el voltaje de compuerta necesario para formar el canal se reduce y, por lo tanto, VT disminuye con un aumento de VDS . Este efecto se llama reducción de barrera inducida por drenaje (DIBL).

Para el funcionamiento analógico, una buena ganancia requiere una alta impedancia de salida del MOSFET, es decir, la corriente del MOSFET debe variar solo ligeramente con el voltaje de drenaje a fuente aplicado. A medida que los dispositivos se hacen más pequeños, la influencia del drenaje compite con más éxito con la de la compuerta debido a la creciente proximidad de estos dos electrodos, lo que aumenta la sensibilidad de la corriente del MOSFET al voltaje de drenaje. Para contrarrestar la disminución resultante en la resistencia de salida, los circuitos se hacen más complejos, ya sea requiriendo más dispositivos, por ejemplo, los amplificadores en cascada y en cascodo , o mediante circuitos de retroalimentación que utilizan amplificadores operacionales , por ejemplo, un circuito como el de la figura adyacente.

La transconductancia del MOSFET determina su ganancia y es proporcional a la movilidad de los huecos o de los electrones (según el tipo de dispositivo), al menos para voltajes de drenaje bajos. A medida que se reduce el tamaño del MOSFET, aumentan los campos en el canal y los niveles de impurezas dopantes aumentan. Ambos cambios reducen la movilidad de los portadores y, por lo tanto, la transconductancia. A medida que se reducen las longitudes de los canales sin una reducción proporcional del voltaje de drenaje, lo que aumenta el campo eléctrico en el canal, el resultado es la saturación de la velocidad de los portadores, lo que limita la corriente y la transconductancia.

Tradicionalmente, el tiempo de conmutación era aproximadamente proporcional a la capacidad de las compuertas. Sin embargo, a medida que los transistores se hacen más pequeños y se colocan más transistores en el chip, la capacidad de interconexión (la capacidad de las conexiones de la capa metálica entre las diferentes partes del chip) se está convirtiendo en un gran porcentaje de la capacidad. [64] [65] Las señales tienen que viajar a través de la interconexión, lo que genera un mayor retraso y un menor rendimiento.

La densidad cada vez mayor de MOSFET en un circuito integrado crea problemas de generación de calor localizado sustancial que puede perjudicar el funcionamiento del circuito. Los circuitos funcionan más lentamente a altas temperaturas y tienen una confiabilidad reducida y una vida útil más corta. Ahora se requieren disipadores de calor y otros dispositivos y métodos de enfriamiento para muchos circuitos integrados, incluidos los microprocesadores. Los MOSFET de potencia corren el riesgo de sufrir una fuga térmica . A medida que su resistencia en estado encendido aumenta con la temperatura, si la carga es aproximadamente una carga de corriente constante, la pérdida de potencia aumenta correspondientemente, generando más calor. Cuando el disipador de calor no puede mantener la temperatura lo suficientemente baja, la temperatura de la unión puede aumentar rápidamente e incontrolablemente, lo que resulta en la destrucción del dispositivo.

A medida que los MOSFET se hacen más pequeños, el número de átomos en el silicio que producen muchas de las propiedades del transistor se hace menor, con el resultado de que el control de la cantidad y la colocación de dopantes es más errático. Durante la fabricación de chips, las variaciones aleatorias del proceso afectan a todas las dimensiones del transistor: longitud, ancho, profundidades de unión, espesor del óxido , etc. , y se convierten en un porcentaje mayor del tamaño total del transistor a medida que el transistor se encoge. Las características del transistor se vuelven menos seguras, más estadísticas. La naturaleza aleatoria de la fabricación significa que no sabemos qué ejemplo particular de MOSFET realmente terminará en una instancia particular del circuito. Esta incertidumbre obliga a un diseño menos óptimo porque el diseño debe funcionar para una gran variedad de posibles MOSFET de componentes. Véase variación del proceso , diseño para la fabricación , ingeniería de confiabilidad y control estadístico de procesos . [66]

Los circuitos integrados modernos se simulan por ordenador con el objetivo de obtener circuitos funcionales a partir del primer lote fabricado. A medida que los dispositivos se miniaturizan, la complejidad del procesamiento dificulta predecir exactamente cómo se verán los dispositivos finales, y el modelado de procesos físicos también se vuelve más complicado. Además, las variaciones microscópicas en la estructura debidas simplemente a la naturaleza probabilística de los procesos atómicos requieren predicciones estadísticas (no solo deterministas). Estos factores se combinan para dificultar la simulación adecuada y la fabricación "correcta a la primera".

El MOSFET de doble compuerta tiene una configuración de tetrodo , donde ambas compuertas controlan la corriente en el dispositivo. Se utiliza comúnmente para dispositivos de pequeña señal en aplicaciones de radiofrecuencia donde la polarización de la compuerta del lado del drenador a potencial constante reduce la pérdida de ganancia causada por el efecto Miller , reemplazando dos transistores separados en la configuración de cascada . Otros usos comunes en circuitos de RF incluyen el control de ganancia y la mezcla (conversión de frecuencia). La descripción del tetrodo , aunque precisa, no replica el tetrodo de tubo de vacío. Los tetrodos de tubo de vacío, que utilizan una rejilla de pantalla, exhiben una capacitancia de placa de rejilla mucho menor y una impedancia de salida y ganancias de voltaje mucho mayores que los tubos de vacío de triodo. Estas mejoras son comúnmente de un orden de magnitud (10 veces) o considerablemente más. Los transistores de tetrodo (ya sea de unión bipolar o de efecto de campo) no exhiben mejoras de un grado tan grande.

El FinFET es un dispositivo de silicio sobre aislante de doble compuerta , una de las diversas geometrías que se están introduciendo para mitigar los efectos de los canales cortos y reducir la reducción de la barrera inducida por el drenaje. La aleta se refiere al canal estrecho entre la fuente y el drenaje. Una fina capa de óxido aislante a cada lado de la aleta la separa de la compuerta. Los FinFET SOI con un óxido grueso en la parte superior de la aleta se denominan de doble compuerta y los que tienen un óxido fino en la parte superior y en los lados se denominan FinFET de triple compuerta . [67] [68]

Existen dispositivos MOSFET de modo de agotamiento , que se utilizan con menos frecuencia que los dispositivos de modo de mejora estándar ya descritos. Se trata de dispositivos MOSFET que están dopados de modo que existe un canal incluso con voltaje cero desde la compuerta a la fuente. Para controlar el canal, se aplica un voltaje negativo a la compuerta (para un dispositivo de canal n), agotando el canal, lo que reduce el flujo de corriente a través del dispositivo. En esencia, el dispositivo de modo de agotamiento es equivalente a un interruptor normalmente cerrado (encendido), mientras que el dispositivo de modo de mejora es equivalente a un interruptor normalmente abierto (apagado). [69]

Debido a su bajo factor de ruido en la región de RF y mejor ganancia , estos dispositivos suelen preferirse a los bipolares en los front-ends de RF, como en los televisores .

Las familias de MOSFET de modo de agotamiento incluyen el BF960 de Siemens y Telefunken , y el BF980 en la década de 1980 de Philips (que más tarde se convertiría en NXP Semiconductors ), cuyos derivados todavía se utilizan en los front-end de mezcladores AGC y RF .

Transistor de efecto de campo metal-aislante-semiconductor, [70] [71] [72] o MISFET , es un término más general que MOSFET y un sinónimo de transistor de efecto de campo de puerta aislada (IGFET). Todos los MOSFET son MISFET, pero no todos los MISFET son MOSFET.

El aislante dieléctrico de la compuerta en un MISFET es un óxido de sustrato (por lo tanto, típicamente dióxido de silicio ) en un MOSFET, pero también se pueden utilizar otros materiales. El dieléctrico de la compuerta se encuentra directamente debajo del electrodo de la compuerta y encima del canal del MISFET. El término metal se utiliza históricamente para el material de la compuerta, aunque ahora suele ser polisilicio altamente dopado o algún otro no metal .

Los tipos de aisladores pueden ser:

Para dispositivos con la misma capacidad de conducción de corriente, los MOSFET de canal n se pueden hacer más pequeños que los MOSFET de canal p, debido a que los portadores de carga de canal p ( huecos ) tienen menor movilidad que los portadores de carga de canal n ( electrones ), y producir solo un tipo de MOSFET sobre un sustrato de silicio es más barato y técnicamente más simple. Estos fueron los principios impulsores en el diseño de la lógica NMOS que utiliza exclusivamente MOSFET de canal n. Sin embargo, al descuidar la corriente de fuga , a diferencia de la lógica CMOS, la lógica NMOS consume energía incluso cuando no se está produciendo ninguna conmutación. Con los avances en la tecnología, la lógica CMOS desplazó a la lógica NMOS a mediados de la década de 1980 para convertirse en el proceso preferido para los chips digitales.

Power MOSFETs have a different structure.[74] As with most power devices, the structure is vertical and not planar. Using a vertical structure, it is possible for the transistor to sustain both high blocking voltage and high current. The voltage rating of the transistor is a function of the doping and thickness of the N-epitaxial layer (see cross section), while the current rating is a function of the channel width (the wider the channel, the higher the current). In a planar structure, the current and breakdown voltage ratings are both a function of the channel dimensions (respectively width and length of the channel), resulting in inefficient use of the "silicon estate". With the vertical structure, the component area is roughly proportional to the current it can sustain, and the component thickness (actually the N-epitaxial layer thickness) is proportional to the breakdown voltage.[75]

Power MOSFETs with lateral structure are mainly used in high-end audio amplifiers and high-power PA systems. Their advantage is a better behaviour in the saturated region (corresponding to the linear region of a bipolar transistor) than the vertical MOSFETs. Vertical MOSFETs are designed for switching applications.[76]

There are LDMOS (lateral double-diffused metal oxide semiconductor) and VDMOS (vertical double-diffused metal oxide semiconductor). Most power MOSFETs are made using this technology.

Semiconductor sub-micrometer and nanometer electronic circuits are the primary concern for operating within the normal tolerance in harsh radiation environments like outer space. One of the design approaches for making a radiation-hardened-by-design (RHBD) device is enclosed-layout-transistor (ELT). Normally, the gate of the MOSFET surrounds the drain, which is placed in the center of the ELT. The source of the MOSFET surrounds the gate. Another RHBD MOSFET is called H-Gate. Both of these transistors have very low leakage currents with respect to radiation. However, they are large in size and take up more space on silicon than a standard MOSFET. In older STI (shallow trench isolation) designs, radiation strikes near the silicon oxide region cause the channel inversion at the corners of the standard MOSFET due to accumulation of radiation induced trapped charges. If the charges are large enough, the accumulated charges affect STI surface edges along the channel near the channel interface (gate) of the standard MOSFET. This causes a device channel inversion to occur along the channel edges, creating an off-state leakage path. Subsequently, the device turns on; this process severely degrades the reliability of circuits. The ELT offers many advantages, including an improvement of reliability by reducing unwanted surface inversion at the gate edges which occurs in the standard MOSFET. Since the gate edges are enclosed in ELT, there is no gate oxide edge (STI at gate interface), and thus the transistor off-state leakage is reduced very much. Low-power microelectronic circuits including computers, communication devices, and monitoring systems in space shuttles and satellites are very different from what is used on earth. They are radiation (high-speed atomic particles like proton and neutron, solar flare magnetic energy dissipation in Earth's space, energetic cosmic rays like X-ray, gamma ray etc.) tolerant circuits. These special electronics are designed by applying different techniques using RHBD MOSFETs to ensure safe space journeys and safe space-walks of astronauts.