La fabricación de dispositivos semiconductores es el proceso utilizado para fabricar dispositivos semiconductores , típicamente circuitos integrados (CI), como procesadores de computadora , microcontroladores y chips de memoria (como NAND flash y DRAM ) que están presentes en los dispositivos electrónicos cotidianos . Es un proceso fotolitográfico y fisicoquímico de múltiples pasos (con pasos como oxidación térmica , deposición de película delgada, implantación de iones, grabado) durante el cual se crean gradualmente circuitos electrónicos en una oblea , generalmente hecha de semiconductores monocristalinos puros. material. Casi siempre se utiliza silicio , pero se utilizan varios semiconductores compuestos para aplicaciones especializadas.

El proceso de fabricación se realiza en plantas de fabricación de semiconductores altamente especializadas , también llamadas fundiciones o "fabs", [1] siendo la parte central la " sala limpia ". En dispositivos semiconductores más avanzados, como los nodos modernos de 14/10/7 nm , la fabricación puede tardar hasta 15 semanas, siendo el promedio de la industria entre 11 y 13 semanas . [2] La producción en instalaciones de fabricación avanzadas está completamente automatizada, con sistemas automatizados de manipulación de materiales que se encargan del transporte de las obleas de una máquina a otra. [3]

Una oblea suele tener varios circuitos integrados que se denominan troqueles , ya que son piezas cortadas en cubitos de una sola oblea. Los troqueles individuales se separan de una oblea terminada en un proceso llamado singularización del troquel , también llamado corte en cubitos de oblea. A continuación, las matrices pueden someterse a un mayor montaje y embalaje. [4]

Dentro de las plantas de fabricación, las obleas se transportan dentro de cajas de plástico selladas especiales llamadas FOUP . [3] Los FOUP en muchas fábricas contienen una atmósfera interna de nitrógeno [5] [6] que ayuda a evitar que el cobre se oxide en las obleas. El cobre se utiliza en semiconductores modernos para cableado. [7] El interior del equipo de procesamiento y los FOUP se mantiene más limpio que el aire circundante en la sala limpia. Esta atmósfera interna se conoce como miniambiente y ayuda a mejorar el rendimiento, que es la cantidad de dispositivos en funcionamiento en una oblea. Este mini entorno se encuentra dentro de un EFEM (módulo frontal del equipo) [8] que permite que una máquina reciba FOUP e introduce obleas de los FOUP en la máquina. Además, muchas máquinas también manipulan obleas en entornos limpios de nitrógeno o vacío para reducir la contaminación y mejorar el control del proceso. [3] Las plantas de fabricación necesitan grandes cantidades de nitrógeno líquido para mantener la atmósfera dentro de la maquinaria de producción y los FOUP, que se purgan constantemente con nitrógeno. [5] [6] También puede haber una cortina de aire entre el FOUP y el EFEM que ayuda a reducir la cantidad de humedad que ingresa al FOUP y mejora el rendimiento. [9] [10]

Las empresas que fabrican máquinas utilizadas en el proceso de fabricación de semiconductores industriales incluyen ASML , Applied Materials , Tokyo Electron y Lam Research .

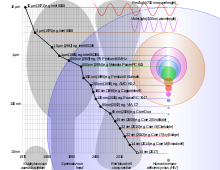

El tamaño de la característica está determinado por el ancho de las líneas más pequeñas que se pueden modelar en un proceso de fabricación de semiconductores; esta medida se conoce como ancho de línea. [11] [12] El patrón a menudo se refiere a la fotolitografía que permite definir un diseño o patrón de dispositivo en el dispositivo durante la fabricación. [13] F 2 se utiliza como medida de área para diferentes partes de un dispositivo semiconductor, en función del tamaño de la característica de un proceso de fabricación de semiconductores. Muchos dispositivos semiconductores están diseñados en secciones llamadas celdas, y cada celda representa una pequeña parte del dispositivo, como una celda de memoria para almacenar datos. Así, se utiliza F 2 para medir el área ocupada por estas células o secciones. [14]

Un proceso de semiconductores específico tiene reglas específicas sobre el tamaño mínimo (ancho o CD/dimensión crítica) y el espaciado para las características de cada capa del chip. [15] Normalmente, un nuevo proceso de semiconductores tiene tamaños mínimos más pequeños y espacios más reducidos. En algunos casos, esto permite una simple reducción de un diseño de chip producido actualmente para reducir costos, mejorar el rendimiento [15] y aumentar la densidad de transistores (número de transistores por unidad de área) sin el gasto de un nuevo diseño.

Los primeros procesos de semiconductores tuvieron nombres arbitrarios durante generaciones (a saber, HMOS I/II/III/IV y CHMOS III/III-E/IV/V). Posteriormente, cada proceso de nueva generación se conoció como nodo tecnológico [16] o nodo de proceso , [17] [18] designado por el tamaño mínimo de característica del proceso en nanómetros (o históricamente micrómetros ) de la longitud de la puerta del transistor del proceso , como el " Proceso de 90 nm ". Sin embargo, este no ha sido el caso desde 1994, [19] y el número de nanómetros utilizados para nombrar los nodos de proceso (ver la Hoja de ruta tecnológica internacional para semiconductores ) se ha convertido más bien en un término de marketing que no tiene una relación estandarizada con los tamaños de características funcionales o con densidad de transistores (número de transistores por unidad de área). [20]

Inicialmente, la longitud de la puerta del transistor era menor que la sugerida por el nombre del nodo del proceso (por ejemplo, nodo de 350 nm); sin embargo, esta tendencia se revirtió en 2009. [19] Los tamaños de las características no pueden tener conexión con los nanómetros (nm) utilizados en marketing. Por ejemplo, el antiguo proceso de 10 nm de Intel en realidad tiene características (las puntas de las aletas FinFET ) con un ancho de 7 nm, por lo que el proceso de Intel de 10 nm es similar en densidad de transistores al proceso de 7 nm de TSMC . Como otro ejemplo, los procesos de 12 y 14 nm de GlobalFoundries tienen tamaños de características similares. [21] [22] [20]

Chih-Tang Sah y Frank Wanlass desarrollaron un tipo mejorado de tecnología MOSFET , CMOS , en Fairchild Semiconductor en 1963. [23] [24] RCA comercializó CMOS a finales de la década de 1960. [23] RCA utilizó comercialmente CMOS para sus circuitos integrados de la serie 4000 en 1968, comenzando con un proceso de 20 µm antes de escalar gradualmente a un proceso de 10 µm durante los siguientes años. [25] Muchos de los primeros fabricantes de dispositivos semiconductores desarrollaron y construyeron sus propios equipos, como implantadores de iones. [26]

Desde entonces, la fabricación de dispositivos semiconductores se ha extendido desde Texas y California en la década de 1960 al resto del mundo, incluidos Asia , Europa y Oriente Medio .

En la década de 1970, varias empresas migraron su tecnología de fabricación de semiconductores de la tecnología bipolar a la tecnología CMOS. [27]

En 1985, STmicroelectronics inventó BCD, también llamado BCDMOS, un proceso de fabricación de semiconductores que utiliza dispositivos bipolares , CMOS y LDMOS . [28] También se puede realizar con dispositivos Bipolar, CMOS y DMOS. [29]

Las obleas de 200 mm de diámetro se utilizaron por primera vez en 1990 para fabricar chips. Estos se convirtieron en el estándar hasta la introducción de las obleas de 300 mm de diámetro en 2000. [30] [31] Con el tiempo, la industria pasó a las obleas de 300 mm, pero muchos productos que no son avanzados todavía se producen en obleas de 200 mm, como circuitos integrados analógicos y chips de RF. , circuitos integrados de alimentación, dispositivos BCDMOS y MEMS. [32] Algunos procesos como limpieza, [33] implantación de iones, [34] [35] grabado, [36] recocido [37] y oxidación [38] comenzaron a adoptar el procesamiento de obleas individuales en lugar del procesamiento de obleas por lotes para mejorar la reproducibilidad de los resultados. [39] [40] Existía una tendencia similar en la fabricación de MEMS. [41] [42]

La industria de los semiconductores es hoy un negocio global. Los principales fabricantes de semiconductores suelen tener instalaciones en todo el mundo. Samsung Electronics , el mayor fabricante de semiconductores del mundo, tiene instalaciones en Corea del Sur y Estados Unidos. Intel , el segundo mayor fabricante, tiene instalaciones en Europa y Asia, además de Estados Unidos. TSMC , la fundición exclusiva más grande del mundo , tiene instalaciones en Taiwán, China, Singapur y Estados Unidos. Qualcomm y Broadcom se encuentran entre las mayores empresas de semiconductores sin fábrica y subcontratan su producción a empresas como TSMC. [43] También tienen instalaciones repartidas en diferentes países. A medida que aumentó la utilización promedio de los dispositivos semiconductores, la durabilidad se convirtió en un problema y los fabricantes comenzaron a diseñar sus dispositivos para garantizar que duraran el tiempo suficiente, y esto depende del mercado para el que está diseñado el dispositivo. Esto se convirtió especialmente en un problema en el nodo de 10 nm. [44] [45]

La tecnología de silicio sobre aislante (SOI) se ha utilizado en los procesadores AMD de 130 nm, 90 nm, 65 nm, 45 nm y 32 nm de uno, dos, cuatro, seis y ocho núcleos fabricados desde 2001. [46]

Desde 2009, "nodo" se ha convertido en un nombre comercial con fines de marketing que indica nuevas generaciones de tecnologías de proceso, sin ninguna relación con la longitud de la puerta, el paso del metal o el paso de la puerta. [47] [48] [49] Por ejemplo, el proceso de 7 nm de GlobalFoundries es similar al proceso de 10 nm de Intel , por lo que la noción convencional de un nodo de proceso se ha vuelto borrosa. [50] Además, los procesos de 10 nm de TSMC y Samsung son sólo ligeramente más densos que los 14 nm de Intel en densidad de transistores. En realidad, están mucho más cerca del proceso de 14 nm de Intel que del proceso de 10 nm de Intel (por ejemplo, el paso de las aletas de los procesos de 10 nm de Samsung es exactamente el mismo que el del proceso de 14 nm de Intel: 42 nm). [51] [52] A medida que los transistores se vuelven más pequeños, nuevos efectos comienzan a influir en las decisiones de diseño, como el autocalentamiento de los transistores, y otros efectos, como la electromigración, se han vuelto más evidentes desde el nodo de 16 nm. [53] [54]

En 2011, Intel demostró los transistores de efecto de campo Fin , donde la puerta rodea el canal en tres lados, lo que permite una mayor eficiencia energética y un menor retardo de la puerta (y, por lo tanto, un mayor rendimiento) en comparación con los transistores planos. [55] [56] [57]

En 2018, se habían propuesto varias arquitecturas de transistores para el eventual reemplazo de FinFET , la mayoría de las cuales se basaban en el concepto de GAAFET : [58] nanocables horizontales y verticales, transistores de nanoláminas horizontales [59] [60] (Samsung MBCFET, Intel Nanoribbon), FET vertical (VFET) y otros transistores verticales, [61] [62] FET complementario (CFET), FET apilado, varios tipos de transistores de puerta horizontal, como nanoanillo, alambre hexagonal, alambre cuadrado , y transistores de puerta de alambre redondo [63] y FET de capacitancia negativa (NC-FET) que utiliza materiales drásticamente diferentes. [64] FD-SOI fue visto como una posible alternativa de bajo costo a los FinFET. [sesenta y cinco]

A partir de 2019, Intel, UMC , TSMC, Samsung, Micron , SK Hynix , Toshiba Memory y GlobalFoundries están produciendo en masa chips de 14 nanómetros y 10 nanómetros , con chips de proceso de 7 nanómetros en producción en masa de TSMC y Samsung, aunque sus 7 nanómetros están en producción en masa. La definición de nodo es similar al proceso de 10 nanómetros de Intel. Samsung comenzó a producir el proceso de 5 nanómetros en 2018. [66] A partir de 2019, el nodo con la mayor densidad de transistores es el nodo N5 de 5 nanómetros de TSMC , [67] con una densidad de 171,3 millones de transistores por milímetro cuadrado. [68] En 2019, Samsung y TSMC anunciaron planes para producir nodos de 3 nanómetros . GlobalFoundries ha decidido detener el desarrollo de nuevos nodos más allá de los 12 nanómetros para ahorrar recursos, ya que ha determinado que establecer una nueva fábrica para manejar pedidos de menos de 12 nm estaría más allá de las capacidades financieras de la empresa. [69] Intel ha cambiado el nombre de su proceso de 10 nm para posicionarlo como un proceso de 7 nm. [70]

Esta es una lista de técnicas de procesamiento que se emplean numerosas veces durante la construcción de un dispositivo electrónico moderno; Esta lista no implica necesariamente un orden específico, ni que se tomen todas las técnicas durante la fabricación ya que, en la práctica, el orden y las técnicas que se aplican, a menudo son específicos de los procesos ofrecidos por las fundiciones, o específicos de un fabricante de dispositivos integrados (IDM) para sus propios productos, y es posible que un dispositivo semiconductor no necesite todas las técnicas. Los equipos para llevar a cabo estos procesos son fabricados por un puñado de empresas . Es necesario probar todos los equipos antes de poner en marcha una planta de fabricación de semiconductores. [71] Estos procesos se realizan después del diseño del circuito integrado . Una fábrica de semiconductores funciona las 24 horas del día, los 7 días de la semana [72] y muchas fábricas utilizan grandes cantidades de agua. [73]

Se pueden llevar a cabo pasos adicionales como el grabado de Wright .

Cuando los anchos de las características eran mucho mayores que aproximadamente 10 micrómetros , la pureza de los semiconductores no era un problema tan grande como lo es hoy en la fabricación de dispositivos. En la década de 1960, los trabajadores podían trabajar en dispositivos semiconductores vestidos con ropa de calle. [92] A medida que los dispositivos se vuelven más integrados, las salas blancas deben volverse aún más limpias. Hoy en día, las plantas de fabricación están presurizadas con aire filtrado para eliminar incluso las partículas más pequeñas, que podrían depositarse en las obleas y contribuir a la aparición de defectos. Los techos de las salas blancas de semiconductores tienen unidades de filtrado de ventiladores (FFU) a intervalos regulares para reemplazar y filtrar constantemente el aire en la sala blanca; Los equipos de capital semiconductores también pueden tener sus propias FFU para limpiar el aire en el EFEM del equipo, lo que permite que el equipo reciba obleas en FOUP. Las FFU, combinadas con suelos elevados con rejillas, ayudan a garantizar un flujo de aire laminar, para garantizar que las partículas bajen inmediatamente al suelo y no queden suspendidas en el aire debido a las turbulencias. Los trabajadores de una instalación de fabricación de semiconductores deben usar trajes de sala blanca para proteger los dispositivos de la contaminación humana. [93] Para aumentar el rendimiento, los FOUP y los bienes de capital semiconductores pueden tener un mini entorno con nivel de polvo ISO clase 1, y los FOUP pueden tener un micro entorno aún más limpio. [10] [8] Las cápsulas FOUP y SMIF aíslan las obleas del aire en la sala limpia, lo que aumenta el rendimiento porque reducen la cantidad de defectos causados por las partículas de polvo. Además, las fábricas tienen la menor cantidad de personas posible en la sala limpia para facilitar el mantenimiento del ambiente de la sala limpia, ya que las personas, incluso cuando usan trajes para sala blanca, arrojan grandes cantidades de partículas, especialmente al caminar. [94] [93] [95]

Una oblea típica está hecha de silicio extremadamente puro que se convierte en lingotes cilíndricos monocristalinos ( bolas ) de hasta 300 mm (un poco menos de 12 pulgadas) de diámetro mediante el proceso Czochralski . A continuación, estos lingotes se cortan en obleas de aproximadamente 0,75 mm de espesor y se pulen para obtener una superficie muy regular y plana.

En la fabricación de dispositivos semiconductores, los distintos pasos del procesamiento se dividen en cuatro categorías generales: deposición, eliminación, modelado y modificación de propiedades eléctricas.

La modificación de las propiedades eléctricas ahora también se extiende a la reducción de la constante dieléctrica de un material en aisladores de baja κ mediante la exposición a la luz ultravioleta en el procesamiento UV (UVP). La modificación se logra frecuentemente mediante oxidación , que se puede llevar a cabo para crear uniones semiconductor-aislante, como en la oxidación local de silicio ( LOCOS ) para fabricar transistores de efecto de campo de óxido metálico . Los chips modernos tienen hasta once o más niveles de metal producidos en más de 300 o más pasos de procesamiento secuenciados.

Una receta en la fabricación de semiconductores es una lista de condiciones bajo las cuales una máquina particular procesará una oblea en un paso de procesamiento durante la fabricación. [99]

El procesamiento FEOL se refiere a la formación de los transistores directamente en el silicio . La oblea cruda está diseñada mediante el crecimiento de una capa de silicio ultrapura y prácticamente libre de defectos a través de epitaxia . En los dispositivos lógicos más avanzados , previo al paso de epitaxia del silicio, se realizan trucos para mejorar el rendimiento de los transistores a construir. Un método implica introducir una etapa de deformación en la que se deposita una variante de silicio tal como silicio-germanio (SiGe). Una vez que se deposita el silicio epitaxial, la red cristalina se estira un poco, lo que mejora la movilidad electrónica. Otro método, llamado tecnología de silicio sobre aislante , implica la inserción de una capa aislante entre la oblea de silicio en bruto y la capa delgada de epitaxia de silicio posterior. Este método da como resultado la creación de transistores con efectos parásitos reducidos . Los equipos semiconductores pueden tener varias cámaras que procesan obleas en procesos como deposición y grabado. Muchos equipos manejan obleas entre estas cámaras en un ambiente interno de nitrógeno o vacío para mejorar el control del proceso. [3]

En 2007, Intel introdujo los transistores HKMG (high-k/metal gate) en el nodo de 45 nm, que reemplazaron a las puertas de polisilicio, que a su vez reemplazaron a la tecnología de puertas metálicas en la década de 1970. [100] El dieléctrico de alta k, como el óxido de hafnio (HFO 2 ), reemplazó al oxinitruro de silicio (SiON), para evitar grandes cantidades de corriente de fuga en el transistor y al mismo tiempo permitir el escalado o encogimiento continuo de los transistores. Sin embargo, HFO 2 no es compatible con puertas de polisilicio que requieren el uso de una puerta de metal. Se utilizaron dos enfoques en la producción: puerta primero y puerta última. La compuerta primero consiste en depositar el dieléctrico de alta k y luego el metal de la compuerta, como el nitruro de tantalio, cuya función de trabajo depende de si el transistor es NMOS o PMOS, deposición de polisilicio, patrón de línea de compuerta, implantación de iones de fuente y drenaje, recocido dopante y silicición. del polisilicio y la fuente y drenaje. [101] [102] Esta tecnología se adoptó por primera vez en 2015 en DRAM. [103]

La última puerta consistió en depositar primero el dieléctrico High-κ , crear puertas falsas, fabricar fuentes y drenajes mediante deposición de iones y recocido dopante, depositar un "dieléctrico entre niveles (ILD)" y luego pulir y retirar las puertas falsas para reemplazarlas con un metal cuya función de trabajo dependía de si el transistor era NMOS o PMOS, creando así la puerta de metal. Un tercer proceso, la silicuración total (FUSI) [104] no se llevó a cabo debido a problemas de fabricación. [105] La primera puerta se volvió dominante en el nodo de 22 nm/20 nm. [106] [107] HKMG se ha ampliado a partir de transistores planos para su uso en transistores FinFET y nanosheet. [108] También se puede utilizar oxinitruro de silicio de hafnio en lugar de óxido de hafnio. [109] [110] [3] [111] [112]

Desde el nodo de 16 nm/14 nm, el grabado de capa atómica (ALE) se utiliza cada vez más para el grabado, ya que ofrece mayor precisión que otros métodos de grabado. En producción se suele utilizar plasma ALE, que elimina materiales de forma unidireccional, creando estructuras con paredes verticales. El ALE térmico también se puede utilizar para eliminar materiales de forma isotrópica, en todas las direcciones al mismo tiempo, pero sin la capacidad de crear paredes verticales. El ALE de plasma se adoptó inicialmente para grabar contactos en transistores y, desde el nodo de 7 nm, también se utiliza para crear estructuras de transistores grabándolos. [80]

A la ingeniería de superficie inicial le sigue el crecimiento del dieléctrico de la compuerta (tradicionalmente dióxido de silicio ), el modelado de la compuerta, el modelado de las regiones de fuente y drenaje, y la posterior implantación o difusión de dopantes para obtener las propiedades eléctricas complementarias deseadas. En los dispositivos de memoria dinámica de acceso aleatorio (DRAM), también se fabrican condensadores de almacenamiento en este momento, normalmente apilados sobre el transistor de acceso (el ahora desaparecido fabricante de DRAM, Qimonda, implementó estos condensadores con zanjas grabadas profundamente en la superficie del silicio).

Una vez creados los diversos dispositivos semiconductores , se deben interconectar para formar los circuitos eléctricos deseados. Esto ocurre en una serie de pasos de procesamiento de obleas denominados colectivamente BEOL (que no debe confundirse con la parte posterior de la fabricación del chip, que se refiere a las etapas de empaque y prueba). El procesamiento BEOL implica la creación de cables metálicos de interconexión que están aislados por capas dieléctricas. El material aislante ha sido tradicionalmente una forma de SiO 2 o un vidrio de silicato , pero recientemente se están utilizando nuevos materiales de baja constante dieléctrica (como el oxicarburo de silicio), que normalmente proporcionan constantes dieléctricas de alrededor de 2,7 (en comparación con 3,82 para el SiO 2 ), aunque los materiales Con constantes tan bajas como 2,2 se ofrecen a los fabricantes de chips.

Desde el nodo de 22 nm, algunos fabricantes han agregado un nuevo proceso llamado mid-of-line (MOL) que conecta los transistores al resto de la interconexión realizada en el proceso BEoL. El MOL suele estar basado en tungsteno y tiene capas superior e inferior: la capa inferior conecta las uniones de los transistores y una capa superior que es un enchufe de tungsteno que conecta los transistores a la interconexión. Intel en el nodo de 10 nm introdujo contacto sobre puerta activa (COAG) que, en lugar de colocar el contacto para conectar el transistor cerca de la puerta del transistor, lo coloca directamente sobre la puerta del transistor para mejorar la densidad del transistor. [113]

Históricamente, los alambres metálicos han estado compuestos de aluminio . En este método de cableado (a menudo llamado aluminio sustractivo ), primero se depositan películas de aluminio, se modelan y luego se graban, dejando los cables aislados. Luego se deposita material dieléctrico sobre los cables expuestos. Las distintas capas metálicas se interconectan grabando orificios (llamados " vías") en el material aislante y luego depositando tungsteno en ellos con una técnica CVD utilizando hexafluoruro de tungsteno ; Este enfoque todavía se puede utilizar (y a menudo se utiliza) en la fabricación de muchos chips de memoria, como la memoria dinámica de acceso aleatorio (DRAM), porque el número de niveles de interconexión puede ser pequeño (no más de cuatro).

Más recientemente, a medida que el número de niveles de interconexión para la lógica ha aumentado sustancialmente debido a la gran cantidad de transistores que ahora están interconectados en un microprocesador moderno , el retraso en el tiempo en el cableado se ha vuelto tan significativo que provoca un cambio en el material del cableado (de capa de interconexión de aluminio a cobre ) y un cambio en el material dieléctrico (de dióxidos de silicio a nuevos aislantes de bajo κ ). Esta mejora del rendimiento también tiene un costo reducido gracias al procesamiento damasquinado , que elimina los pasos de procesamiento. A medida que aumenta el número de niveles de interconexión, se requiere la planarización de las capas anteriores para garantizar una superficie plana antes de la litografía posterior. Sin él, los niveles se torcerían cada vez más, extendiéndose más allá de la profundidad de enfoque de la litografía disponible e interfiriendo así con la capacidad de crear patrones. CMP ( planarización químico-mecánica ) es el método de procesamiento principal para lograr dicha planarización, aunque a veces todavía se emplea el grabado en seco cuando el número de niveles de interconexión no es superior a tres. Las interconexiones de cobre utilizan una capa de barrera eléctricamente conductora para evitar que el cobre se difunda ("envenene") su entorno, a menudo hecho de nitruro de tantalio. [114] [113]

En 2014, Applied Materials propuso el uso de cobalto en las interconexiones en el nodo de 22 nm, utilizado para encapsular las interconexiones de cobre en cobalto para evitar la electromigración, reemplazando el nitruro de tantalio, ya que debe ser más grueso que el cobalto en esta aplicación. [113] [115]

La naturaleza altamente serializada del procesamiento de obleas ha aumentado la demanda de metrología entre los distintos pasos del procesamiento. Por ejemplo, la metrología de película delgada basada en elipsometría o reflectometría se utiliza para controlar estrictamente el espesor del óxido de puerta, así como el espesor, el índice de refracción y el coeficiente de extinción del fotoprotector y otros recubrimientos. [116] El equipo de metrología de prueba de obleas se utiliza para verificar que las obleas no hayan sido dañadas por los pasos de procesamiento anteriores hasta la prueba; Si fallan demasiados troqueles en una oblea, se desecha toda la oblea para evitar los costos de procesamiento posterior. La metrología virtual se ha utilizado para predecir las propiedades de las obleas basándose en métodos estadísticos sin realizar la medición física en sí. [1]

Una vez que se ha completado el proceso inicial, los dispositivos semiconductores o chips se someten a una variedad de pruebas eléctricas para determinar si funcionan correctamente. El porcentaje de dispositivos en la oblea que funcionan correctamente se conoce como rendimiento . Los fabricantes suelen ser reservados sobre sus rendimientos, [117] pero pueden ser tan bajos como el 30%, lo que significa que sólo el 30% de los chips de la oblea funcionan según lo previsto. La variación del proceso es una entre muchas razones del bajo rendimiento. Se llevan a cabo pruebas para evitar que se monten chips defectuosos en paquetes relativamente caros.

El rendimiento suele estar relacionado, aunque no necesariamente, con el tamaño del dispositivo (troquel o chip). A modo de ejemplo, en diciembre de 2019, TSMC anunció un rendimiento promedio de ~80 %, con un rendimiento máximo por oblea de >90 % para sus chips de prueba de 5 nm con un tamaño de matriz de 17,92 mm 2 . El rendimiento bajó al 32,0% con un aumento en el tamaño del troquel a 100 mm 2 . [118] El número de defectos mortales en una oblea, independientemente del tamaño del troquel, se puede indicar como la densidad de defectos (o D 0 ) de la oblea por unidad de área, generalmente cm 2 .

La fábrica prueba los chips de la oblea con un probador electrónico que presiona pequeñas sondas contra el chip. La máquina marca cada chip defectuoso con una gota de tinte. Actualmente, el marcado electrónico con tintes es posible si los datos de las pruebas de obleas (resultados) se registran en una base de datos de computadora central y los chips se "agrupan" (es decir, se clasifican en contenedores virtuales) de acuerdo con límites de prueba predeterminados, como frecuencias/relojes máximos de operación, número de horas de trabajo. núcleos (totalmente funcionales) por chip, etc. Los datos de agrupación resultantes se pueden graficar o registrar en un mapa de oblea para rastrear defectos de fabricación y marcar chips defectuosos. Este mapa también se puede utilizar durante el ensamblaje y embalaje de las obleas. El binning permite reutilizar chips que de otro modo serían rechazados en productos de nivel inferior, como es el caso de las GPU y CPU, lo que aumenta el rendimiento del dispositivo, especialmente porque muy pocos chips son completamente funcionales (tienen todos los núcleos funcionando correctamente, por ejemplo). Los eFUSE se pueden utilizar para desconectar partes de chips, como núcleos, ya sea porque no funcionaron como se esperaba durante la agrupación o como parte de la segmentación del mercado (usando el mismo chip para los niveles de gama baja, media y alta). Los chips pueden tener piezas de repuesto para permitir que pasen completamente las pruebas incluso si tienen varias piezas que no funcionan.

Los chips también se prueban nuevamente después del empaquetado, ya que es posible que falten los cables de conexión o que el paquete pueda alterar el rendimiento analógico. Esto se conoce como la "prueba final". También se pueden obtener imágenes de los chips mediante rayos X.

Por lo general, las fábricas cobran por el tiempo de prueba, con precios del orden de centavos por segundo. Los tiempos de prueba varían desde unos pocos milisegundos hasta un par de segundos, y el software de prueba está optimizado para reducir el tiempo de prueba. También es posible realizar pruebas de múltiples chips (multisitio) porque muchos probadores tienen los recursos para realizar la mayoría o todas las pruebas en paralelo y en varios chips a la vez.

Los chips a menudo se diseñan con "características de capacidad de prueba", como cadenas de escaneo o una " autoprueba incorporada " para acelerar las pruebas y reducir los costos de las mismas. En ciertos diseños que utilizan procesos de fabricación analógicos especializados, las obleas también se recortan con láser durante las pruebas, para lograr valores de resistencia estrechamente distribuidos según lo especificado en el diseño.

Los buenos diseños intentan probar y gestionar estadísticamente las esquinas (extremos del comportamiento del silicio causados por una alta temperatura de funcionamiento combinada con los extremos de pasos de procesamiento fabulosos). La mayoría de los diseños tienen al menos 64 esquinas.

El rendimiento del dispositivo o del troquel es el número de chips o troqueles de trabajo en una oblea, expresado en porcentaje, ya que el número de chips en una oblea (Die per wafer, DPW) puede variar según el tamaño de los chips y el diámetro de la oblea. La degradación del rendimiento es una reducción del rendimiento, que históricamente fue causada principalmente por partículas de polvo; sin embargo, desde la década de 1990, la degradación del rendimiento es causada principalmente por la variación del proceso, el proceso en sí y las herramientas utilizadas en la fabricación de chips, aunque el polvo sigue siendo un problema en Muchas fábricas antiguas. Las partículas de polvo tienen un efecto cada vez mayor sobre el rendimiento a medida que los tamaños de las características se reducen con los procesos más nuevos. La automatización y el uso de mini entornos dentro de los equipos de producción, FOUP y SMIF, han permitido reducir los defectos causados por partículas de polvo. El rendimiento del dispositivo debe mantenerse alto para reducir el precio de venta de los chips en funcionamiento, ya que los chips en funcionamiento tienen que pagar por los chips que fallaron, y para reducir el costo del procesamiento de las obleas. El rendimiento también puede verse afectado por el diseño y funcionamiento de la fábrica.

Es necesario un control estricto de los contaminantes y del proceso de producción para aumentar el rendimiento. Los contaminantes pueden ser contaminantes químicos o partículas de polvo. Los "defectos mortales" son aquellos causados por partículas de polvo que provocan el fallo total del dispositivo (como un transistor). También existen defectos inofensivos. Una partícula debe tener 1/5 del tamaño de una característica para causar un defecto mortal. Entonces, si una característica tiene 100 nm de ancho, una partícula solo necesita tener 20 nm de ancho para causar un defecto mortal. La electricidad electrostática también puede afectar negativamente al rendimiento. Los contaminantes o impurezas químicas incluyen metales pesados como hierro, cobre, níquel, zinc, cromo, oro, mercurio y plata, metales alcalinos como sodio, potasio y litio, y elementos como aluminio, magnesio, calcio, cloro, azufre, carbono. y flúor. Es importante que estos elementos no queden en contacto con el silicio, ya que podrían reducir el rendimiento. Se pueden utilizar mezclas químicas para eliminar estos elementos del silicio; diferentes mezclas son efectivas contra diferentes elementos.

Se utilizan varios modelos para estimar el rendimiento. Son el modelo de Murphy, el modelo de Poisson, el modelo binomial, el modelo de Moore y el modelo de Seeds. No existe un modelo universal; se debe elegir un modelo en función de la distribución de rendimiento real (la ubicación de los chips defectuosos). Por ejemplo, el modelo de Murphy supone que la pérdida de rendimiento se produce más en los bordes de la oblea (los chips que no funcionan se concentran en los bordes de la oblea), El modelo de Poisson supone que los troqueles defectuosos están distribuidos de manera relativamente uniforme a lo largo de la oblea, y el modelo de Seeds supone que los troqueles defectuosos están agrupados. [119]

Los troqueles más pequeños cuestan menos de producir (ya que caben más en una oblea, y las obleas se procesan y se cotizan en su conjunto) y pueden ayudar a lograr mayores rendimientos, ya que los troqueles más pequeños tienen menos posibilidades de tener un defecto, debido a su menor área de superficie en la oblea. Sin embargo, los troqueles más pequeños requieren características más pequeñas para lograr las mismas funciones de los troqueles más grandes o superarlas, y las características más pequeñas requieren una variación reducida del proceso y una mayor pureza (reducción de la contaminación) para mantener altos rendimientos. Se utilizan herramientas de metrología para inspeccionar las obleas durante el proceso de producción y predecir el rendimiento, por lo que las obleas que se predice que tendrán demasiados defectos pueden desecharse para ahorrar en costos de procesamiento. [117]

Una vez probada, normalmente se reduce el grosor de una oblea en un proceso también conocido como "afilado", [120] "acabado posterior", "pulido posterior de oblea" o "adelgazamiento de oblea" [121] antes de marcar la oblea y luego dividirla en matrices individuales. , un proceso conocido como corte en cubitos de obleas . Sólo se empaquetan las patatas fritas buenas y sin marcar.

El embalaje de plástico o cerámica implica montar el troquel, conectar las almohadillas del troquel a las clavijas del paquete y sellar el troquel. Se utilizan pequeños cables de unión para conectar las almohadillas a los pines. En los "viejos tiempos" (década de 1970), los cables se unían a mano, pero ahora máquinas especializadas realizan la tarea. Tradicionalmente, estos cables estaban compuestos de oro, lo que conducía a un marco de plomo (pronunciado "marco leed") de cobre chapado en soldadura ; el plomo es venenoso, por lo que ahora RoHS exige "marcos de plomo" sin plomo .

El paquete a escala de chips (CSP) es otra tecnología de envasado. Un paquete de plástico doble en línea , como la mayoría de los paquetes, es muchas veces más grande que el troquel real escondido en su interior, mientras que los chips CSP son casi del tamaño del troquel; Se puede construir un CSP para cada dado antes de cortar la oblea.

Los chips empaquetados se vuelven a probar para garantizar que no sufrieron daños durante el embalaje y que la operación de interconexión entre matriz y pin se realizó correctamente. Luego, un láser graba el nombre y los números del chip en el paquete.

En el proceso de fabricación se utilizan muchos materiales tóxicos. [122] Estos incluyen:

Es vital que los trabajadores no estén expuestos directamente a estas sustancias peligrosas. El alto grado de automatización común en la industria de fabricación de circuitos integrados ayuda a reducir los riesgos de exposición. La mayoría de las instalaciones de fabricación emplean sistemas de gestión de gases de escape, como depuradores húmedos, cámaras de combustión, cartuchos absorbentes calentados, etc., para controlar el riesgo para los trabajadores y el medio ambiente.

La siguiente gran innovación en transistores fue la introducción de transistores FinFET (tri-gate) en la tecnología de 22 nm de Intel en 2011.

{{cite book}}: CS1 maint: bot: original URL status unknown (link)