En electrónica , los flip-flops y los latches son circuitos que tienen dos estados estables que pueden almacenar información de estado: un multivibrador biestable . Se puede hacer que el circuito cambie de estado mediante señales aplicadas a una o más entradas de control y emitirá su estado (a menudo junto con su complemento lógico también). Es el elemento de almacenamiento básico en la lógica secuencial . Los flip-flops y los latches son bloques de construcción fundamentales de los sistemas de electrónica digital utilizados en computadoras, comunicaciones y muchos otros tipos de sistemas.

Los flip-flops y los latches se utilizan como elementos de almacenamiento de datos para almacenar un solo bit (dígito binario) de datos; uno de sus dos estados representa un "uno" y el otro representa un "cero". Este tipo de almacenamiento de datos se puede utilizar para el almacenamiento de estados , y un circuito de este tipo se describe como lógica secuencial en electrónica. Cuando se utiliza en una máquina de estados finitos , la salida y el siguiente estado dependen no solo de su entrada actual, sino también de su estado actual (y, por lo tanto, de las entradas anteriores). También se puede utilizar para contar pulsos y para sincronizar señales de entrada de tiempo variable con alguna señal de tiempo de referencia.

El término flip-flop se ha referido históricamente de manera genérica tanto a circuitos disparados por nivel (asincrónicos, transparentes u opacos) como disparados por flanco ( sincrónicos o sincronizados ) que almacenan un solo bit de datos utilizando puertas . [1] Los autores modernos reservan el término flip-flop exclusivamente para elementos de almacenamiento disparados por flanco y pestillos para los disparados por nivel. [2] [3] Los términos "disparado por flanco" y "disparado por nivel" pueden usarse para evitar ambigüedades. [4]

Cuando se habilita un pestillo activado por nivel, se vuelve transparente, pero la salida de un flip-flop activado por borde solo cambia en un borde de reloj (ya sea positivo o negativo).

Existen distintos tipos de flip-flops y latches disponibles como circuitos integrados , generalmente con múltiples elementos por chip. Por ejemplo, el 74HC75 es un latch cuádruple transparente de la serie 7400 .

El primer pestillo electrónico fue inventado en 1918 por los físicos británicos William Eccles y FW Jordan . [5] [6] Inicialmente se llamó circuito disparador Eccles-Jordan y consistía en dos elementos activos ( tubos de vacío ). [7] El diseño se utilizó en la computadora de descifrado de códigos Colossus británica de 1943 [8] y tales circuitos y sus versiones transistorizadas eran comunes en las computadoras incluso después de la introducción de los circuitos integrados , aunque los pestillos y flip-flops hechos de puertas lógicas también son comunes ahora. [9] [10] Los primeros pestillos se conocían como circuitos disparadores o multivibradores .

Según PL Lindley, ingeniero del Laboratorio de Propulsión a Chorro de EE. UU ., los tipos de flip-flop detallados a continuación (SR, D, T, JK) se analizaron por primera vez en un curso de UCLA de 1954 sobre diseño de computadoras por Montgomery Phister, y luego aparecieron en su libro Logical Design of Digital Computers. [11] [12] Lindley trabajaba en ese momento en Hughes Aircraft con Eldred Nelson, quien había acuñado el término JK para un flip-flop que cambiaba de estado cuando ambas entradas estaban activadas (un "uno" lógico). Los otros nombres fueron acuñados por Phister. Difieren ligeramente de algunas de las definiciones que se dan a continuación. Lindley explica que escuchó la historia del flip-flop JK de Eldred Nelson, quien es responsable de acuñar el término mientras trabajaba en Hughes Aircraft. Los flip-flops que se usaban en Hughes en ese momento eran todos del tipo que llegó a conocerse como JK. Al diseñar un sistema lógico, Nelson asignó letras a las entradas de flip-flops de la siguiente manera: #1: A y B, #2: C y D, #3: E y F, #4: G y H, #5: J y K. Nelson utilizó las notaciones " j -input" y " k -input" en una solicitud de patente presentada en 1953. [13]

Se pueden construir pestillos transparentes o asincrónicos alrededor de un solo par de elementos inversores acoplados de forma cruzada: se han utilizado tubos de vacío , transistores bipolares , transistores de efecto de campo , inversores y puertas lógicas inversoras en circuitos prácticos.

Los flip-flops sincronizados están diseñados especialmente para sistemas sincrónicos; estos dispositivos ignoran sus entradas excepto en la transición de una señal de reloj dedicada (conocida como sincronización, pulsos o estrobismo). La sincronización hace que el flip-flop cambie o conserve su señal de salida en función de los valores de las señales de entrada en la transición. Algunos flip-flops cambian la salida en el flanco ascendente del reloj, otros en el flanco descendente.

Dado que las etapas amplificadoras elementales son inversoras, se pueden conectar dos etapas en sucesión (como una cascada) para formar el amplificador no inversor necesario. En esta configuración, cada amplificador puede considerarse como una red de retroalimentación inversora activa para el otro amplificador inversor. De este modo, las dos etapas están conectadas en un bucle no inversor, aunque el diagrama del circuito suele dibujarse como un par simétrico acoplado en cruz (ambos dibujos se introdujeron inicialmente en la patente de Eccles-Jordan).

Los flip-flops y los latches se pueden dividir en tipos comunes: SR ("set-reset"), D ("data"), T ("toggle") y JK (consulte la sección Historial anterior). El comportamiento de un tipo particular se puede describir mediante la ecuación característica que deriva la salida "próxima" ( Q next ) en términos de la(s) señal(es) de entrada y/o la salida actual, .

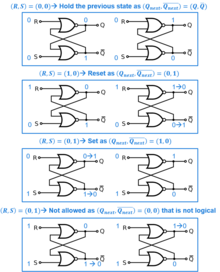

Al utilizar puertas estáticas como bloques de construcción, el pestillo más fundamental es el pestillo asincrónico Set-Reset (SR) .

Sus dos entradas S y R pueden establecer el estado interno en 1 usando la combinación S=1 y R=0, y pueden restablecer el estado interno a 0 usando la combinación S=0 y R=1. [nota 1]

El latch SR se puede construir a partir de un par de puertas lógicas NOR o NAND acopladas de forma cruzada . El bit almacenado está presente en la salida marcada como Q.

Es conveniente pensar en NAND, NOR, AND y OR como operaciones controladas, donde una entrada se elige como el conjunto de entrada de control y el otro bit como la entrada a procesar dependiendo del estado del control. Entonces, todas estas puertas tienen un valor de control que ignora la entrada (x) y genera un valor constante, mientras que el otro valor de control deja pasar la entrada (quizás complementada):

Básicamente, todos pueden usarse como interruptores que establecen un valor específico o dejan pasar un valor de entrada.

El latch SR NOR consta de dos puertas NOR paralelas donde la salida de cada NOR también se distribuye en abanico en una entrada del otro NOR, como se muestra en la figura. Llamamos entradas de retroalimentación , o simplemente retroalimentación a estas conexiones de salida a entrada. Las entradas restantes las usaremos como entradas de control como se explicó anteriormente. Observe que en este punto, debido a que todo es simétrico, no importa a qué entradas estén conectadas las salidas. Ahora rompemos la simetría al elegir cuál de las entradas de control restantes será nuestro set y reset y podemos llamar "set NOR" a la puerta NOR con el control set y "reset NOR" a la NOR con el control reset; en las figuras, el NOR set es el de abajo y el NOR reset es el de arriba. La salida del NOR reset será nuestro bit almacenado Q, mientras que veremos que la salida del NOR set almacena su complemento Q.

Para derivar el comportamiento del latch SR NOR, considere S y R como entradas de control y recuerde que, de las ecuaciones anteriores, establecer y restablecer NOR con control 1 fijará sus salidas a 0, mientras que establecer y restablecer NOR con control 0 actuará como una compuerta NOT. Con esto ahora es posible derivar el comportamiento del latch SR como condiciones simples (en lugar de, por ejemplo, asignar valores a cada línea, vea cómo se propagan):

Nota: X significa que no importa , es decir, 0 o 1 es un valor válido.

La combinación R = S = 1 se denomina combinación restringida o estado prohibido porque, como ambas puertas NOR generan ceros, se rompe la ecuación lógica Q = no Q. La combinación también es inadecuada en circuitos donde ambas entradas pueden pasar a estado bajo simultáneamente (es decir, una transición de restringido a estado de retención ). La salida podría permanecer en un estado metaestable y eventualmente bloquearse en 1 o 0 dependiendo de las relaciones de tiempo de propagación entre las puertas (una condición de carrera ).

Para superar la combinación restringida, se pueden agregar puertas a las entradas que se convertirían (S, R) = (1, 1)en una de las combinaciones no restringidas. Esto puede ser:

Esto se hace en casi todos los controladores lógicos programables .

Como alternativa, se puede hacer que la combinación restringida alterne la salida. El resultado es el pestillo JK.

La ecuación característica del pestillo SR es:

donde A + B significa (A o B), AB significa (A y B)

Otra expresión es:

El circuito que se muestra a continuación es un circuito de bloqueo NAND básico. Las entradas también se designan generalmente como S y R para establecer y restablecer respectivamente. Debido a que las entradas NAND normalmente deben ser lógicas 1 para evitar afectar la acción de bloqueo, se considera que las entradas están invertidas en este circuito (o activas en nivel bajo).

El circuito utiliza la misma retroalimentación que SR NOR, solo que reemplaza las puertas NOR por puertas NAND, para "recordar" y retener su estado lógico incluso después de que las señales de entrada de control hayan cambiado. Nuevamente, recuerde que una NAND controlada por 1 siempre genera 0, mientras que una NAND controlada por 0 actúa como una puerta NOT. Cuando las entradas S y R son altas, la retroalimentación mantiene las salidas Q en el estado anterior. Cuando una es cero, fijan sus bits de salida en 0 mientras que la otra se adapta al complemento. S=R=0 produce el estado inválido.

Desde un punto de vista didáctico, los latches SR dibujados como un par de componentes acoplados de forma cruzada (transistores, compuertas, tubos, etc.) suelen ser difíciles de entender para los principiantes. Una explicación didácticamente más sencilla es dibujar el latch como un único bucle de retroalimentación en lugar del acoplamiento cruzado. El siguiente es un latch SR construido con una compuerta AND con una entrada invertida y una compuerta OR . Tenga en cuenta que el inversor no es necesario para la funcionalidad del latch, sino para hacer que ambas entradas sean de alta actividad.

Tenga en cuenta que el pestillo SR AND-OR tiene la ventaja de que S = 1, R = 1 está bien definido. En la versión anterior del pestillo SR AND-OR, se da prioridad a la señal R sobre la señal S. Si se necesita prioridad de S sobre R, esto se puede lograr conectando la salida Q a la salida de la compuerta OR en lugar de a la salida de la compuerta AND.

El latch SR AND-OR es más fácil de entender, porque ambas puertas se pueden explicar de forma aislada, de nuevo con la vista de control de AND y OR de arriba. Cuando no se establece ni S ni R, entonces tanto la puerta OR como la puerta AND están en "modo de retención", es decir, dejan pasar la entrada, su salida es la entrada del bucle de retroalimentación. Cuando la entrada S = 1, entonces la puerta OR genera 1, independientemente de la otra entrada del bucle de retroalimentación ("modo de ajuste"). Cuando la entrada R = 1, entonces la puerta AND genera 0, independientemente de la otra entrada del bucle de retroalimentación ("modo de reinicio"). Y dado que la puerta AND toma la salida de la puerta OR como entrada, R tiene prioridad sobre S. Los latches dibujados como puertas acopladas cruzadamente pueden parecer menos intuitivos, ya que el comportamiento de una puerta parece estar entrelazado con el de la otra puerta. Los latches NOR o NAND estándar también se podrían volver a dibujar con el bucle de retroalimentación, pero en su caso el bucle de retroalimentación no muestra el mismo valor de señal en todo el bucle de retroalimentación. Sin embargo, el latch SR AND-OR tiene el inconveniente de que necesitaría un inversor adicional, si se necesita una salida Q invertida.

Nótese que el latch SR AND-OR se puede transformar en el latch SR NOR usando transformaciones lógicas: invirtiendo la salida de la compuerta OR y también la segunda entrada de la compuerta AND y conectando la salida Q invertida entre estos dos inversores agregados; siendo la compuerta AND con ambas entradas invertidas equivalente a una compuerta NOR según las leyes de De Morgan .

El latch JK se utiliza con mucha menos frecuencia que el flip-flop JK. El latch JK sigue la siguiente tabla de estados:

Por lo tanto, el latch JK es un latch SR que está diseñado para alternar su salida (oscilar entre 0 y 1) cuando se le pasa la combinación de entrada de 11. [16] A diferencia del flip-flop JK, la combinación de entrada 11 para el latch JK no es muy útil porque no hay un reloj que dirija la alternancia. [17]

Los latches están diseñados para ser transparentes. Es decir, los cambios en la señal de entrada provocan cambios inmediatos en la salida. Se puede añadir lógica adicional a un latch transparente para que no sea transparente u opaco cuando no se activa otra entrada (una entrada "habilitada"). Cuando varios latches transparentes se suceden uno tras otro, si todos son transparentes al mismo tiempo, las señales se propagarán a través de todos ellos. Sin embargo, después de un latch transparente alto hay un latch transparente bajo (o viceversa) que provoca que el estado y la salida solo cambien en los flancos del reloj, formando lo que se denomina un flip-flop maestro-esclavo .

Se puede crear un latch SR con compuerta agregando un segundo nivel de compuertas NAND a un latch SR invertido . Las compuertas NAND adicionales invierten aún más las entradas, de modo que un latch SR se convierte en un latch SR con compuerta (un latch SR se transformaría en un latch SR con compuerta con habilitación invertida).

Como alternativa, se puede crear un pestillo SR con compuerta (con habilitación no inversora) agregando un segundo nivel de compuertas AND a un pestillo SR .

Con E alto ( habilitar verdadero), las señales pueden pasar a través de las puertas de entrada al pestillo encapsulado; todas las combinaciones de señales excepto (0, 0) = se mantienen y luego se reproducen inmediatamente en la salida (Q, Q ), es decir, el pestillo es transparente .

Con E bajo ( habilitar falso) el pestillo se cierra (opaco) y permanece en el estado en el que estaba la última vez que E estaba alto.

Una señal de entrada de habilitación periódica puede denominarse señal de escritura . Cuando la entrada de habilitación es una señal de reloj , se dice que el pestillo es sensible al nivel (al nivel de la señal de reloj), a diferencia de los flip-flops que se muestran a continuación.

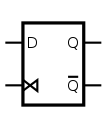

Este latch explota el hecho de que, en las dos combinaciones de entrada activas (01 y 10) de un latch SR con compuerta, R es el complemento de S. La etapa NAND de entrada convierte los dos estados de entrada D (0 y 1) a estas dos combinaciones de entrada para el siguiente latch SR invirtiendo la señal de entrada de datos. El estado bajo de la señal de habilitación produce la combinación inactiva "11". Por lo tanto, un latch D con compuerta puede considerarse como un latch SR sincrónico de una entrada . Esta configuración evita la aplicación de la combinación de entrada restringida. También se conoce como latch transparente , latch de datos o simplemente latch con compuerta . Tiene una entrada de datos y una señal de habilitación (a veces denominada reloj o control ). La palabra transparente proviene del hecho de que, cuando la entrada de habilitación está activada, la señal se propaga directamente a través del circuito, desde la entrada D a la salida Q. Los latches D con compuerta también son sensibles al nivel con respecto al nivel del reloj o la señal de habilitación.

Los pestillos transparentes se utilizan normalmente como puertos de E/S o en sistemas asincrónicos o en sistemas bifásicos sincrónicos ( sistemas sincrónicos que utilizan un reloj de dos fases ), donde dos pestillos que funcionan en diferentes fases de reloj impiden la transparencia de los datos como en un flip-flop maestro-esclavo.

La tabla de verdad que aparece a continuación muestra que cuando la entrada de habilitación/ reloj es 0, la entrada D no tiene efecto en la salida. Cuando E/C es alta, la salida es igual a D.

Los diseños clásicos de pestillo con compuerta tienen algunas características indeseables. [18] Requieren lógica de doble riel o un inversor. La propagación de entrada a salida puede requerir hasta tres retardos de compuerta. La propagación de entrada a salida no es constante: algunas salidas requieren dos retardos de compuerta mientras que otras requieren tres.

Los diseñadores buscaron alternativas. [19] Una alternativa exitosa es el latch Earle. Requiere solamente una entrada de datos y su salida requiere dos retardos de compuerta constantes. Además, los dos niveles de compuerta del latch Earle pueden, en algunos casos, fusionarse con los dos últimos niveles de compuerta de los circuitos que controlan el latch porque muchos circuitos computacionales comunes tienen una capa OR seguida de una capa AND como sus dos últimos niveles. La fusión de la función del latch puede implementar el latch sin retardos de compuerta adicionales. [18] La fusión se explota comúnmente en el diseño de computadoras segmentadas y, de hecho, fue desarrollada originalmente por John G. Earle para ser utilizada en el IBM System/360 Model 91 para ese propósito. [20]

El pestillo Earle no presenta riesgos. [21] Si se omite la puerta NAND central, se obtiene el pestillo de retención de polaridad , que se utiliza comúnmente porque requiere menos lógica. [21] [22] Sin embargo, es susceptible a riesgos lógicos. Sesgar intencionalmente la señal del reloj puede evitar el riesgo. [22]

El flip-flop D es un dispositivo muy utilizado y conocido como flip-flop de "datos". El flip-flop D captura el valor de la entrada D en una parte definida del ciclo de reloj (como el flanco ascendente del reloj). Ese valor capturado se convierte en la salida Q. En otros momentos, la salida Q no cambia. [23] [24] El flip-flop D puede considerarse como una celda de memoria, un dispositivo de retención de orden cero o una línea de retardo . [25]

Tabla de verdad:

( X denota una condición de no importancia , lo que significa que la señal es irrelevante)

La mayoría de los flip-flops de tipo D en los circuitos integrados tienen la capacidad de ser forzados al estado de activación o desactivación (que ignora las entradas D y de reloj), de forma muy similar a un flip-flop SR. Por lo general, la condición ilegal S = R = 1 se resuelve en los flip-flops de tipo D. Al configurar S = R = 0, el flip-flop se comporta como se describió anteriormente. Aquí se muestra la tabla de verdad para las otras configuraciones posibles de S y R:

Estos flip-flops son muy útiles, ya que forman la base de los registros de desplazamiento , que son una parte esencial de muchos dispositivos electrónicos. La ventaja del flip-flop D sobre el "latch transparente" de tipo D es que la señal en el pin de entrada D se captura en el momento en que se activa el reloj del flip-flop, y los cambios posteriores en la entrada D se ignorarán hasta el siguiente evento de reloj. Una excepción es que algunos flip-flops tienen una entrada de señal de "reinicio", que restablecerá Q (a cero), y puede ser asincrónica o sincrónica con el reloj.

El circuito anterior desplaza el contenido del registro hacia la derecha, una posición de bit en cada transición activa del reloj. La entrada X se desplaza hacia la posición de bit más a la izquierda.

Este circuito [26] consta de dos etapas implementadas por pestillos SR NAND. La etapa de entrada (los dos pestillos de la izquierda) procesa las señales de reloj y datos para asegurar señales de entrada correctas para la etapa de salida (el pestillo único de la derecha). Si el reloj está bajo, ambas señales de salida de la etapa de entrada están altas independientemente de la entrada de datos; el pestillo de salida no se ve afectado y almacena el estado anterior. Cuando la señal de reloj cambia de baja a alta, solo uno de los voltajes de salida (dependiendo de la señal de datos) se vuelve bajo y establece/reinicia el pestillo de salida: si D = 0, la salida inferior se vuelve baja; si D = 1, la salida superior se vuelve baja. Si la señal de reloj continúa manteniéndose alta, las salidas mantienen sus estados independientemente de la entrada de datos y fuerzan al pestillo de salida a permanecer en el estado correspondiente ya que el cero lógico de entrada (de la etapa de salida) permanece activo mientras el reloj está alto. Por lo tanto, el papel del pestillo de salida es almacenar los datos solo mientras el reloj está bajo.

El circuito está estrechamente relacionado con el latch D con compuerta, ya que ambos circuitos convierten los dos estados de entrada D (0 y 1) en dos combinaciones de entrada (01 y 10) para el latch SR de salida invirtiendo la señal de entrada de datos (ambos circuitos dividen la señal D única en dos señales S y R complementarias ). La diferencia es que en el latch D con compuerta se utilizan compuertas lógicas NAND, mientras que en el flip-flop D activado por flanco positivo se utilizan compuertas NAND SR . La función de estos latches es "bloquear" la salida activa produciendo un voltaje bajo (un cero lógico); por lo tanto, el flip-flop D activado por flanco positivo también se puede considerar como un latch D con compuerta con compuertas de entrada bloqueadas.

Un flip-flop D maestro-esclavo se crea conectando dos latches D con compuerta en serie e invirtiendo la entrada de habilitación de uno de ellos. Se llama maestro-esclavo porque el latch maestro controla el valor de salida Q del latch esclavo y obliga al latch esclavo a mantener su valor siempre que el latch esclavo esté habilitado, ya que el latch esclavo siempre copia su nuevo valor del latch maestro y cambia su valor solo en respuesta a un cambio en el valor del latch maestro y la señal de reloj.

En el caso de un flip-flop D maestro-esclavo activado por flanco positivo, cuando la señal de reloj es baja (0 lógico), la "habilitación" vista por el primer latch D o "maestro" (la señal de reloj invertida) es alta (1 lógico). Esto permite que el latch "maestro" almacene el valor de entrada cuando la señal de reloj pasa de baja a alta. A medida que la señal de reloj pasa a alta (0 a 1), la "habilitación" invertida del primer latch pasa a baja (1 a 0) y el valor visto en la entrada del latch maestro se "bloquea". Casi simultáneamente, la "habilitación" invertida dos veces del segundo latch D o "esclavo" pasa de baja a alta (0 a 1) con la señal de reloj. Esto permite que la señal capturada en el flanco ascendente del reloj por el latch maestro ahora "bloqueado" pase a través del latch "esclavo". Cuando la señal del reloj vuelve a baja (1 a 0), la salida del pestillo "esclavo" se "bloquea" y el valor visto en el último borde ascendente del reloj se mantiene mientras el pestillo "maestro" comienza a aceptar nuevos valores en preparación para el próximo borde ascendente del reloj.

Al quitar el inversor situado más a la izquierda del circuito se crea un flip-flop de tipo D que se activa con el flanco descendente de una señal de reloj. Esto tiene una tabla de verdad como la siguiente:

Los flip-flops que leen un nuevo valor en el flanco ascendente y descendente del reloj se denominan flip-flops de doble activación por flanco. Un flip-flop de este tipo se puede construir utilizando dos flip-flops de tipo D de activación por flanco único y un multiplexor, o utilizando dos flip-flops de tipo D de activación por flanco único y tres puertas XOR.

Se puede crear una alternativa funcional eficiente a un flip-flop D con circuitos dinámicos (donde la información se almacena en una capacitancia) siempre que se active con la suficiente frecuencia; aunque no es un flip-flop verdadero, se lo sigue llamando flip-flop por su función. Si bien el elemento D maestro-esclavo se activa en el borde de un reloj, sus componentes se activan cada uno por niveles de reloj. El "flip-flop D activado por borde", como se lo llama, aunque no es un flip-flop verdadero, no tiene las propiedades de maestro-esclavo.

Los flip-flops D activados por flanco se suelen implementar en operaciones integradas de alta velocidad que utilizan lógica dinámica . Esto significa que la salida digital se almacena en la capacitancia parásita del dispositivo mientras el dispositivo no está en transición. Este diseño facilita el restablecimiento simplemente descargando uno o más nodos internos. Una variedad común de flip-flop dinámico es el tipo de reloj monofásico verdadero (TSPC) que realiza la operación de flip-flop con poca energía y a altas velocidades. Sin embargo, los flip-flops dinámicos normalmente no funcionarán a velocidades de reloj estáticas o bajas: con suficiente tiempo, las rutas de fuga pueden descargar la capacitancia parásita lo suficiente como para hacer que el flip-flop entre en estados no válidos.

Si la entrada T es alta, el flip-flop T cambia de estado ("alterna") cada vez que se activa la entrada de reloj. Si la entrada T es baja, el flip-flop mantiene el valor anterior. Este comportamiento se describe mediante la ecuación característica :

y se puede describir en una tabla de verdad :

Cuando T se mantiene alto, el flip-flop de conmutación divide la frecuencia de reloj por dos; es decir, si la frecuencia de reloj es de 4 MHz, la frecuencia de salida obtenida del flip-flop será de 2 MHz. Esta característica de "división por" tiene aplicación en varios tipos de contadores digitales . El flip-flop AT también se puede construir utilizando un flip-flop JK (los pines J y K están conectados entre sí y actúan como T) o un flip-flop D (la entrada T XOR Q anterior controla la entrada D).

El flip-flop JK, aumenta el comportamiento del flip-flop SR (J: Set, K: Reset) interpretando la condición J = K = 1 como un comando de "flip" o de conmutación. Específicamente, la combinación J = 1, K = 0 es un comando para configurar el flip-flop; la combinación J = 0, K = 1 es un comando para restablecer el flip-flop; y la combinación J = K = 1 es un comando para conmutar el flip-flop, es decir, cambiar su salida al complemento lógico de su valor actual. Establecer J = K = 0 mantiene el estado actual. Para sintetizar un flip-flop D, simplemente establezca K igual al complemento de J (la entrada J actuará como entrada D). De manera similar, para sintetizar un flip-flop T, establezca K igual a J. El flip-flop JK es, por lo tanto, un flip-flop universal, porque se puede configurar para funcionar como un flip-flop SR, un flip-flop D o un flip-flop T.

La ecuación característica del flip-flop JK es:

y la tabla de verdad correspondiente es:

La entrada debe mantenerse constante en un período alrededor del borde ascendente del reloj conocido como apertura. Imagine tomar una fotografía de una rana en una hoja de nenúfar. [28] Suponga que la rana luego salta al agua. Si toma una fotografía de la rana mientras salta al agua, obtendrá una imagen borrosa de la rana saltando al agua: no está claro en qué estado estaba la rana. Pero si toma una fotografía mientras la rana se sienta firmemente en la hoja (o está firmemente en el agua), obtendrá una imagen clara. De la misma manera, la entrada a una chancla debe mantenerse constante durante la apertura de la chancla.

El tiempo de configuración es la cantidad mínima de tiempo que la entrada de datos debe mantenerse estable antes del evento del reloj, para que el reloj muestre los datos de manera confiable.

El tiempo de retención es la cantidad mínima de tiempo que la entrada de datos debe mantenerse estable después del evento del reloj, para que el reloj muestree los datos de manera confiable.

La apertura es la suma del tiempo de configuración y de retención. La entrada de datos debe mantenerse constante durante este período de tiempo. [28]

El tiempo de recuperación es el tiempo mínimo que la entrada de configuración o restablecimiento asincrónico debe estar inactiva antes del evento de reloj, de modo que el reloj muestre los datos de manera confiable. El tiempo de recuperación para la entrada de configuración o restablecimiento asincrónico es, por lo tanto, similar al tiempo de configuración para la entrada de datos.

El tiempo de eliminación es el tiempo mínimo que la entrada de configuración o restablecimiento asincrónico debe estar inactiva después del evento de reloj, de modo que el reloj muestre los datos de manera confiable. El tiempo de eliminación de la entrada de configuración o restablecimiento asincrónico es, por lo tanto, similar al tiempo de retención de la entrada de datos.

Los impulsos cortos aplicados a entradas asincrónicas (activación, restablecimiento) no deben aplicarse completamente dentro del período de recuperación-eliminación, o de lo contrario se vuelve completamente indeterminable si el flip-flop pasará al estado apropiado. En otro caso, donde una señal asincrónica simplemente realiza una transición que cae entre el tiempo de recuperación/eliminación, eventualmente el flip-flop pasará al estado apropiado, pero puede aparecer o no un fallo muy breve en la salida, dependiendo de la señal de entrada sincrónica. Esta segunda situación puede tener o no importancia para el diseño de un circuito.

Las señales de ajuste y reinicio (y otras) pueden ser sincrónicas o asincrónicas y, por lo tanto, pueden caracterizarse con tiempos de configuración/retención o de recuperación/eliminación, y la sincronicidad depende en gran medida del diseño del flip-flop.

La diferenciación entre los tiempos de configuración/retención y recuperación/eliminación suele ser necesaria al verificar la sincronización de circuitos más grandes, ya que las señales asincrónicas pueden resultar menos críticas que las señales sincrónicas. La diferenciación ofrece a los diseñadores de circuitos la capacidad de definir las condiciones de verificación para estos tipos de señales de forma independiente.

Los flip-flops están sujetos a un problema llamado metaestabilidad , que puede ocurrir cuando dos entradas, como datos y reloj o reloj y reinicio, están cambiando aproximadamente al mismo tiempo. Cuando el orden no es claro, dentro de las restricciones de tiempo apropiadas, el resultado es que la salida puede comportarse de manera impredecible, tardando mucho más de lo normal en establecerse en un estado u otro, o incluso oscilando varias veces antes de estabilizarse. Teóricamente, el tiempo para estabilizarse no está acotado. En un sistema informático , esta metaestabilidad puede causar corrupción de datos o un bloqueo del programa si el estado no es estable antes de que otro circuito use su valor; en particular, si dos caminos lógicos diferentes usan la salida de un flip-flop, un camino puede interpretarlo como un 0 y el otro como un 1 cuando no se ha resuelto al estado estable, poniendo a la máquina en un estado inconsistente. [29]

La metaestabilidad en los flip-flops se puede evitar si se garantiza que las entradas de datos y de control se mantengan válidas y constantes durante períodos específicos antes y después del pulso de reloj, llamados tiempo de configuración (t su ) y tiempo de retención (t h ) respectivamente. Estos tiempos se especifican en la hoja de datos del dispositivo y, por lo general, oscilan entre unos pocos nanosegundos y unos pocos cientos de picosegundos en el caso de los dispositivos modernos. Según la organización interna del flip-flop, es posible construir un dispositivo con un requisito de tiempo de configuración o de retención cero (o incluso negativo), pero no ambos simultáneamente.

Desafortunadamente, no siempre es posible cumplir con los criterios de configuración y retención, porque el flip-flop puede estar conectado a una señal en tiempo real que podría cambiar en cualquier momento, fuera del control del diseñador. En este caso, lo mejor que puede hacer el diseñador es reducir la probabilidad de error a un cierto nivel, dependiendo de la confiabilidad requerida del circuito. Una técnica para suprimir la metaestabilidad es conectar dos o más flip-flops en una cadena, de modo que la salida de cada uno alimente la entrada de datos del siguiente, y todos los dispositivos compartan un reloj común. Con este método, la probabilidad de un evento metaestable se puede reducir a un valor insignificante, pero nunca a cero. La probabilidad de metaestabilidad se acerca cada vez más a cero a medida que aumenta el número de flip-flops conectados en serie. El número de flip-flops que se conectan en cascada se conoce como "clasificación"; los flip-flops de "doble clasificación" (dos flip-flops en serie) son una situación común.

Existen los llamados flip-flops reforzados con metaestable, que funcionan reduciendo los tiempos de configuración y de retención tanto como sea posible, pero ni siquiera estos pueden eliminar el problema por completo. Esto se debe a que la metaestabilidad es más que una simple cuestión de diseño de circuitos. Cuando las transiciones en el reloj y los datos están muy cerca en el tiempo, el flip-flop se ve obligado a decidir qué evento ocurrió primero. Por más rápido que se construya el dispositivo, siempre existe la posibilidad de que los eventos de entrada estén tan cerca entre sí que no pueda detectar cuál ocurrió primero. Por lo tanto, es lógicamente imposible construir un flip-flop perfectamente a prueba de metaestable. Los flip-flops a veces se caracterizan por un tiempo máximo de establecimiento (el tiempo máximo que permanecerán metaestables en condiciones específicas). En este caso, los flip-flops de doble rango que tienen una frecuencia de reloj más lenta que el tiempo máximo permitido de metaestabilidad proporcionarán el acondicionamiento adecuado para señales asincrónicas (por ejemplo, externas).

Otro valor de tiempo importante para un flip-flop es el retardo de reloj a salida (símbolo común en las hojas de datos: t CO ) o retardo de propagación (t P ), que es el tiempo que tarda un flip-flop en cambiar su salida después del flanco del reloj. El tiempo para una transición de alto a bajo (t PHL ) a veces es diferente del tiempo para una transición de bajo a alto (t PLH ).

Cuando se conectan en cascada flip-flops que comparten el mismo reloj (como en un registro de desplazamiento ), es importante asegurarse de que el t CO del flip-flop anterior sea mayor que el tiempo de retención (t h ) del flip-flop siguiente, de modo que los datos presentes en la entrada del flip-flop siguiente se "desplacen hacia adentro" correctamente siguiendo el flanco activo del reloj. Esta relación entre t CO y t h normalmente está garantizada si los flip-flops son físicamente idénticos. Además, para un funcionamiento correcto, es fácil verificar que el período del reloj debe ser mayor que la suma t su + t h .

Los flip-flops se pueden generalizar de al menos dos maneras: haciéndolos 1 de N en lugar de 1 de 2, y adaptándolos a la lógica con más de dos estados. En los casos especiales de codificación 1 de 3, o lógica ternaria multivaluada , un elemento de este tipo puede denominarse flip-flap-flop . [30]

En un flip-flop convencional, exactamente una de las dos salidas complementarias es alta. Esto se puede generalizar a un elemento de memoria con N salidas, exactamente una de las cuales es alta (alternativamente, donde exactamente una de N es baja). Por lo tanto, la salida es siempre una representación de uno caliente (respectivamente uno frío ). La construcción es similar a un flip-flop de acoplamiento cruzado convencional; cada salida, cuando es alta, inhibe todas las demás salidas. [31] Alternativamente, se pueden utilizar flip-flops más o menos convencionales, uno por salida, con circuitos adicionales para asegurarse de que solo uno a la vez pueda ser verdadero. [32]

Otra generalización del flip-flop convencional es un elemento de memoria para lógica multivalor . En este caso, el elemento de memoria retiene exactamente uno de los estados lógicos hasta que las entradas de control inducen un cambio. [33] Además, también se puede utilizar un reloj multivalor, lo que da lugar a nuevas posibles transiciones de reloj. [34]

{{cite book}}: |journal=ignorado ( ayuda )