La memoria de cambio de fase (también conocida como PCM , PCME , PRAM , PCRAM , OUM ( memoria unificada ovónica ) y C-RAM o CRAM ( RAM de calcogenuro )) es un tipo de memoria de acceso aleatorio no volátil . Las PRAM explotan el comportamiento único del vidrio de calcogenuro . En PCM, el calor producido por el paso de una corriente eléctrica a través de un elemento calefactor generalmente hecho de nitruro de titanio se utiliza para calentar y enfriar rápidamente el vidrio, volviéndolo amorfo , o para mantenerlo en su rango de temperatura de cristalización durante algún tiempo, cambiándolo así a un estado cristalino . [1] PCM también tiene la capacidad de lograr una serie de estados intermedios distintos, por lo que tiene la capacidad de mantener múltiples bits en una sola celda, [2] pero las dificultades para programar celdas de esta manera han impedido que estas capacidades se implementen en otras tecnologías (sobre todo la memoria flash ) con la misma capacidad.

Las investigaciones recientes sobre PCM se han dirigido a intentar encontrar alternativas viables al material de cambio de fase Ge2Sb2Te5 ( GST ) , con resultados dispares. Otras investigaciones se han centrado en el desarrollo de una superred GeTe - Sb2Te3 para lograr cambios de fase no térmicos modificando el estado de coordinación de los átomos de germanio con un pulso láser . Esta nueva memoria de cambio de fase interfacial (IPCM) ha tenido muchos éxitos y sigue siendo objeto de mucha investigación activa. [3]

Leon Chua ha sostenido que todos los dispositivos de memoria no volátil de dos terminales , incluido el PCM, deberían considerarse memristores . [4] Stan Williams de HP Labs también ha sostenido que el PCM debería considerarse un memristor. [5] Sin embargo, esta terminología ha sido cuestionada y la posible aplicabilidad de la teoría del memristor a cualquier dispositivo físicamente realizable está abierta a dudas. [6] [7]

En la década de 1960, Stanford R. Ovshinsky de Energy Conversion Devices exploró por primera vez las propiedades de los vidrios de calcogenuro como una posible tecnología de memoria. En 1969, Charles Sie publicó una disertación en la Universidad Estatal de Iowa que describía y demostraba la viabilidad de un dispositivo de memoria de cambio de fase mediante la integración de una película de calcogenuro con una matriz de diodos . [8] [9] Un estudio cinematográfico de 1970 estableció que el mecanismo de memoria de cambio de fase en el vidrio de calcogenuro implica el crecimiento de filamentos cristalinos inducido por un campo eléctrico . [10] [11] En la edición de septiembre de 1970 de Electronics , Gordon Moore , cofundador de Intel , publicó un artículo sobre la tecnología. [12] Sin embargo, la calidad del material y los problemas de consumo de energía impidieron la comercialización de la tecnología. Más recientemente, el interés y la investigación se han reanudado ya que se espera que las tecnologías de memoria flash y DRAM encuentren dificultades de escalabilidad a medida que se reduzca la litografía de chips . [13]

Los estados cristalino y amorfo del vidrio de calcogenuro tienen valores de resistividad eléctrica radicalmente diferentes. El estado amorfo, de alta resistencia, representa un 0 binario , mientras que el estado cristalino, de baja resistencia, representa un 1. [ cita requerida ] El calcogenuro es el mismo material que se utiliza en los medios ópticos regrabables (como CD-RW y DVD-RW ). En esos casos, se manipulan las propiedades ópticas del material, en lugar de su resistividad eléctrica, ya que el índice de refracción del calcogenuro también cambia con el estado del material.

Aunque la PRAM aún no ha alcanzado la etapa de comercialización para dispositivos electrónicos de consumo, casi todos los dispositivos prototipo utilizan una aleación de calcogenuro de germanio (Ge), antimonio (Sb) y telurio (Te) llamada GeSbTe (GST). La estequiometría , o la relación de elementos Ge:Sb:Te, es 2:2:5 en GST. Cuando el GST se calienta a una temperatura alta (más de 600 °C), su cristalinidad de calcogenuro se pierde. Una vez enfriado, se congela en un estado amorfo similar al vidrio [14] y su resistencia eléctrica es alta. Al calentar el calcogenuro a una temperatura por encima de su punto de cristalización , pero por debajo del punto de fusión , se transformará en un estado cristalino con una resistencia mucho menor. El tiempo para completar esta transición de fase depende de la temperatura. Las partes más frías del calcogenuro tardan más en cristalizar, y las partes sobrecalentadas pueden volver a fundirse. Generalmente se utiliza una escala de tiempo de cristalización del orden de 100 ns . [15] Este tiempo es mayor que el de los dispositivos de memoria volátil convencionales, como la DRAM moderna , que tienen un tiempo de conmutación del orden de dos nanosegundos. Sin embargo, una solicitud de patente de Samsung Electronics de enero de 2006 indica que la PRAM puede alcanzar tiempos de conmutación de hasta cinco nanosegundos.

Un avance de 2008 iniciado por Intel y ST Microelectronics permitió controlar con más cuidado el estado del material, lo que permitió transformarlo en uno de cuatro estados distintos: los estados amorfos o cristalinos anteriores, junto con dos nuevos estados parcialmente cristalinos. Cada uno de estos estados tiene diferentes propiedades eléctricas que se pueden medir durante las lecturas, lo que permite que una sola celda represente dos bits , duplicando la densidad de memoria . [16]

Los dispositivos de memoria de cambio de fase basados en germanio , antimonio y telurio presentan desafíos de fabricación, ya que el grabado y pulido del material con calcógenos puede cambiar la composición del material. Los materiales basados en aluminio y antimonio son más estables térmicamente que el GeSbTe . Al 50 Sb 50 tiene tres niveles de resistencia distintos, lo que ofrece el potencial de almacenar tres bits de datos en dos celdas en lugar de dos (nueve estados posibles para el par de celdas, utilizando ocho de esos estados se obtiene log 2 8 = 3 bits). [17] [18]

El tiempo de conmutación de la PRAM y su escalabilidad inherente [19] la hacen más atractiva que la memoria flash . La sensibilidad a la temperatura de la PRAM es quizás su inconveniente más notable, que puede requerir cambios en el proceso de producción de los fabricantes que incorporen la tecnología.

La memoria flash funciona modulando la carga ( electrones ) almacenada dentro de la compuerta de un transistor MOS . La compuerta está construida con una "pila" especial diseñada para atrapar cargas (ya sea en una compuerta flotante o en "trampas" aislantes ). La presencia de carga dentro de la compuerta aumenta o disminuye el voltaje umbral del transistor, lo que corresponde a un cambio en el estado del bit de la celda de 1 a 0 o de 0 a 1. Cambiar el estado del bit requiere eliminar la carga acumulada, lo que demanda un voltaje relativamente grande para "succionar" los electrones de la compuerta flotante. Esta ráfaga de voltaje es proporcionada por una bomba de carga , que tarda un tiempo en acumular energía. Los tiempos de escritura generales para dispositivos flash comunes son del orden de 100 μs (para un bloque de datos), aproximadamente 10 000 veces el tiempo de lectura típico de 10 ns para SRAM, por ejemplo (para un byte ). [ cita requerida ]

La PRAM puede ofrecer un rendimiento mucho mayor en aplicaciones en las que escribir rápidamente es importante, tanto porque el elemento de memoria se puede cambiar más rápidamente como porque los bits individuales se pueden cambiar a 1 o 0 sin necesidad de borrar primero un bloque completo de celdas. El alto rendimiento de la PRAM, miles de veces más rápido que los discos duros convencionales , la hace particularmente interesante en funciones de memoria no volátil cuyo rendimiento actualmente está limitado por el tiempo de acceso a la memoria.

Además, con las memorias flash, cada ráfaga de voltaje en la celda provoca una degradación. A medida que el tamaño de las celdas disminuye, el daño causado por la programación se agrava porque el voltaje necesario para programar el dispositivo no se ajusta a la litografía. La mayoría de los dispositivos flash están clasificados, actualmente, para solo 5000 escrituras por sector, y muchos controladores flash realizan una nivelación del desgaste para distribuir las escrituras en muchos sectores físicos.

Los dispositivos PRAM también se degradan con el uso, por razones diferentes a las de las memorias flash, pero se degradan mucho más lentamente. Un dispositivo PRAM puede soportar alrededor de 100 millones de ciclos de escritura. [20] La vida útil de una PRAM está limitada por mecanismos como la degradación debido a la expansión térmica de GST durante la programación, la migración de metales (y otros materiales) y otros mecanismos aún desconocidos.

Las piezas de Flash se pueden programar antes de soldarlas a una placa , o incluso comprarse preprogramadas. Sin embargo, el contenido de una PRAM se pierde debido a las altas temperaturas necesarias para soldar el dispositivo a una placa (consulte soldadura por reflujo o soldadura por ola ). Esto empeoró debido al requisito de tener una fabricación sin plomo que requiere temperaturas de soldadura más altas. Un fabricante que utiliza piezas de PRAM debe proporcionar un mecanismo para programar la PRAM "en el sistema" después de que se haya soldado en su lugar.

Las puertas especiales que se utilizan en la memoria flash “pierden” carga (electrones) con el tiempo, lo que provoca la corrupción y la pérdida de datos. La resistividad del elemento de memoria en PRAM es más estable; a la temperatura de trabajo normal de 85 °C, se estima que retendrá datos durante 300 años. [21]

Al modular cuidadosamente la cantidad de carga almacenada en la compuerta, los dispositivos flash pueden almacenar varios bits (normalmente dos) en cada celda física. En efecto, esto duplica la densidad de memoria , lo que reduce el coste. Los dispositivos PRAM almacenaban originalmente solo un bit en cada celda, pero los avances recientes de Intel han eliminado este problema. [ cita requerida ]

Debido a que los dispositivos flash atrapan electrones para almacenar información, son susceptibles a la corrupción de datos por radiación , lo que los hace inadecuados para muchas aplicaciones espaciales y militares. La PRAM presenta una mayor resistencia a la radiación.

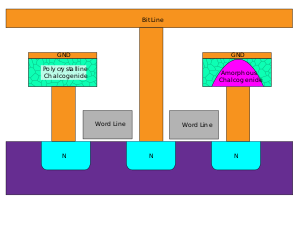

Los selectores de celdas PRAM pueden utilizar varios dispositivos: diodos , BJT y MOSFET . El uso de un diodo o un BJT proporciona la mayor cantidad de corriente para un tamaño de celda determinado. Sin embargo, la preocupación con el uso de un diodo surge de las corrientes parásitas a las celdas vecinas, así como de un requisito de voltaje más alto, lo que resulta en un mayor consumo de energía. La resistencia de calcogenuro es necesariamente mayor que la de un diodo, lo que significa que el voltaje de operación debe superar 1 V por un amplio margen para garantizar una corriente de polarización directa adecuada del diodo. Quizás la consecuencia más grave de usar una matriz seleccionada por diodos, en particular para matrices grandes, es la corriente de fuga de polarización inversa total de las líneas de bits no seleccionadas. En las matrices seleccionadas por transistores , solo las líneas de bits seleccionadas contribuyen a la corriente de fuga de polarización inversa. La diferencia en la corriente de fuga es de varios órdenes de magnitud. Otra preocupación con el escalado por debajo de 40 nm es el efecto de los dopantes discretos a medida que se reduce el ancho de la unión pn . Los selectores basados en película delgada permiten densidades más altas, utilizando un área de celda de < 4 F2 mediante el apilamiento de capas de memoria horizontal o verticalmente. A menudo, las capacidades de aislamiento son inferiores al uso de transistores si la relación de encendido/apagado del selector no es suficiente, lo que limita la capacidad de operar matrices muy grandes en esta arquitectura. Se ha demostrado que los interruptores de umbral basados en calcogenuro son un selector viable para matrices PCM de alta densidad [22].

En agosto de 2004, Nanochip licenció la tecnología PRAM para su uso en dispositivos de almacenamiento de sondas MEMS (sistemas microeléctricos-mecánicos). Estos dispositivos no son de estado sólido . En su lugar, un plato muy pequeño recubierto de calcogenuro se arrastra debajo de miles o incluso millones de sondas eléctricas que pueden leer y escribir el calcogenuro. La tecnología de micro-movimiento de Hewlett-Packard puede colocar el plato con precisión a 3 nm , por lo que serán posibles densidades de más de 1 Tbit (125 GB ) por pulgada cuadrada si se puede perfeccionar la tecnología. La idea básica es reducir la cantidad de cableado necesario en el chip; en lugar de cablear cada celda, las celdas se colocan más juntas y se leen mediante la corriente que pasa a través de las sondas MEMS, actuando como cables. Este enfoque se asemeja a la tecnología Millipede de IBM .

En septiembre de 2006, Samsung anunció un prototipo de dispositivo de 512 Mb (64 MB ) que utilizaba interruptores de diodo . [23] El anuncio fue algo sorprendente, y fue especialmente notable por su densidad de memoria bastante alta . El prototipo presentaba un tamaño de celda de solo 46,7 nm, más pequeño que los dispositivos flash comerciales disponibles en ese momento. Aunque había dispositivos flash de mayor capacidad disponibles (64 Gb , u 8 GB , recién estaba llegando al mercado), otras tecnologías que competían para reemplazar flash en general ofrecían densidades más bajas (tamaños de celda más grandes). Los únicos dispositivos MRAM y FeRAM de producción son de solo 4 Mb, por ejemplo. La alta densidad del dispositivo PRAM prototipo de Samsung sugería que podría ser un competidor flash viable, y no limitado a roles de nicho como lo han estado otros dispositivos. PRAM parecía ser particularmente atractivo como un reemplazo potencial para flash NOR , donde las capacidades de los dispositivos generalmente quedan rezagadas con respecto a las de los dispositivos flash NAND . Las capacidades de última generación en NAND superaron los 512 Mb hace algún tiempo. La memoria flash NOR ofrece densidades similares al prototipo PRAM de Samsung y ya ofrece direccionabilidad de bits (a diferencia de NAND, donde se accede a la memoria en bancos de muchos bytes a la vez).

El anuncio de Samsung fue seguido por uno de Intel y STMicroelectronics , quienes demostraron sus propios dispositivos PRAM en el Intel Developer Forum de 2006 en octubre. [24] Mostraron una pieza de 128 Mb que comenzó a fabricarse en el laboratorio de investigación de STMicroelectronics en Agrate, Italia. Intel declaró que los dispositivos eran estrictamente una prueba de concepto .

La PRAM también es una tecnología prometedora en las industrias militar y aeroespacial, donde los efectos de la radiación hacen que el uso de memorias no volátiles estándar como las flash sea poco práctico. BAE Systems ha presentado dispositivos PRAM , conocidos como C-RAM, que afirman tener una excelente tolerancia a la radiación ( rad-hard ) e inmunidad al bloqueo . Además, BAE afirma tener una resistencia al ciclo de escritura de 10 8 , lo que le permitirá ser un candidato para reemplazar las PROM y EEPROM en los sistemas espaciales.

En febrero de 2008, Intel y STMicroelectronics revelaron el primer prototipo de matriz PRAM multinivel ( MLC ). El prototipo almacenaba dos bits lógicos en cada celda física, en efecto 256 Mb de memoria almacenados en una matriz física de 128 Mb. Esto significa que en lugar de los dos estados normales (totalmente amorfo y totalmente cristalino ), dos estados intermedios distintos adicionales representan diferentes grados de cristalización parcial, lo que permite almacenar el doble de bits en la misma área física. [16] En junio de 2011, [25] IBM anunció que había creado una memoria de cambio de fase multibit estable, confiable y de alto rendimiento y estabilidad. SK Hynix tenía un acuerdo de desarrollo conjunto y un acuerdo de licencia de tecnología con IBM para el desarrollo de la tecnología PRAM multinivel. [26]

También en febrero de 2008, Intel y STMicroelectronics enviaron muestras de prototipos de su primer producto PRAM a los clientes. El producto de 90 nm y 128 Mb (16 MB) se llamó Alverstone. [27]

En junio de 2009, Samsung y Numonyx BV anunciaron un esfuerzo de colaboración para el desarrollo de productos de hardware PRAM adaptados al mercado. [28]

En abril de 2010, [29] Numonyx anunció la línea Omneo de memorias de cambio de fase compatibles con NOR de 128 Mbit. Samsung anunció el envío de RAM de cambio de fase (PRAM) de 512 Mb en un paquete multichip (MCP) para su uso en teléfonos móviles en el otoño de 2010.

En diciembre de 2018, STMicroelectronics presentó datos de diseño y rendimiento para una matriz ePCM de 16 MB para una unidad de control automotriz de silicio sobre aislante completamente agotado de 28 nm . [30]

Más recientemente, existe un interés significativo en la aplicación de PCM para la computación en memoria. [31] La idea esencial es realizar tareas computacionales como operaciones de multiplicación de matriz-vector en la propia matriz de memoria explotando la capacidad de almacenamiento analógico de PCM y las leyes de circuitos de Kirchhoff . La computación en memoria basada en PCM podría ser interesante para aplicaciones como la inferencia de aprendizaje profundo que no requieren una precisión computacional muy alta. [32] En 2021, IBM publicó un núcleo de computación en memoria completo basado en PCM multinivel integrado en un nodo de tecnología CMOS de 14 nm . [33]

El mayor desafío para la memoria de cambio de fase ha sido el requisito de una alta densidad de corriente de programación (>10 7 A /cm 2 , en comparación con 10 5 ... 10 6 A/cm 2 para un transistor o diodo típico ). [ cita requerida ] El contacto entre la región de cambio de fase caliente y el dieléctrico adyacente es otra preocupación fundamental. El dieléctrico puede comenzar a perder corriente a una temperatura más alta, o puede perder adhesión al expandirse a una velocidad diferente del material de cambio de fase.

La memoria de cambio de fase es susceptible a una disyuntiva fundamental entre cambio de fase no deseado y cambio de fase deseado. Esto se debe principalmente al hecho de que el cambio de fase es un proceso impulsado térmicamente en lugar de un proceso electrónico. Las condiciones térmicas que permiten una cristalización rápida no deben ser demasiado similares a las condiciones de espera, por ejemplo, la temperatura ambiente, de lo contrario no se puede mantener la retención de datos. Con la energía de activación adecuada para la cristalización, es posible tener una cristalización rápida en condiciones de programación y, al mismo tiempo, una cristalización muy lenta en condiciones normales.

Probablemente el mayor desafío para la memoria de cambio de fase es su resistencia a largo plazo y la deriva del voltaje umbral . [34] La resistencia del estado amorfo aumenta lentamente de acuerdo con una ley de potencia (~t 0,1 ). Esto limita severamente la capacidad para la operación de múltiples niveles, ya que un estado intermedio inferior se confundiría con un estado intermedio superior en un momento posterior, y también podría poner en peligro la operación estándar de dos estados si el voltaje umbral aumenta más allá del valor de diseño.

En abril de 2010, Numonyx lanzó su línea Omneo de chips PRAM de reemplazo de flash NOR de 128 Mb con interfaz en serie y paralela . Aunque los chips flash NOR que pretendían reemplazar operaban en el rango de -40 a 85 °C, los chips PRAM operaban en el rango de 0 a 70 °C, lo que indica una ventana operativa más pequeña en comparación con los flash NOR. Esto probablemente se deba al uso de uniones p–n altamente sensibles a la temperatura para proporcionar las altas corrientes necesarias para la programación.

{{cite web}}: La cita utiliza un título genérico ( ayuda )