JTAG (llamado así por el Joint Test Action Group que lo codificó) es un estándar industrial para verificar diseños y probar placas de circuito impreso después de la fabricación.

JTAG implementa estándares para instrumentación en chip en automatización de diseño electrónico (EDA) como herramienta complementaria a la simulación digital . [1] Especifica el uso de un puerto de depuración dedicado que implementa una interfaz de comunicaciones en serie para un acceso de bajo costo sin requerir acceso externo directo a la dirección del sistema y a los buses de datos. La interfaz se conecta a un puerto de acceso de prueba (TAP) en el chip que implementa un protocolo con estado para acceder a un conjunto de registros de prueba que presentan niveles lógicos del chip y capacidades del dispositivo de varias partes.

El Joint Test Action Group se formó en 1985 para desarrollar un método de verificación de diseños y pruebas de placas de circuito impreso después de su fabricación. En 1990, el Instituto de Ingenieros Eléctricos y Electrónicos codificó los resultados del esfuerzo en el estándar IEEE 1149.1-1990, titulado Puerto de acceso de prueba estándar y arquitectura de escaneo de límites .

Muchos fabricantes de chips semiconductores han ampliado los estándares JTAG con variantes especializadas para proporcionar características específicas del proveedor. [2]

En la década de 1980, las placas de circuitos multicapa y los circuitos integrados (CI) que utilizaban una matriz de rejilla de bolas y tecnologías de montaje similares se estaban convirtiendo en estándar, y se realizaban conexiones entre CI que no estaban disponibles para las sondas. La mayoría de las fallas de fabricación y de campo en las placas de circuito se debieron a uniones de soldadura deficientes en las placas, imperfecciones entre las conexiones de las placas o las uniones y cables de unión desde las almohadillas de circuitos integrados hasta los marcos de conductores de clavijas. El Joint Test Action Group (JTAG) se formó en 1985 para proporcionar una vista de los pines de una almohadilla de CI a otra para poder descubrir estas fallas.

El estándar de la industria se convirtió en estándar IEEE en 1990 como IEEE Std. 1149.1-1990 [3] después de muchos años de uso inicial. Ese mismo año, Intel lanzó su primer procesador con JTAG (el 80486 ), lo que llevó a una adopción industrial más rápida por parte de todos los fabricantes. En 1994, se añadió un suplemento que contiene una descripción del lenguaje de descripción de exploración de límites (BSDL). En 2001 se realizaron y publicaron más mejoras con respecto al uso de ceros para EXTEST, separando el uso de SAMPLE de PRELOAD y una mejor implementación para las celdas OBSERVE_ONLY. [4] Desde 1990, este estándar ha sido adoptado por compañías de electrónica de todo el mundo. El escaneo de límites ahora es principalmente sinónimo de JTAG, pero JTAG tiene usos esenciales más allá de dichas aplicaciones de fabricación. La revisión de 2013 [5] de IEEE Std. 1149.1 ha introducido un amplio conjunto de características opcionales, extensiones asociadas a BSDL y un nuevo lenguaje de descripción de procedimientos (PDL) basado en Tcl .

Aunque las primeras aplicaciones de JTAG estaban dirigidas a pruebas a nivel de placa, en este caso el estándar JTAG fue diseñado para ayudar con las pruebas, el diagnóstico y el aislamiento de fallas de dispositivos, placas y sistemas. Hoy en día, JTAG se utiliza como medio principal para acceder a subbloques de circuitos integrados , lo que lo convierte en un mecanismo esencial para depurar sistemas integrados que podrían no tener ningún otro canal de comunicaciones con capacidad de depuración. [ cita necesaria ] En la mayoría de los sistemas, la depuración basada en JTAG está disponible desde la primera instrucción después del reinicio de la CPU, lo que le permite ayudar con el desarrollo del software de arranque temprano que se ejecuta antes de que se configure algo. Un emulador en circuito (o, más correctamente, un "adaptador JTAG") utiliza JTAG como mecanismo de transporte para acceder a los módulos de depuración en chip dentro de la CPU de destino . Esos módulos permiten a los desarrolladores de software depurar el software de un sistema integrado directamente en el nivel de instrucción de la máquina cuando sea necesario o (más típicamente) en términos de código fuente de lenguaje de alto nivel.

El soporte de depuración del software del sistema es para muchos desarrolladores de software la razón principal para estar interesados en JTAG. Muchas arquitecturas de silicio, como PowerPC, MIPS, ARM y x86, crearon una infraestructura completa de depuración de software, seguimiento de instrucciones y seguimiento de datos en torno al protocolo JTAG básico. Sin embargo, con frecuencia los proveedores individuales de silicio solo implementan partes de estas extensiones. Algunos ejemplos son ARM CoreSight y Nexus , así como las implementaciones BTS (Branch Trace Storage), LBR (Last Branch Record) e IPT (Intel Processor Trace) de Intel. Hay muchas otras extensiones específicas de proveedores de silicio que pueden no estar documentadas excepto bajo NDA . La adopción del estándar JTAG ayudó a alejar los entornos de depuración centrados en JTAG de los primeros diseños específicos de procesadores. Normalmente, los procesadores se pueden detener, realizar un solo paso o dejar que funcionen libremente. Se pueden establecer puntos de interrupción del código, tanto para el código en RAM (a menudo usando una instrucción de máquina especial, por ejemplo, INT3 ) como en ROM/flash. Los puntos de interrupción de datos suelen estar disponibles, al igual que la descarga masiva de datos a la RAM. La mayoría de los diseños tienen "depuración en modo detenido", pero algunos permiten a los depuradores acceder a registros y buses de datos sin necesidad de detener el núcleo que se está depurando. Algunas cadenas de herramientas pueden usar módulos ARM Embedded Trace Macrocell (ETM) o implementaciones equivalentes en otras arquitecturas para activar la actividad de depuración (o rastreo) en eventos de hardware complejos, como un analizador lógico programado para ignorar los primeros siete accesos a un registro desde una subrutina particular. .

A veces, los desarrolladores de FPGA también utilizan JTAG para desarrollar herramientas de depuración. [6] Las mismas técnicas JTAG utilizadas para depurar software que se ejecuta dentro de una CPU pueden ayudar a depurar otros bloques de diseño digital dentro de una FPGA. Por ejemplo, se pueden proporcionar instrucciones JTAG personalizadas para permitir la lectura de registros creados a partir de conjuntos arbitrarios de señales dentro de la FPGA, proporcionando visibilidad para comportamientos que son invisibles para las operaciones de escaneo de límites. De manera similar, redactar dichos registros podría proporcionar una capacidad de control que de otro modo no estaría disponible.

JTAG permite que el hardware del programador de dispositivos transfiera datos a la memoria interna no volátil del dispositivo (por ejemplo, CPLD ). Algunos programadores de dispositivos tienen un doble propósito: programar y depurar el dispositivo. En el caso de las FPGA, los dispositivos de memoria volátil también se pueden programar a través del puerto JTAG, normalmente durante el trabajo de desarrollo. Además, se puede acceder a las capacidades de monitoreo interno (temperatura, voltaje y corriente) a través del puerto JTAG.

Los programadores JTAG también se utilizan para escribir software y datos en la memoria flash . Esto generalmente se hace usando el mismo acceso al bus de datos que usaría la CPU y, a veces, lo maneja la CPU. En otros casos, los propios chips de memoria tienen interfaces JTAG. Algunas arquitecturas de depuración modernas proporcionan acceso maestro de bus interno y externo sin necesidad de detener y hacerse cargo de una CPU. En el peor de los casos, normalmente es posible controlar señales de bus externas utilizando la función de exploración de límites.

Como cuestión práctica, al desarrollar un sistema integrado, emular el almacén de instrucciones es la forma más rápida de implementar el "ciclo de depuración" (editar, compilar, descargar, probar y depurar). [ cita necesaria ] Esto se debe a que el emulador en circuito que simula un almacén de instrucciones se puede actualizar muy rápidamente desde el host de desarrollo a través de, digamos, USB. El uso de un puerto serie UART y un gestor de arranque para cargar firmware en Flash hace que este ciclo de depuración sea bastante lento y posiblemente costoso en términos de herramientas; instalar firmware en Flash (o SRAM en lugar de Flash) a través de JTAG es una solución intermedia entre estos extremos.

La tecnología de escaneo de límites JTAG brinda acceso a muchas señales lógicas de un circuito integrado complejo, incluidos los pines del dispositivo. Las señales se representan en el registro de exploración de límites (BSR) accesible a través del TAP. Esto permite probar y controlar los estados de las señales para probar y depurar. Por lo tanto, se pueden localizar fallas tanto de software como de hardware (fabricación) y se puede monitorear un dispositivo en funcionamiento.

Cuando se combina con la autoprueba incorporada ( BIST ), la cadena de escaneo JTAG permite una solución integrada de baja sobrecarga para probar un IC en busca de ciertas fallas estáticas (cortocircuitos, aperturas y errores lógicos). El mecanismo de la cadena de escaneo generalmente no ayuda a diagnosticar ni probar la sincronización, la temperatura u otros errores operativos dinámicos que puedan ocurrir. Los casos de prueba a menudo se proporcionan en formatos estandarizados como SVF o su hermano binario XSVF, y se utilizan en pruebas de producción. La capacidad de realizar este tipo de pruebas en tableros terminados es una parte esencial del diseño para pruebas en los productos actuales, lo que aumenta la cantidad de fallas que se pueden encontrar antes de que los productos se envíen a los clientes.

Una interfaz JTAG es una interfaz especial agregada a un chip. Dependiendo de la versión de JTAG, se agregan dos, cuatro o cinco pines. Las interfaces de cuatro y cinco pines están diseñadas para que varios chips en una placa puedan tener sus líneas JTAG conectadas en cadena si se cumplen condiciones específicas. [7] La interfaz de dos pines está diseñada para que se puedan conectar varios chips en una topología en estrella . En cualquier caso, una sonda de prueba sólo necesita conectarse a un único "puerto JTAG" para tener acceso a todos los chips de una placa de circuito .

Los pines del conector son:

El pin TRST es un reinicio activo-bajo opcional de la lógica de prueba, generalmente asíncrono, pero a veces síncrono, según el chip. Si el pin no está disponible, la lógica de prueba se puede restablecer cambiando al estado de reinicio de forma sincrónica, usando TCK y TMS. Tenga en cuenta que restablecer la lógica de prueba no implica necesariamente restablecer nada más. Generalmente existen algunas operaciones JTAG específicas del procesador que pueden restablecer todo o parte del chip que se está depurando.

Como sólo hay una línea de datos disponible, el protocolo es serial . La entrada del reloj está en el pin TCK. Un bit de datos se transfiere desde TDI y sale a TDO por flanco ascendente del reloj de TCK. Se pueden cargar diferentes instrucciones. Las instrucciones para los circuitos integrados típicos pueden leer la identificación del chip, muestrear pines de entrada, impulsar (o flotar) pines de salida, manipular funciones del chip o derivar (conectar TDI a TDO para acortar lógicamente cadenas de múltiples chips).

Al igual que con cualquier señal sincronizada, los datos presentados a TDI deben ser válidos durante algún tiempo de configuración específico del chip antes y tiempo de retención después del flanco de reloj relevante (aquí, ascendente). Los datos TDO son válidos durante un tiempo específico del chip después del flanco descendente de TCK.

La frecuencia operativa máxima de TCK varía según todos los chips de la cadena (se debe utilizar la velocidad más baja), pero normalmente es de 10 a 100 MHz (100 a 10 ns por bit). Además, las frecuencias TCK dependen del diseño de la placa y de las capacidades y el estado del adaptador JTAG. Un chip puede tener un reloj JTAG de 40 MHz, pero sólo si utiliza un reloj de 200 MHz para operaciones que no sean JTAG; y es posible que necesite utilizar un reloj mucho más lento cuando esté en modo de bajo consumo. En consecuencia, algunos adaptadores JTAG tienen sincronización adaptativa utilizando una señal RTCK (Return TCK). Las frecuencias TCK más rápidas son más útiles cuando se utiliza JTAG para transferir muchos datos, como cuando se almacena un programa ejecutable en la memoria flash .

Los cambios de sincronización en TMS pasan a través de una máquina de estado JTAG estandarizada . La máquina de estado JTAG puede restablecerse, acceder a un registro de instrucciones o acceder a datos seleccionados por el registro de instrucciones.

Las plataformas JTAG suelen añadir señales a las pocas definidas por la especificación IEEE 1149.1. Una señal de reinicio del sistema (SRST) es bastante común, lo que permite a los depuradores restablecer todo el sistema, no solo las partes con soporte JTAG. A veces, hay señales de eventos que se utilizan para desencadenar actividad por parte del host o del dispositivo que se monitorea a través de JTAG; o, quizás, líneas de control adicionales.

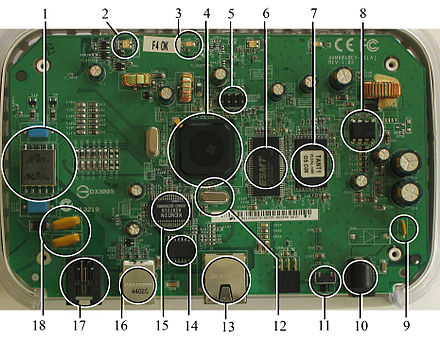

Aunque pocos productos de consumo proporcionan un conector de puerto JTAG explícito, las conexiones a menudo están disponibles en la placa de circuito impreso como un remanente del desarrollo de prototipos y/o producción. Cuando se explotan, estas conexiones suelen proporcionar el medio más viable para la ingeniería inversa .

Número reducido de pines JTAG utiliza sólo dos cables, un cable de reloj y un cable de datos. Esto se define como parte del estándar IEEE 1149.7. [8] Los pines del conector son:

Se llama cJTAG para JTAG compacto.

La interfaz de dos cables redujo la presión sobre la cantidad de pines y los dispositivos se pueden conectar en una topología en estrella . [9] La topología en estrella permite apagar algunas partes del sistema, mientras que aún se puede acceder a otras a través de JTAG; una conexión en cadena requiere que todas las interfaces JTAG estén alimentadas. Existen otras interfaces de dos cables, como Serial Wire Debug.

En JTAG, los dispositivos exponen uno o más puertos de acceso de prueba (TAP). La imagen de arriba muestra tres TAP, que pueden ser chips individuales o módulos dentro de un chip. Una conexión en cadena de TAP se denomina cadena de escaneo o (en términos generales) objetivo. Las cadenas de escaneo pueden ser arbitrariamente largas, pero en la práctica veinte TAP es inusualmente largo. [ cita necesaria ]

Para usar JTAG, se conecta un host a las señales JTAG del objetivo (TMS, TCK, TDI, TDO, etc.) a través de algún tipo de adaptador JTAG , que puede necesitar manejar problemas como cambio de nivel y aislamiento galvánico . El adaptador se conecta al host mediante alguna interfaz como USB, PCI, Ethernet, etc.

El host se comunica con los TAP manipulando TMS y TDI junto con TCK y leyendo los resultados a través de TDO (que es la única entrada estándar del lado del host). Las transiciones de salida TMS/TDI/TCK crean la primitiva de comunicación JTAG básica sobre la que se basan los protocolos de capa superior:

En un nivel básico, el uso de JTAG implica leer y escribir instrucciones y sus registros de datos asociados; y a veces implica ejecutar varios ciclos de prueba. Detrás de esos registros hay hardware que no está especificado por JTAG y que tiene sus propios estados que se ven afectados por las actividades de JTAG.

La mayoría de los hosts JTAG utilizan el camino más corto entre dos estados, quizás restringido por peculiaridades del adaptador. (Por ejemplo, un adaptador [ ¿cuál? ] solo maneja rutas cuyas longitudes son múltiplos de siete bits). Algunas capas construidas sobre JTAG monitorean las transiciones de estado y usan rutas poco comunes para activar operaciones de nivel superior. Algunos núcleos ARM utilizan dichas secuencias para entrar y salir de un modo SWD de dos cables (no JTAG) . En IEEE 1149.7 [8] se utiliza una secuencia de escaneo de bits cero (ZBS) para acceder a funciones avanzadas como la conmutación de TAP dentro y fuera de cadenas de escaneo, administración de energía y un modo de dos cables diferente.

Los tamaños de los registros de instrucciones tienden a ser pequeños, quizás de cuatro o siete bits de ancho. Excepto BYPASS y EXTEST, todos los códigos de operación de instrucción los define el implementador TAP, al igual que sus registros de datos asociados; No se deben utilizar códigos de instrucción no definidos. Dos instrucciones clave son:

Al salir del estado RESET, el registro de instrucciones está precargado con BYPASS o IDCODE. Esto permite a los hosts JTAG identificar el tamaño y, al menos parcialmente, el contenido de la cadena de escaneo a la que están conectados. (Pueden ingresar al estado RESET y luego escanear el registro de datos hasta que lean los datos que escribieron. Un registro BYPASS tiene solo un bit cero; mientras que un registro IDCODE tiene 32 bits y comienza con uno. Entonces, los bits no escritos por el host se puede asignar fácilmente a TAP). Esta identificación se utiliza a menudo para comprobar la integridad de la configuración manual, ya que IDCODE suele ser inespecífico. Por ejemplo, podría identificar un microcontrolador basado en ARM Cortex-M3, sin especificar el proveedor o modelo del microcontrolador; o una FPGA en particular, pero no cómo ha sido programada.

Un modismo común implica cambiar BYPASS a los registros de instrucciones de todos los TAP excepto uno, que recibe alguna otra instrucción. De esa manera, todos los TAP, excepto uno, exponen un registro de datos de un solo bit, y los valores se pueden cambiar selectivamente dentro o fuera del registro de datos de ese TAP sin afectar a ningún otro TAP.

El estándar IEEE 1149.1 (JTAG) describe una serie de instrucciones para admitir aplicaciones de escaneo de límites. Algunas de estas instrucciones son "obligatorias", pero los TAP utilizados para la depuración en lugar de las pruebas de escaneo de límites a veces brindan un soporte mínimo o nulo para estas instrucciones. Esas instrucciones "obligatorias" operan en el Registro de exploración de límites (BSR) definido en el archivo BSDL e incluyen:

Las instrucciones "opcionales" definidas por IEEE incluyen:

Los dispositivos pueden definir más instrucciones y esas definiciones deben formar parte de un archivo BSDL proporcionado por el fabricante. A menudo sólo están marcados como PRIVADOS.

Los dispositivos se comunican con el mundo a través de un conjunto de pines de entrada y salida. Por sí solos, estos pines proporcionan una visibilidad limitada del funcionamiento del dispositivo. Sin embargo, los dispositivos que admiten escaneo de límites contienen una celda de registro de desplazamiento para cada pin de señal del dispositivo. Estos registros están conectados en una ruta dedicada alrededor del límite del dispositivo (de ahí el nombre). La ruta crea una capacidad de acceso virtual que evita las entradas y salidas normales, proporcionando control directo del dispositivo y visibilidad detallada de las señales. [10]

El fabricante suele describir el contenido del registro de exploración de límites, incluidas las capacidades de E/S de señal, mediante un archivo BSDL específico de la pieza . Estos se utilizan con 'netlists' de diseño de sistemas CAD/EDA para desarrollar pruebas utilizadas en la fabricación de placas. Los sistemas de prueba comerciales a menudo cuestan varios miles de dólares por un sistema completo e incluyen opciones de diagnóstico para identificar fallas como circuitos abiertos y cortocircuitos. También pueden ofrecer visores de esquemas o diseños para representar la falla de manera gráfica.

Para permitir el escaneo de límites, los proveedores de circuitos integrados agregan lógica a cada uno de sus dispositivos, incluidas celdas de escaneo para cada uno de los pines de señal. Luego, estas celdas se conectan entre sí para formar el registro de desplazamiento de exploración de límites (BSR), que está conectado a un controlador TAP. Estos diseños son parte de la mayoría de las bibliotecas Verilog o VHDL. Los gastos generales de esta lógica adicional son mínimos y, en general, valen la pena el precio para permitir pruebas eficientes a nivel de placa.

Un ejemplo ayuda a mostrar el funcionamiento de JTAG en sistemas reales. El ejemplo aquí es el TAP de depuración de un procesador ARM11 , el núcleo ARM1136 [11] . El procesador en sí tiene una amplia capacidad JTAG, similar a la que se encuentra en otros núcleos de CPU, y está integrado en chips con capacidades aún más amplias a las que se accede a través de JTAG.

Este es un ejemplo no trivial, que es representativo de una sección representativa significativa de sistemas habilitados para JTAG. Además, muestra cómo se construyen los mecanismos de control utilizando las primitivas de lectura/escritura de registros de JTAG, y cómo se combinan para facilitar las pruebas y la depuración de elementos lógicos complejos; Las CPU son comunes, pero los FPGA y ASIC incluyen otros elementos complejos que deben depurarse.

Los licenciatarios de este núcleo lo integran en chips, normalmente combinándolo con otros TAP así como con numerosos periféricos y memorias. Uno de esos otros TAP maneja las pruebas de escaneo de límites para todo el chip; no es compatible con el TAP de depuración. Ejemplos de tales chips incluyen:

Ambos procesadores están diseñados para su uso en teléfonos inalámbricos como teléfonos celulares, lo cual es parte de la razón por la que incluyen controladores TAP que modifican la cadena de escaneo JTAG: la depuración del funcionamiento de bajo consumo requiere acceder a los chips cuando están en gran parte apagados y, por lo tanto, cuando no. todos los TAP están operativos. Esa modificación de la cadena de escaneo es un tema de un próximo estándar IEEE 1149.7 [8] .

Este TAP de depuración expone varias instrucciones estándar y algunas diseñadas específicamente para la depuración asistida por hardware , donde una herramienta de software (el "depurador") utiliza JTAG para comunicarse con un sistema que se está depurando:

BYPASSe IDCODEinstrucciones estándar como se describe arribaEXTEST, INTEST, instrucciones estándar, pero operando en el núcleo en lugar de una cadena de escaneo de límites externo. EXTESTes nominalmente para escribir datos en el núcleo, INTESTes nominalmente para leerlos; pero dos cadenas de escaneo son excepciones a esa regla.SCAN_NInstrucción ARM para seleccionar la cadena de escaneo numerada utilizada con EXTESTo INTEST. Hay seis cadenas de escaneo:0- Registro de ID del dispositivo, 40 bits de datos de identificación de solo lectura1- Registro de control y estado de depuración (DSCR), 32 bits utilizados para operar las funciones de depuración4- Registro de transferencia de instrucciones (ITR), 33 bits (32 instrucciones más un bit de estado) utilizados para ejecutar instrucciones del procesador mientras se encuentra en un "Modo de depuración" especial (ver más abajo)5- Canal de comunicaciones de depuración (DCC), 34 bits (una palabra de datos larga más dos bits de estado) utilizados para la transferencia de datos bidireccional al núcleo. Esto se usa tanto en modo de depuración como posiblemente en tiempo de ejecución cuando se habla con software compatible con el depurador.6- Módulo de seguimiento integrado (ETM), 40 bits (dirección de 7 bits, una palabra de datos de 32 bits de longitud y un bit R/W) utilizado para controlar el funcionamiento de una instrucción pasiva y un mecanismo de seguimiento de datos. Esto alimenta un búfer de seguimiento integrado (ETB) en el chip o un módulo externo de recopilación de datos de seguimiento de alta velocidad. El seguimiento admite la depuración pasiva (examinar el historial de ejecución) y la creación de perfiles para ajustar el rendimiento.7- módulo de depuración, 40 bits (dirección de 7 bits, una palabra de datos de 32 bits de longitud y un bit de lectura/escritura) que se utiliza para acceder a puntos de interrupción de hardware, puntos de vigilancia y más. Estos se pueden escribir mientras el procesador está en ejecución; no es necesario que esté en modo de depuración.HALTe RESTARTinstrucciones específicas de ARM11 para detener y reiniciar la CPU. Detenerlo coloca el núcleo en el "Modo de depuración", donde el ITR se puede usar para ejecutar instrucciones, incluido el uso del DCC para transferir datos entre el host de depuración (JTAG) y la CPU.ITRSEL, Instrucción específica de ARM11 para acelerar algunas operaciones con ITR.Ese modelo se parece al modelo utilizado en otros núcleos ARM. Los sistemas que no son ARM generalmente tienen capacidades similares, tal vez implementadas utilizando los protocolos Nexus además de JTAG u otros esquemas específicos del proveedor.

Los núcleos ARM7 y ARM9 más antiguos incluyen un módulo EmbeddedICE [14] que combina la mayoría de esas funciones, pero tiene un mecanismo incómodo para la ejecución de instrucciones: el depurador debe controlar la canalización de instrucciones de la CPU, reloj por reloj, y acceder directamente a los buses de datos para leer y escribir datos en la CPU. El ARM11 utiliza el mismo modelo para soporte de seguimiento (ETM, ETB) que los núcleos más antiguos.

Los núcleos ARM Cortex más nuevos se parecen mucho a este modelo de depuración, pero se basan en un puerto de acceso de depuración (DAP) en lugar de acceso directo a la CPU. En esta arquitectura (llamada CoreSight Technology ), el núcleo y el módulo JTAG son completamente independientes. También están desacoplados de JTAG para que puedan alojarse en la interfaz SWD de dos cables de ARM (ver más abajo) en lugar de solo en la interfaz JTAG de seis cables. (ARM toma las cuatro señales JTAG estándar y agrega el TRST opcional, más la señal RTCK utilizada para el reloj adaptativo). CoreSight JTAG-DP es asíncrono con los relojes centrales y no implementa RTCK. [15] Además, los núcleos más nuevos tienen soporte de seguimiento actualizado.

Una forma básica de depurar software es presentar un modelo de subproceso único, donde el depurador detiene periódicamente la ejecución del programa y examina su estado expuesto por el contenido de los registros y la memoria (incluidos los registros del controlador periférico). Cuando se acercan eventos interesantes del programa, una persona puede querer seguir instrucciones de un solo paso (o líneas de código fuente) para observar cómo ocurre un mal comportamiento en particular.

Entonces, por ejemplo, un host JTAG podría DETENER el núcleo, ingresar al modo de depuración y luego leer los registros de la CPU usando ITR y DCC. Después de guardar el estado del procesador, podría escribir esos registros con los valores que necesite y luego ejecutar algoritmos arbitrarios en la CPU, accediendo a la memoria y a los periféricos para ayudar a caracterizar el estado del sistema. Después de que el depurador realiza esas operaciones, se puede restaurar el estado y continuar la ejecución mediante la instrucción RESTART.

Al modo de depuración también se ingresa de forma asincrónica cuando el módulo de depuración activa un punto de vigilancia o punto de interrupción, o al emitir una instrucción BKPT (punto de interrupción) desde el software que se está depurando. Cuando no se utiliza para el seguimiento de instrucciones, el ETM también puede activar la entrada al modo de depuración; admite activadores complejos sensibles al estado y al historial, así como comparaciones de direcciones simples expuestas por el módulo de depuración. Las transiciones asincrónicas al modo de depuración se detectan sondeando el registro DSCR. Así es como se implementa el paso único: DETENER el núcleo, establecer un punto de interrupción temporal en la siguiente instrucción o siguiente declaración de alto nivel, REINICIAR, sondear DSCR hasta que detecte una entrada asincrónica al estado de depuración, eliminar ese punto de interrupción temporal, repetir.

El software moderno suele ser demasiado complejo para funcionar bien con un modelo de subproceso único. Por ejemplo, es posible que un procesador utilizado para controlar un motor (quizás uno que impulse una hoja de sierra) no pueda entrar de manera segura en modo de parada; Es posible que deba continuar manejando las interrupciones para garantizar la seguridad física de las personas y/o la maquinaria. Emitir una instrucción HALT usando JTAG puede ser peligroso.

Los procesadores ARM admiten un modo de depuración alternativo, llamado Modo Monitor , para trabajar en este tipo de situaciones. (Esto es distinto del modo de monitor seguro implementado como parte de las extensiones de seguridad en los núcleos ARM más nuevos; administra las operaciones de depuración, no las transiciones de seguridad). En esos casos, los puntos de interrupción y los puntos de vigilancia desencadenan un tipo especial de excepción de hardware, transfiriendo el control a un " monitor de depuración" que se ejecuta como parte del software del sistema. Este monitor se comunica con el depurador mediante el DCC y podría organizar, por ejemplo, un solo paso en un solo proceso mientras otros procesos (y controladores de interrupciones) continúan ejecutándose.

Los proveedores de microprocesadores a menudo han definido sus propias extensiones de depuración específicas del núcleo. Dichos proveedores incluyen Infineon , MIPS con EJTAG y más. Si el proveedor no adopta un estándar (como los utilizados por los procesadores ARM o Nexus), debe definir su propia solución. Si admiten el escaneo de límites, generalmente crean la depuración a través de JTAG.

Freescale tiene COP y OnCE (emulación en chip). OnCE incluye un comando JTAG que hace que un TAP entre en un modo especial donde el IR contiene comandos de depuración OnCE [16] para operaciones como paso único, puntos de interrupción y acceso a registros o memoria. También define EOnCE (Emulación mejorada en chip) [17] presentada como una solución a problemas de tiempo real.

ARM tiene una extensa arquitectura de depuración de núcleos de procesador (CoreSight) que comenzó con EmbeddedICE (una función de depuración disponible en la mayoría de los núcleos ARM) y ahora incluye muchos componentes adicionales, como un ETM (Embedded Trace Macrocell), con un puerto de rastreo de alta velocidad, que admite rastreo multinúcleo y multiproceso. Tenga en cuenta que el rastreo no es invasivo; Los sistemas no necesitan dejar de funcionar para ser rastreados. (Sin embargo, los datos de seguimiento son demasiado voluminosos para utilizar JTAG como algo más que un canal de control de seguimiento).

Nexus define una infraestructura de depuración del procesador que es en gran medida independiente del proveedor. Una de sus interfaces de hardware es JTAG. También define una interfaz de puerto auxiliar de alta velocidad, utilizada para rastreo y más. Nexus se utiliza con algunas plataformas más nuevas, como los procesadores de las series Atmel AVR32 y Freescale MPC5500.

Se accede a la interfaz JTAG del objetivo mediante alguna aplicación habilitada para JTAG y algún hardware adaptador JTAG. Existe una amplia gama de este tipo de hardware, optimizado para fines tales como pruebas de producción, depuración de sistemas de alta velocidad, desarrollo de microcontroladores de bajo costo, etc. Del mismo modo, el software utilizado para controlar dicho hardware puede ser bastante variado. Los desarrolladores de software utilizan principalmente JTAG para depurar y actualizar el firmware.

No existen estándares oficiales para los conectores físicos del adaptador JTAG. Las placas de desarrollo suelen incluir un encabezado para admitir las herramientas de desarrollo preferidas; en algunos casos incluyen varios encabezados de este tipo, porque necesitan admitir varias herramientas de este tipo. Por ejemplo, un microcontrolador, un FPGA y un procesador de aplicaciones ARM rara vez comparten herramientas, por lo que una placa de desarrollo que utilice todos esos componentes podría tener tres o más encabezados. Las placas de producción pueden omitir los encabezados o, cuando el espacio es limitado, pueden proporcionar acceso a la señal JTAG mediante puntos de prueba.

Algunas configuraciones de pines comunes [20] para cabezales de pines de 2,54 mm (0,100 pulg.) son:

Esos conectores tienden a incluir más que solo las cuatro señales estandarizadas (TMS, TCK, TDI, TDO). Por lo general, se proporcionan señales de reinicio, una o ambas TRST (reinicio de TAP) y SRST (reinicio del sistema). El conector generalmente proporciona el voltaje de suministro lógico de la placa bajo prueba para que los adaptadores JTAG utilicen los niveles lógicos apropiados. El voltaje de la placa también puede servir como entrada del depurador de "placa presente". Se pueden proporcionar otras señales de entrada o salida de eventos, o líneas de E/S de propósito general (GPIO), para admitir arquitecturas de depuración más complejas.

Los productos de gama alta suelen utilizar conectores densos (frecuentemente conectores MICTOR de 38 pines ) para admitir el rastreo de alta velocidad junto con operaciones JTAG. Una tendencia reciente es que las placas de desarrollo integren una interfaz USB a JTAG, donde se utiliza un segundo canal para un puerto serie. (Las placas más pequeñas también se pueden alimentar a través de USB. Dado que las PC modernas tienden a omitir los puertos serie, estos enlaces de depuración integrados pueden reducir significativamente el desorden para los desarrolladores). Las placas de producción a menudo dependen de conexiones de base de clavos a puntos de prueba para pruebas y programación.

El hardware del adaptador varía ampliamente. Cuando no está integrado en una placa de desarrollo, implica un cable corto para conectarlo a un conector JTAG en la placa de destino; una conexión al host de depuración, como un enlace USB, PCI o Ethernet; y suficiente electrónica para adaptar los dos dominios de comunicaciones (y, a veces, proporcionar aislamiento galvánico ). Es posible que se necesite una fuente de alimentación independiente. Existen ambos adaptadores "tontos", donde el host decide y realiza todas las operaciones JTAG; y los "inteligentes", donde parte de ese trabajo se realiza dentro del adaptador, a menudo impulsado por un microcontrolador. Los adaptadores "inteligentes" eliminan las latencias de enlace para secuencias de operación que pueden implicar sondeos para cambios de estado entre pasos y, en consecuencia, pueden ofrecer un mayor rendimiento.

A partir de 2018 [actualizar], los adaptadores con un enlace USB desde el host son el enfoque más común. Los productos de gama alta suelen admitir Ethernet , con la ventaja de que el host de depuración puede ser bastante remoto. Los adaptadores que admiten puertos de seguimiento de alta velocidad generalmente incluyen varios megabytes de búfer de seguimiento y proporcionan enlaces de alta velocidad (USB o Ethernet) para llevar esos datos al host.

Los adaptadores de puerto paralelo son simples y económicos, pero relativamente lentos porque utilizan la CPU del host para cambiar cada bit (" bit banging "). Su utilidad ha disminuido porque la mayoría de las computadoras en los últimos años no tienen un puerto paralelo. La compatibilidad con los controladores también es un problema, porque el uso de pines por parte de los adaptadores varía ampliamente. Dado que el puerto paralelo se basa en un nivel lógico de 5 V, la mayoría de los adaptadores carecían de soporte de traducción de voltaje para voltajes objetivo de 3,3 V o 1,8 V.

También existen adaptadores de puerto serie RS-232 , y su utilidad también está disminuyendo. Por lo general, implican una explosión de bits más lenta que un puerto paralelo o un microcontrolador que traduce algún protocolo de comando a operaciones JTAG. Estos adaptadores serie tampoco son rápidos, pero sus protocolos de comando generalmente podrían reutilizarse además de enlaces de mayor velocidad.

Con todos los adaptadores JTAG, el soporte de software es una preocupación básica. Muchos proveedores no publican los protocolos utilizados por su hardware adaptador JTAG, lo que limita a sus clientes a las cadenas de herramientas admitidas por esos proveedores. Este es un problema particular para los adaptadores "inteligentes", algunos de los cuales incorporan cantidades significativas de conocimiento sobre cómo interactuar con CPU específicas.

La mayoría de los entornos de desarrollo para software integrado incluyen soporte JTAG. En términos generales, existen tres fuentes de dicho software:

Todo este tipo de software tiende a incluir soporte básico para el depurador: detener, detener, realizar pasos únicos, puntos de interrupción, exploración de estructuras de datos, etc. Las herramientas comerciales tienden a proporcionar herramientas como simuladores y análisis de trazas muy precisos, que actualmente no están disponibles como código abierto.

Serial Wire Debug (SWD) es una interfaz eléctrica alternativa de 2 pines que utiliza el mismo protocolo. Utiliza la conexión GND existente. SWD utiliza un protocolo de cable bidireccional estándar de CPU ARM, definido en la interfaz de depuración ARM v5. [21] Esto permite que el depurador se convierta en otro bus maestro AMBA para acceder a la memoria del sistema y a los registros periféricos o de depuración. La velocidad de datos es de hasta 4 MB/s a 50 MHz . SWD también tiene detección de errores incorporada. En dispositivos JTAG con capacidad SWD, TMS y TCK se utilizan como señales SWDIO y SWCLK, lo que permite programadores de modo dual.