La memoria estática de acceso aleatorio ( RAM estática o SRAM ) es un tipo de memoria de acceso aleatorio (RAM) que utiliza circuitos de enclavamiento (flip-flop) para almacenar cada bit. La SRAM es una memoria volátil ; los datos se pierden cuando se corta la energía.

El término estático diferencia la SRAM de la DRAM ( memoria dinámica de acceso aleatorio):

La SRAM bipolar de semiconductores fue inventada en 1963 por Robert Norman en Fairchild Semiconductor . [1] La SRAM de metal-óxido-semiconductor (MOS-SRAM) fue inventada en 1964 por John Schmidt en Fairchild Semiconductor. Era una SRAM de canal p MOS de 64 bits. [2] [3]

SRAM ha sido el principal impulsor de cualquier nuevo proceso de fabricación de tecnología basada en CMOS desde la década de 1960, cuando se inventó CMOS. [4]

En 1964, Arnold Farber y Eugene Schlig, trabajando para IBM, crearon una celda de memoria cableada, utilizando una compuerta de transistor y un pestillo de diodo túnel . Reemplazaron el pestillo con dos transistores y dos resistencias , una configuración que se conoció como la celda Farber-Schlig. Ese año presentaron una divulgación de invención, pero inicialmente fue rechazada. [5] [6] En 1965, Benjamin Agusta y su equipo en IBM crearon un chip de memoria de silicio de 16 bits basado en la celda Farber-Schlig, con 80 transistores, 64 resistencias y 4 diodos.

En abril de 1969, Intel Inc. presentó su primer producto, Intel 3101, un chip de memoria SRAM destinado a reemplazar los voluminosos módulos de memoria de núcleo magnético ; su capacidad era de 64 bits (en las primeras versiones, solo 63 bits eran utilizables debido a un error) [7] y estaba basado en transistores de unión bipolar [8] fue diseñado utilizando rubylith . [9]

Aunque puede caracterizarse como memoria volátil , la SRAM exhibe remanencia de datos . [10]

La memoria SRAM ofrece un modelo de acceso a datos simple y no requiere un circuito de actualización. El rendimiento y la confiabilidad son buenos y el consumo de energía es bajo cuando está inactiva. [11]

Dado que la SRAM requiere más transistores por bit para su implementación, es menos densa y más cara que la DRAM y también tiene un mayor consumo de energía durante el acceso de lectura o escritura. El consumo de energía de la SRAM varía ampliamente según la frecuencia con la que se accede a ella. [11]

Muchas categorías de subsistemas industriales y científicos, electrónica automotriz y sistemas integrados similares contienen SRAM que, en este contexto, puede denominarse ESRAM . [12] Una cierta cantidad (kilobytes o menos) también está incorporada en prácticamente todos los electrodomésticos, juguetes, etc. modernos que implementan una interfaz de usuario electrónica.

La SRAM en su forma de doble puerto se utiliza a veces para circuitos de procesamiento de señales digitales en tiempo real . [13]

La SRAM también se utiliza en ordenadores personales, estaciones de trabajo, enrutadores y equipos periféricos: archivos de registro de CPU , cachés internos de CPU , cachés internos de GPU y cachés SRAM de modo ráfaga externos , búferes de disco duro , búferes de enrutador , etc. Las pantallas LCD y las impresoras también emplean normalmente SRAM para contener la imagen mostrada (o que se va a imprimir). Los LCD pueden tener SRAM en sus controladores LCD. La SRAM se utilizó para la memoria principal de muchos de los primeros ordenadores personales, como el ZX80 , el TRS-80 Model 100 y el VIC-20 .

Algunas de las primeras tarjetas de memoria de finales de la década de 1980 y principios de la de 1990 utilizaban SRAM como medio de almacenamiento, lo que requería una batería de litio para mantener el contenido de la SRAM. [14] [15]

La SRAM se puede integrar en el chip para:

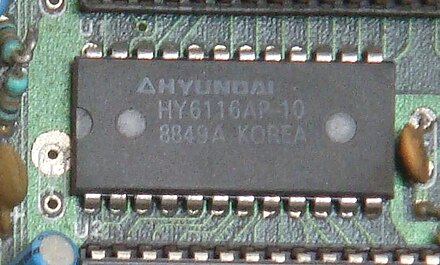

Los aficionados, en especial los entusiastas de los procesadores caseros, [16] a menudo prefieren la SRAM debido a la facilidad de interconexión. Es mucho más fácil trabajar con ella que con la DRAM, ya que no hay ciclos de actualización y los buses de dirección y datos suelen ser directamente accesibles. [ cita requerida ] Además de los buses y las conexiones de alimentación, la SRAM normalmente requiere solo tres controles: Chip Enable (CE), Write Enable (WE) y Output Enable (OE). En la SRAM síncrona, también se incluye Clock (CLK). [17]

La SRAM no volátil (nvSRAM) tiene la funcionalidad SRAM estándar, pero guarda los datos cuando se pierde el suministro de energía, lo que garantiza la preservación de la información crítica. Las nvSRAM se utilizan en una amplia gama de situaciones (redes, aeroespacial y médica, entre muchas otras [18] ), donde la preservación de los datos es fundamental y donde las baterías son poco prácticas.

La RAM pseudoestática (PSRAM) es una DRAM combinada con un circuito de actualización automática. [19] Externamente parece una SRAM más lenta, aunque con una ventaja de densidad y costo sobre la SRAM verdadera, y sin la complejidad de acceso de la DRAM.

En la década de 1990, la SRAM asíncrona solía emplearse para un tiempo de acceso rápido. La SRAM asíncrona se usaba como memoria principal para pequeños procesadores integrados sin caché utilizados en todo, desde electrónica industrial y sistemas de medición hasta discos duros y equipos de red, entre muchas otras aplicaciones. Hoy en día, la SRAM síncrona (por ejemplo, la SRAM DDR) se emplea de manera bastante similar a la DRAM síncrona: se usa más la memoria DDR SDRAM que la DRAM asíncrona . La interfaz de memoria síncrona es mucho más rápida ya que el tiempo de acceso se puede reducir significativamente al emplear la arquitectura de canalización . Además, como la DRAM es mucho más barata que la SRAM, la SRAM a menudo se reemplaza por DRAM, especialmente en el caso de que se requiera un gran volumen de datos. Sin embargo, la memoria SRAM es mucho más rápida para el acceso aleatorio (no en bloques / ráfagas). Por lo tanto, la memoria SRAM se usa principalmente para la caché de la CPU , la memoria pequeña en chip, los FIFO u otros búferes pequeños.

Una celda SRAM típica está formada por seis MOSFET y a menudo se la denomina celda SRAM 6T . Cada bit de la celda se almacena en cuatro transistores (M1, M2, M3, M4) que forman dos inversores acoplados de forma cruzada. Esta celda de almacenamiento tiene dos estados estables que se utilizan para denotar 0 y 1. Dos transistores de acceso adicionales sirven para controlar el acceso a una celda de almacenamiento durante las operaciones de lectura y escritura. La SRAM 6T es el tipo de SRAM más común. [20] Además de la SRAM 6T, otros tipos de SRAM utilizan 4, 5, 7, [21] 8, 9, [20] 10 [22] (SRAM 4T, 5T, 7T 8T, 9T, 10T) o más transistores por bit. [23] [24] [25] La SRAM de cuatro transistores es bastante común en dispositivos SRAM independientes (a diferencia de la SRAM utilizada para cachés de CPU), implementada en procesos especiales con una capa adicional de polisilicio , lo que permite resistencias pull-up de muy alta resistencia. [26] El principal inconveniente de usar SRAM de 4T es el aumento de la potencia estática debido al flujo de corriente constante a través de uno de los transistores pull-down (M1 o M2).

Esto a veces se usa para implementar más de un puerto (de lectura y/o escritura), lo que puede ser útil en ciertos tipos de memoria de video y archivos de registro implementados con circuitos SRAM de múltiples puertos.

En general, cuanto menos transistores se necesiten por celda, más pequeña puede ser cada una de ellas. Dado que el costo de procesamiento de una oblea de silicio es relativamente fijo, el uso de celdas más pequeñas y, por lo tanto, la inclusión de más bits en una oblea reduce el costo por bit de la memoria.

Son posibles celdas de memoria que utilizan menos de cuatro transistores; sin embargo, dichas celdas 3T [27] [28] o 1T son DRAM, no SRAM (incluso las llamadas 1T-SRAM ).

El acceso a la celda se habilita mediante la línea de palabra (WL en la figura) que controla los dos transistores de acceso M5 y M6 que , a su vez, controlan si la celda debe conectarse a las líneas de bits: BL y BL2. Se utilizan para transferir datos tanto para operaciones de lectura como de escritura. Aunque no es estrictamente necesario tener dos líneas de bits, normalmente se proporcionan tanto la señal como su inversa para mejorar los márgenes de ruido y la velocidad.

Durante los accesos de lectura, los inversores de la celda SRAM activan las líneas de bits en sentido alto y bajo. Esto mejora el ancho de banda de la SRAM en comparación con las DRAM: en una DRAM, la línea de bits está conectada a los condensadores de almacenamiento y la distribución de carga hace que la línea de bits oscile hacia arriba o hacia abajo. La estructura simétrica de las SRAM también permite la señalización diferencial , lo que hace que las pequeñas oscilaciones de voltaje sean más fácilmente detectables. Otra diferencia con la DRAM que contribuye a que la SRAM sea más rápida es que los chips comerciales aceptan todos los bits de dirección a la vez. En comparación, las DRAM comerciales tienen la dirección multiplexada en dos mitades, es decir, bits más altos seguidos de bits más bajos, sobre los mismos pines del paquete para mantener su tamaño y costo bajos.

El tamaño de una SRAM con m líneas de dirección y n líneas de datos es de 2 m palabras, o 2 m × n bits. El tamaño de palabra más común es de 8 bits, lo que significa que se puede leer o escribir un solo byte en cada una de las 2 m palabras diferentes dentro del chip SRAM. Varios chips SRAM comunes tienen 11 líneas de dirección (por lo tanto, una capacidad de 2 11 = 2048 = 2 k palabras) y una palabra de 8 bits, por lo que se los conoce como "SRAM 2k × 8".

Las dimensiones de una celda SRAM en un IC están determinadas por el tamaño mínimo de la característica del proceso utilizado para fabricar el IC.

Una celda SRAM tiene tres estados:

La memoria SRAM que funciona en modo lectura y escritura debe tener "legibilidad" y "estabilidad de escritura", respectivamente. Los tres estados diferentes funcionan de la siguiente manera:

Si la línea de palabra no está activada, los transistores de acceso M 5 y M 6 desconectan la celda de las líneas de bits. Los dos inversores acoplados en cruz formados por M 1 – M 4 continuarán reforzándose entre sí mientras estén conectados a la fuente de alimentación.

En teoría, la lectura solo requiere afirmar la línea de palabra WL y leer el estado de la celda SRAM mediante un solo transistor de acceso y línea de bit, p. ej. M 6 , BL. Sin embargo, las líneas de bit son relativamente largas y tienen una gran capacitancia parásita . Para acelerar la lectura, en la práctica se utiliza un proceso más complejo: el ciclo de lectura se inicia precargando ambas líneas de bit BL y BL , a un voltaje alto (lógica 1 ). Luego, afirmar la línea de palabra WL habilita ambos transistores de acceso M 5 y M 6 , lo que hace que el voltaje de una línea de bit BL caiga ligeramente. Luego, las líneas BL y BL tendrán una pequeña diferencia de voltaje entre ellas. Un amplificador de detección detectará qué línea tiene el voltaje más alto y, por lo tanto, determinará si había 1 o 0 almacenado. Cuanto mayor sea la sensibilidad del amplificador de detección, más rápida será la operación de lectura. Como el NMOS es más potente, la extracción es más fácil. Por lo tanto, las líneas de bit se precargan tradicionalmente a alto voltaje. Muchos investigadores también están tratando de precargar a un voltaje ligeramente bajo para reducir el consumo de energía. [29] [30]

El ciclo de escritura comienza aplicando el valor que se va a escribir en las líneas de bits. Para escribir un 0, se aplica un 0 a las líneas de bits, como establecer BL en 1 y BL en 0. Esto es similar a aplicar un pulso de reinicio a un SR-latch , que hace que el flip flop cambie de estado. Se escribe un 1 invirtiendo los valores de las líneas de bits. Luego se afirma WL y se bloquea el valor que se va a almacenar. Esto funciona porque los controladores de entrada de la línea de bits están diseñados para ser mucho más fuertes que los transistores relativamente débiles en la propia celda, de modo que pueden anular fácilmente el estado anterior de los inversores acoplados de forma cruzada. En la práctica, los transistores NMOS de acceso M 5 y M 6 tienen que ser más fuertes que los transistores NMOS inferiores (M 1 , M 3 ) o PMOS superiores (M 2 , M 4 ). Esto se obtiene fácilmente ya que los transistores PMOS son mucho más débiles que los NMOS cuando tienen el mismo tamaño. En consecuencia, cuando un par de transistores (por ejemplo, M 3 y M 4 ) se anula solo ligeramente durante el proceso de escritura, el voltaje de compuerta del par de transistores opuestos (M 1 y M 2 ) también cambia. Esto significa que los transistores M 1 y M 2 se pueden anular más fácilmente, y así sucesivamente. Por lo tanto, los inversores acoplados en cruz magnifican el proceso de escritura.

La RAM con un tiempo de acceso de 70 ns generará datos válidos dentro de los 70 ns a partir del momento en que las líneas de dirección sean válidas. Algunas celdas de SRAM tienen un "modo de página", donde las palabras de una página (256, 512 o 1024 palabras) se pueden leer secuencialmente con un tiempo de acceso significativamente más corto (normalmente, aproximadamente 30 ns). La página se selecciona configurando las líneas de dirección superiores y luego las palabras se leen secuencialmente recorriendo las líneas de dirección inferiores.

Con la introducción de la implementación del transistor FinFET en las celdas SRAM, estas comenzaron a sufrir ineficiencias cada vez mayores en el tamaño de las celdas. En los últimos 30 años (de 1987 a 2017), con una disminución constante del tamaño de los transistores (tamaño de los nodos), la reducción de la huella de la topología de las celdas SRAM se ralentizó, lo que hizo más difícil agrupar las celdas de manera más densa. [4]

Además de los problemas de tamaño, un desafío importante de las celdas SRAM modernas es la fuga de corriente estática. La corriente, que fluye desde la fuente de alimentación positiva (V dd ), a través de la celda y hacia tierra, aumenta exponencialmente cuando aumenta la temperatura de la celda. La pérdida de potencia de la celda se produce tanto en estado activo como inactivo, desperdiciando así energía útil sin realizar ningún trabajo útil. Aunque en los últimos 20 años el problema se solucionó parcialmente mediante la técnica de voltaje de retención de datos (DRV) con tasas de reducción que van de 5 a 10, la disminución del tamaño del nodo provocó que las tasas de reducción cayeran a aproximadamente 2. [4]

Con estos dos problemas se volvió más difícil desarrollar memorias SRAM densas y energéticamente eficientes, lo que impulsó a la industria de semiconductores a buscar alternativas como STT-MRAM y F-RAM . [4] [31]

En 2019, un instituto francés informó sobre una investigación de un circuito integrado fabricado a 28 nm con fines de IoT . [32] Se basaba en transistores de silicio sobre aislante totalmente agotados (FD-SOI), tenía un riel de memoria SRAM de dos puertos para accesos sincrónicos/asincrónicos y una conexión a tierra virtual selectiva (SVGND). El estudio afirmaba que se alcanzaba una corriente SVGND ultrabaja en los modos de "suspensión" y lectura mediante un ajuste fino de su voltaje. [32]