La lógica PMOS o pMOS (del semiconductor de óxido metálico de canal p ) es una familia de circuitos digitales basados en transistores de efecto de campo semiconductores de óxido metálico (MOSFET) de modo mejorado de canal p. A finales de los años 1960 y principios de los 1970, la lógica PMOS era la tecnología de semiconductores dominante para circuitos integrados a gran escala antes de ser reemplazada por los dispositivos NMOS y CMOS .

Mohamed Atalla y Dawon Kahng fabricaron el primer MOSFET funcional en Bell Labs en 1959. [1] Fabricaron dispositivos PMOS y NMOS, pero solo funcionaban los dispositivos PMOS. [2] Pasaría más de una década antes de que los contaminantes en el proceso de fabricación (particularmente el sodio) pudieran gestionarse lo suficientemente bien como para fabricar dispositivos NMOS prácticos.

En comparación con el transistor de unión bipolar , el único otro dispositivo disponible en ese momento para su uso en un circuito integrado , el MOSFET ofrece una serie de ventajas:

Las desventajas relativas a los circuitos integrados bipolares fueron:

General Microelectronics introdujo el primer circuito PMOS comercial en 1964, un registro de desplazamiento de 20 bits con 120 MOSFET, un nivel de integración increíble en aquel momento. [5] El intento de General Microelectronics en 1965 de desarrollar un conjunto de 23 circuitos integrados personalizados para una calculadora electrónica para Victor Comptometer [5] resultó ser demasiado ambicioso dada la confiabilidad de los circuitos PMOS en ese momento y finalmente condujo a la desaparición de Microelectrónica general. [6] Otras empresas continuaron fabricando circuitos PMOS, como grandes registros de desplazamiento ( General Instrument ) [7] o el multiplexor analógico 3705 ( Fairchild Semiconductor ) [8] que no eran factibles en las tecnologías bipolares de la época.

Se produjo una mejora importante con la introducción de la tecnología de puerta autoalineada de polisilicio en 1968. [9] Tom Klein y Federico Faggin de Fairchild Semiconductor mejoraron el proceso de puerta autoalineada para hacerlo comercialmente viable, lo que resultó en el lanzamiento del multiplexor analógico 3708. como el primer circuito integrado de puerta de silicio. [9] El proceso de compuerta autoalineada permitió tolerancias de fabricación más estrictas y, por lo tanto, MOSFET más pequeños y capacitancias de compuerta reducidas y consistentes. Por ejemplo, para las memorias PMOS, esta tecnología ofrecía de tres a cinco veces la velocidad en la mitad del área del chip. [9] El material de la compuerta de polisilicio no solo hizo posible la compuerta autoalineada, sino que también resultó en un voltaje de umbral reducido y, en consecuencia, en un voltaje mínimo de suministro de energía más bajo (por ejemplo, -16 V [ 10] : 1-13 ), reduciendo el el consumo de energía. Debido al menor voltaje de la fuente de alimentación, la lógica PMOS de puerta de silicio a menudo se denomina PMOS de bajo voltaje en contraste con el PMOS de puerta metálica más antiguo como PMOS de alto voltaje . [3] : 89

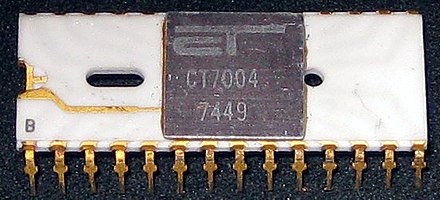

Por diversas razones, Fairchild Semiconductor no desarrolló los circuitos integrados PMOS con tanta intensidad como querían los directivos implicados. [11] : 1302 Dos de ellos, Gordon Moore y Robert Noyce , decidieron en 1968 fundar su propia startup: Intel . Poco después se les unieron otros ingenieros de Fairchild, entre ellos Federico Faggin y Les Vadasz . Intel presentó su primera memoria estática de acceso aleatorio PMOS con una capacidad de 256 bits, la Intel 1101, en 1969. [11] : 1303 La memoria dinámica de acceso aleatorio de 1024 bits , la Intel 1103, siguió en 1970. [12] La 1103 fue un éxito comercial y rápidamente comenzó a reemplazar la memoria de núcleo magnético en las computadoras. [12] Intel presentó su primer microprocesador PMOS , el Intel 4004 , en 1971. Varias empresas siguieron el ejemplo de Intel. La mayoría de los primeros microprocesadores se fabricaron con tecnología PMOS: 4040 y 8008 de Intel; IMP-16 , PACE y SC/MP de National Semiconductor ; TMS1000 de Texas Instruments ; PPS-4 [13] y PPS-8 [14] de Rockwell International . Hay varias primicias comerciales en esta lista de microprocesadores: el primer microprocesador de 4 bits (4004), el primer microprocesador de 8 bits (8008), el primer microprocesador de 16 bits de un solo chip (PACE) y el primer microprocesador de un solo chip. Microcontrolador de 4 bits (TMS1000; RAM y ROM en el mismo chip que la CPU ).

En 1972, la tecnología NMOS finalmente se había desarrollado hasta el punto de poder utilizarse en productos comerciales. Tanto Intel (con el 2102) [15] como IBM [12] introdujeron chips de memoria de 1 kbit. Como la movilidad de los electrones en el canal tipo n de los MOSFET NMOS es aproximadamente tres veces mayor que la movilidad de los huecos en el canal tipo p de los MOSFETS PMOS, la lógica NMOS permite una mayor velocidad de conmutación. Por esta razón, la lógica NMOS rápidamente comenzó a reemplazar a la lógica PMOS. A finales de la década de 1970, los microprocesadores NMOS habían superado a los procesadores PMOS. [16] La lógica PMOS permaneció en uso durante un tiempo debido a su bajo costo y nivel relativamente alto de integración para aplicaciones como calculadoras y relojes simples. La tecnología CMOS prometía un consumo de energía drásticamente menor que el de PMOS o NMOS. Aunque Frank Wanlass [17] ya había propuesto un circuito CMOS en 1963 y los circuitos integrados CMOS comerciales de la serie 4000 habían entrado en producción en 1968, CMOS seguía siendo complejo de fabricar y no permitía ni el nivel de integración de PMOS o NMOS ni la velocidad de NMOS. . Fue necesario esperar hasta la década de 1980 para que CMOS reemplazara a NMOS como la principal tecnología para microprocesadores.

Los circuitos PMOS tienen una serie de desventajas en comparación con las alternativas NMOS y CMOS , incluida la necesidad de varios voltajes de suministro diferentes (tanto positivos como negativos), alta disipación de potencia en el estado conductor y características relativamente grandes. Además, la velocidad de conmutación general es menor.

PMOS utiliza transistores de efecto de campo semiconductores de óxido metálico (MOSFET) de canal p (+) para implementar puertas lógicas y otros circuitos digitales . Los transistores PMOS funcionan creando una capa de inversión en un cuerpo de transistor tipo n . Esta capa de inversión, llamada canal p, puede conducir agujeros entre los terminales de "fuente" y "drenaje" de tipo p .

El canal p se crea aplicando un voltaje negativo (-25 V era común [18] ) al tercer terminal, llamado puerta. Al igual que otros MOSFET, los transistores PMOS tienen cuatro modos de funcionamiento: corte (o subumbral), triodo, saturación (a veces llamado activo) y saturación de velocidad.

Si bien la lógica PMOS es fácil de diseñar y fabricar (se puede hacer que un MOSFET funcione como una resistencia, por lo que todo el circuito se puede fabricar con FET PMOS), también tiene varias deficiencias. El peor problema es que hay corriente continua (DC) a través de una puerta lógica PMOS cuando la llamada "red pull-up" (PUN) está activa, es decir, siempre que la salida es alta, lo que conduce a una disipación de energía estática. incluso cuando el circuito está inactivo.

Además, los circuitos PMOS tardan en pasar de alto a bajo. Al pasar de bajo a alto, los transistores proporcionan baja resistencia y la carga capacitiva en la salida se acumula muy rápidamente (similar a cargar un condensador a través de una resistencia muy baja). Pero la resistencia entre la salida y el riel de suministro negativo es mucho mayor, por lo que la transición de alto a bajo lleva más tiempo (similar a la descarga de un condensador a través de una resistencia alta). El uso de una resistencia de menor valor acelerará el proceso pero también aumentará la disipación de energía estática.

Además, los niveles lógicos de entrada asimétricos hacen que los circuitos PMOS sean susceptibles al ruido. [19]

La mayoría de los circuitos integrados PMOS requieren una fuente de alimentación de 17 a 24 voltios CC. [20] Sin embargo, el microprocesador Intel 4004 PMOS utiliza lógica PMOS con puertas de polisilicio en lugar de puertas metálicas, lo que permite un diferencial de voltaje más pequeño. Para compatibilidad con señales TTL , el 4004 utiliza un voltaje de suministro positivo V SS =+5 V y un voltaje de suministro negativo V DD = -10 V. [21]

Los MOSFET de tipo p están dispuestos en la denominada "red pull-up" (PUN) entre la salida de la puerta lógica y la tensión de alimentación positiva, mientras que se coloca una resistencia entre la salida de la puerta lógica y la tensión de alimentación negativa. El circuito está diseñado de manera que si la salida deseada es alta, entonces el PUN estará activo, creando una ruta de corriente entre el suministro positivo y la salida.

Las puertas PMOS tienen la misma disposición que las puertas NMOS si todos los voltajes están invertidos. [22] Por lo tanto, para la lógica activa-alta, las leyes de De Morgan muestran que una puerta PMOS NOR tiene la misma estructura que una puerta NMOS NAND y viceversa.

Además, los niveles lógicos de entrada asimétricos hacen que los circuitos PMOS sean susceptibles al ruido.

La mayoría de las piezas P-MOS más populares se especifican con fuentes de alimentación de 17 V a 24 V, mientras que el voltaje máximo de fuente de alimentación para CMOS es de 15 V.