DRAM

En oposición a este concepto surge el de SRAM (RAM estática), con la que se denomina al tipo de tecnología RAM basada en semiconductores que, mientras siga alimentada, no necesita refresco.

[1] DRAM tuvo un aumento del 47 % en el precio por bit en 2017, el salto más grande en 30 años desde el salto del 45 % en 1988, mientras que en los últimos años el precio ha estado bajando.

[2] La memoria dinámica fue desarrollada en los laboratorios de IBM pasando por un proceso evolutivo que la llevó de usar 6 transistores a sólo un condensador y un transistor, como la memoria DRAM que conocemos hoy.

No hubo interés en comercializar ese tipo de memorias para otros fabricantes ni tampoco se pensó en usar las tecnologías de estado sólido tipo SRAM o DRAM para construir la memoria principal.

La producción y calidad del integrado era difícil de mantener, hecho que se demostró cuando Intel entregó parte de la producción a otra empresa llamada Microelectronics Integrated Limited (MIL) que en un principio pudo obtener mejores resultados que la misma Intel, pero después del cambio importante en el proceso de fabricación no fue capaz de producir.

[7] La memoria i1103 era muy primitiva en comparación a las DRAM de la actualidad, aun así se comportaba mejor que la memoria de núcleo y con un precio menor.

[10] Para 1973 Intel y otros fabricantes construían y empacaban sus integrados de DRAM empleando un esquema en el que se aumentaba un pin por cada vez que se doblaba la capacidad.

La solución a nivel de la celda conducía a un ahorro en el empaque, ya que la dirección podría recibirse en dos etapas, reduciendo la cantidad de pines usados.

El transistor funciona como un interruptor que conecta y desconecta al condensador.

Para acceder a una posición de memoria se necesita una dirección de 4 bits, pero en las DRAM las direcciones están multiplexadas en tiempo, es decir se envían por mitades.

Cada bit de datos en una DRAM se almacena como una carga eléctrica positiva o negativa en una estructura capacitiva.

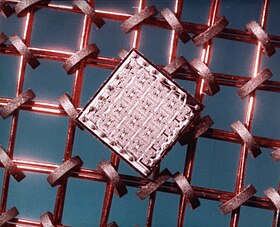

Son el bloque de construcción fundamental en las matrices DRAM.

En las DRAM modernas, un voltaje de +VCC/2 a través del condensador se requiere almacenar uno lógico; y un voltaje de -VCC/2 a través del condensador se requiere para almacenar un cero lógico.

Si el condensador contiene un cero lógico, comienza a descargarse cuando el voltaje del terminal de la puerta está por encima VTH.

El impulso para aumentar tanto la densidad como, en menor medida, el rendimiento, requería diseños más densos.