El multiprocesamiento simétrico o multiprocesamiento de memoria compartida [1] ( SMP ) implica una arquitectura de hardware y software de computadora multiprocesador donde dos o más procesadores idénticos están conectados a una única memoria principal compartida , tienen acceso completo a todos los dispositivos de entrada y salida y están controlados. por una única instancia de sistema operativo que trata a todos los procesadores por igual, sin reservar ninguno para propósitos especiales. La mayoría de los sistemas multiprocesador actuales utilizan una arquitectura SMP. En el caso de los procesadores multinúcleo , la arquitectura SMP se aplica a los núcleos, tratándolos como procesadores separados.

El profesor John D. Kubiatowicz considera que tradicionalmente los sistemas SMP contienen procesadores sin caché. [2] Culler y Pal-Singh en su libro de 1998 "Parallel Computer Architecture: A Hardware/Software Approach" mencionan: "El término SMP se usa ampliamente pero causa un poco de confusión. [...] La descripción más precisa de lo que Lo que pretende SMP es un multiprocesador de memoria compartida donde el costo de acceder a una ubicación de memoria es el mismo para todos los procesadores; es decir, tiene costos de acceso uniformes cuando el acceso en realidad es a la memoria. Si la ubicación está en caché, el acceso será más rápido, pero los tiempos de acceso a la caché y a la memoria son los mismos en todos los procesadores". [3]

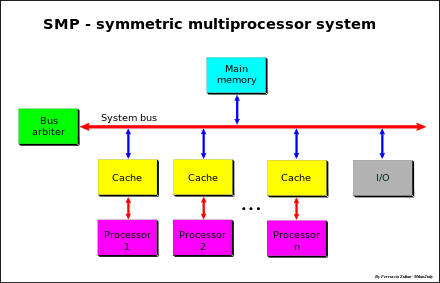

Los sistemas SMP son sistemas multiprocesador estrechamente acoplados con un conjunto de procesadores homogéneos que se ejecutan de forma independiente unos de otros. Cada procesador, que ejecuta diferentes programas y trabaja con diferentes conjuntos de datos, tiene la capacidad de compartir recursos comunes (memoria, dispositivo de E/S, sistema de interrupción, etc.) que están conectados mediante un bus del sistema o una barra transversal .

Los sistemas SMP cuentan con una memoria compartida centralizada denominada memoria principal (MM) que opera bajo un único sistema operativo con dos o más procesadores homogéneos. Normalmente cada procesador tiene asociada una memoria privada de alta velocidad conocida como memoria caché (o caché) para acelerar el acceso a los datos de la memoria principal y reducir el tráfico del bus del sistema.

Los procesadores pueden interconectarse mediante buses, conmutadores de barra transversal o redes de malla en chip. El cuello de botella en la escalabilidad de SMP utilizando buses o conmutadores de barra cruzada es el ancho de banda y el consumo de energía de la interconexión entre los distintos procesadores, la memoria y los conjuntos de discos. Las arquitecturas de malla evitan estos cuellos de botella y proporcionan una escalabilidad casi lineal a un número de procesadores mucho mayor sacrificando la programabilidad:

Este tipo de arquitectura plantea serios desafíos de programación porque requiere dos modos distintos de programación; uno para las propias CPU y otro para la interconexión entre las CPU. Un único lenguaje de programación tendría que ser capaz no sólo de dividir la carga de trabajo, sino también de comprender la localidad de la memoria, lo cual es grave en una arquitectura basada en malla. [4]

Los sistemas SMP permiten que cualquier procesador trabaje en cualquier tarea sin importar dónde se encuentren los datos para esa tarea en la memoria, siempre que cada tarea en el sistema no esté en ejecución en dos o más procesadores al mismo tiempo. Con el soporte adecuado del sistema operativo , los sistemas SMP pueden mover fácilmente tareas entre procesadores para equilibrar la carga de trabajo de manera eficiente.

El primer sistema de producción con múltiples procesadores idénticos fue el Burroughs B5000 , que estaba funcional alrededor de 1961. Sin embargo, en tiempo de ejecución era asimétrico , con un procesador restringido a programas de aplicación mientras que el otro procesador manejaba principalmente el sistema operativo y las interrupciones de hardware. El Burroughs D825 implementó SMP por primera vez en 1962. [5] [6]

IBM ofreció sistemas informáticos de doble procesador basados en su System/360 Modelo 65 y los estrechamente relacionados Modelo 67 [7] y 67-2. [8] Los sistemas operativos que se ejecutaban en estas máquinas eran OS/360 M65MP [9] y TSS/360 . Otro software desarrollado en universidades, en particular el Michigan Terminal System (MTS), utilizaba ambas CPU. Ambos procesadores podrían acceder a canales de datos e iniciar E/S. En OS/360 M65MP, los periféricos generalmente se podían conectar a cualquiera de los procesadores ya que el kernel del sistema operativo se ejecutaba en ambos procesadores (aunque con un "gran bloqueo" alrededor del controlador de E/S). [10] El supervisor MTS (UMMPS) tiene la capacidad de ejecutarse en ambas CPU del IBM System/360 modelo 67–2. Los bloqueos de supervisor eran pequeños y se usaban para proteger estructuras de datos comunes individuales a las que se podía acceder simultáneamente desde cualquiera de las CPU. [11]

Otros mainframes que soportaban SMP incluían el UNIVAC 1108 II , lanzado en 1965, que soportaba hasta tres CPU, y el GE-635 y el GE-645 , [12] [13] aunque GECOS en sistemas multiprocesador GE-635 se ejecutaba en un sistema maestro. -esclavo de forma asimétrica, a diferencia de Multics en sistemas multiprocesador GE-645, que se ejecutaban de forma simétrica. [14]

A partir de su versión 7.0 (1972), el sistema operativo TOPS-10 de Digital Equipment Corporation implementó la función SMP; el primer sistema que ejecutaba SMP fue el sistema de procesador dual KI10 DECSystem 1077 . [15] El sistema KL10 posterior podría agregar hasta 8 CPU en forma SMP. Por el contrario, el primer sistema VAX multiprocesador de DEC , el VAX-11/782, era asimétrico, [16] pero los sistemas multiprocesador VAX posteriores eran SMP. [17]

Las primeras implementaciones comerciales de Unix SMP incluyeron Sequent Computer Systems Balance 8000 (lanzado en 1984) y Balance 21000 (lanzado en 1986). [18] Ambos modelos se basaron en procesadores National Semiconductor NS32032 de 10 MHz , cada uno con una pequeña caché de escritura conectada a una memoria común para formar un sistema de memoria compartida . Otra implementación comercial temprana de Unix SMP fue el Honeywell Information Systems Italy XPS-100 basado en NUMA, diseñado por Dan Gielan de VAST Corporation en 1985. Su diseño admitía hasta 14 procesadores, pero debido a limitaciones eléctricas, la versión más grande comercializada fue un sistema de procesador dual. . El sistema operativo fue derivado y portado por VAST Corporation a partir del código AT&T 3B20 Unix SysVr3 utilizado internamente en AT&T.

Anteriormente existían puertos UNIX de multiprocesamiento no comerciales, incluido un puerto llamado MUNIX creado en la Escuela de Postgrado Naval en 1975. [19]

Los sistemas de tiempo compartido y de servidor a menudo pueden usar SMP sin cambios en las aplicaciones, ya que pueden tener múltiples procesos ejecutándose en paralelo, y un sistema con más de un proceso en ejecución puede ejecutar diferentes procesos en diferentes procesadores.

En computadoras personales , SMP es menos útil para aplicaciones que no han sido modificadas. Si el sistema rara vez ejecuta más de un proceso a la vez, SMP es útil sólo para aplicaciones que han sido modificadas para procesamiento multiproceso (multitarea). El software programado a medida se puede escribir o modificar para utilizar varios subprocesos, de modo que pueda utilizar varios procesadores.

Los programas multiproceso también se pueden utilizar en sistemas de tiempo compartido y de servidor que admitan subprocesos múltiples, lo que les permite hacer un mayor uso de múltiples procesadores.

En los sistemas SMP actuales, todos los procesadores están estrechamente acoplados dentro de la misma caja con un bus o conmutador; en sistemas SMP anteriores, una sola CPU ocupaba un gabinete completo. Algunos de los componentes que se comparten son la memoria global, los discos y los dispositivos de E/S. Sólo se ejecuta una copia de un sistema operativo en todos los procesadores y el sistema operativo debe diseñarse para aprovechar esta arquitectura. Algunas de las ventajas básicas implican formas rentables de aumentar el rendimiento. Para resolver diferentes problemas y tareas, SMP aplica múltiples procesadores a ese único problema, lo que se conoce como programación paralela .

Sin embargo, existen algunos límites en la escalabilidad de SMP debido a la coherencia de la caché y los objetos compartidos.

Los sistemas monoprocesador y SMP requieren diferentes métodos de programación para lograr el máximo rendimiento. Los programas que se ejecutan en sistemas SMP pueden experimentar un aumento en el rendimiento incluso cuando hayan sido escritos para sistemas monoprocesador. Esto se debe a que las interrupciones de hardware generalmente suspenden la ejecución del programa, mientras que el núcleo que las maneja puede ejecutarse en un procesador inactivo. El efecto en la mayoría de las aplicaciones (por ejemplo, juegos) no es tanto un aumento del rendimiento sino la apariencia de que el programa se ejecuta mucho mejor. Algunas aplicaciones, en particular la creación de software y algunos proyectos de computación distribuida , se ejecutan más rápido en un factor (casi) del número de procesadores adicionales. (Los compiladores en sí mismos son de un solo subproceso, pero, cuando se construye un proyecto de software con múltiples unidades de compilación, si cada unidad de compilación se maneja de forma independiente, esto crea una situación embarazosamente paralela en todo el proyecto de múltiples unidades de compilación, lo que permite un escalado casi lineal de la compilación. tiempo. Los proyectos de computación distribuida son inherentemente paralelos por diseño.)

Los programadores de sistemas deben incorporar soporte para SMP en el sistema operativo ; de lo contrario, los procesadores adicionales permanecen inactivos y el sistema funciona como un sistema monoprocesador.

Los sistemas SMP también pueden generar una mayor complejidad con respecto a los conjuntos de instrucciones. Un sistema de procesador homogéneo normalmente requiere registros adicionales para "instrucciones especiales" como SIMD (MMX, SSE, etc.), mientras que un sistema heterogéneo puede implementar diferentes tipos de hardware para diferentes instrucciones/usos.

Cuando se ejecuta más de un programa al mismo tiempo, un sistema SMP tiene un rendimiento considerablemente mejor que un monoprocesador, porque diferentes programas pueden ejecutarse en diferentes CPU simultáneamente. Por el contrario, el multiprocesamiento asimétrico (AMP) normalmente permite que sólo un procesador ejecute un programa o tarea a la vez. Por ejemplo, AMP se puede utilizar para asignar tareas específicas a la CPU según la prioridad y la importancia de la finalización de la tarea. AMP se creó mucho antes que SMP en términos de manejo de múltiples CPU, lo que explica la falta de rendimiento según el ejemplo proporcionado.

En los casos en que un entorno SMP procesa muchos trabajos, los administradores suelen experimentar una pérdida de eficiencia del hardware. Se han desarrollado programas de software para programar trabajos y otras funciones de la computadora de modo que la utilización del procesador alcance su máximo potencial. Los buenos paquetes de software pueden alcanzar este máximo potencial programando cada CPU por separado, además de poder integrar múltiples máquinas y clústeres SMP.

El acceso a la RAM está serializado; Esto y los problemas de coherencia de la caché hacen que el rendimiento quede ligeramente por detrás de la cantidad de procesadores adicionales en el sistema.

SMP utiliza un único bus de sistema compartido que representa uno de los primeros estilos de arquitecturas de máquinas multiprocesador, normalmente utilizado para construir computadoras más pequeñas con hasta 8 procesadores.

Los sistemas informáticos más grandes pueden utilizar arquitecturas más nuevas, como NUMA (Acceso a memoria no uniforme), que dedica diferentes bancos de memoria a diferentes procesadores. En una arquitectura NUMA, los procesadores pueden acceder a la memoria local rápidamente y a la memoria remota más lentamente. Esto puede mejorar drásticamente el rendimiento de la memoria siempre que los datos estén localizados en procesos específicos (y, por tanto, en procesadores). En el lado negativo, NUMA encarece el costo de mover datos de un procesador a otro, como en el equilibrio de la carga de trabajo. Los beneficios de NUMA se limitan a cargas de trabajo particulares, especialmente en servidores donde los datos a menudo están fuertemente asociados con ciertas tareas o usuarios.

Finalmente, existe el multiprocesamiento en clústeres de computadoras (como Beowulf ), en el que no toda la memoria está disponible para todos los procesadores. Las técnicas de agrupación en clústeres se utilizan bastante para construir supercomputadoras de gran tamaño.

El multiprocesamiento simétrico variable (vSMP) es una tecnología de casos de uso móvil específica iniciada por NVIDIA. Esta tecnología incluye un quinto núcleo adicional en un dispositivo de cuatro núcleos, llamado núcleo Companion, creado específicamente para ejecutar tareas a una frecuencia más baja durante el modo de espera activo móvil, reproducción de video y reproducción de música.

El Proyecto Kal-El ( Tegra 3 ), [20] patentado por NVIDIA, fue el primer SoC (System on Chip) en implementar esta nueva tecnología vSMP. Esta tecnología no sólo reduce el consumo de energía móvil durante el estado de espera activo, sino que también maximiza el rendimiento de cuatro núcleos durante el uso activo para aplicaciones móviles intensivas. En general, esta tecnología aborda la necesidad de aumentar la duración de la batería durante el uso activo y en espera al reducir el consumo de energía en los procesadores móviles.

A diferencia de las arquitecturas SMP actuales, el núcleo vSMP Companion es transparente para el sistema operativo, lo que significa que el sistema operativo y las aplicaciones en ejecución desconocen por completo este núcleo adicional, pero aún pueden aprovecharlo. Algunas de las ventajas de la arquitectura vSMP incluyen coherencia de caché, eficiencia del sistema operativo y optimización de energía. Las ventajas de esta arquitectura se explican a continuación:

Estas ventajas hacen que la arquitectura vSMP se beneficie considerablemente [ peacock prose ] sobre otras arquitecturas que utilizan tecnologías de sincronización asíncrona.