La aceleración de hardware es el uso de hardware informático diseñado para realizar funciones específicas de manera más eficiente en comparación con el software que se ejecuta en una unidad central de procesamiento (CPU) de uso general . Cualquier transformación de datos que se pueda calcular en un software que se ejecuta en una CPU genérica también se puede calcular en un hardware personalizado o en una combinación de ambos.

Para realizar tareas informáticas de manera más eficiente, generalmente se puede invertir tiempo y dinero en mejorar el software, mejorar el hardware o ambos. Existen varios enfoques con ventajas y desventajas en términos de disminución de la latencia , aumento del rendimiento y reducción del consumo de energía . Las ventajas típicas de centrarse en el software pueden incluir mayor versatilidad, desarrollo más rápido , menores costos de ingeniería no recurrentes , mayor portabilidad y facilidad para actualizar características o parchear errores , a costa de la sobrecarga para calcular operaciones generales. Las ventajas de centrarse en el hardware pueden incluir aceleración , menor consumo de energía , [1] menor latencia, mayor paralelismo [2] y ancho de banda , y mejor utilización del área y los componentes funcionales disponibles en un circuito integrado ; a costa de una menor capacidad para actualizar diseños una vez grabados en silicio y mayores costos de verificación funcional , tiempos de comercialización y la necesidad de más piezas. En la jerarquía de los sistemas informáticos digitales que van desde procesadores de propósito general hasta hardware totalmente personalizado , existe una compensación entre flexibilidad y eficiencia, y la eficiencia aumenta en órdenes de magnitud cuando una aplicación determinada se implementa más arriba en esa jerarquía. [3] Esta jerarquía incluye procesadores de propósito general como CPU, [4] procesadores más especializados como sombreadores programables en una GPU , [5] de función fija implementados en matrices de puertas programables en campo (FPGAs), [6] y de función fija implementados en circuitos integrados específicos de la aplicación (ASICs). [7]

La aceleración de hardware es ventajosa para el rendimiento y práctica cuando las funciones son fijas, por lo que las actualizaciones no son tan necesarias como en las soluciones de software. Con la llegada de dispositivos lógicos reprogramables como los FPGA, la restricción de la aceleración de hardware a algoritmos totalmente fijos se ha aliviado desde 2010, lo que permite que la aceleración de hardware se aplique a dominios problemáticos que requieren modificación de algoritmos y flujo de control de procesamiento . [8] [9] Sin embargo, la desventaja es que en muchos proyectos de código abierto, requiere bibliotecas propietarias que no todos los proveedores están dispuestos a distribuir o exponer, lo que dificulta la integración en dichos proyectos.

Los circuitos integrados están diseñados para manejar diversas operaciones tanto en señales analógicas como digitales. En informática, las señales digitales son las más comunes y suelen representarse como números binarios. El hardware y el software de las computadoras utilizan esta representación binaria para realizar cálculos. Esto se hace procesando funciones booleanas en la entrada binaria y luego enviando los resultados para su almacenamiento o posterior procesamiento por otros dispositivos.

Dado que todas las máquinas de Turing pueden ejecutar cualquier función computable , siempre es posible diseñar hardware personalizado que realice la misma función que un determinado programa informático. A la inversa, siempre se puede utilizar software para emular la función de un determinado programa informático. El hardware personalizado puede ofrecer un mayor rendimiento por vatio para las mismas funciones que se pueden especificar en el software. Los lenguajes de descripción de hardware (HDL) como Verilog y VHDL pueden modelar la misma semántica que el software y sintetizar el diseño en una lista de conexiones que se puede programar en un FPGA o integrar en las puertas lógicas de un ASIC.

La gran mayoría de la computación basada en software ocurre en máquinas que implementan la arquitectura de von Neumann , conocidas colectivamente como computadoras de programa almacenado . Los programas de computadora se almacenan como datos y son ejecutados por procesadores . Dichos procesadores deben buscar y decodificar instrucciones, así como cargar operandos de datos de la memoria (como parte del ciclo de instrucción ), para ejecutar las instrucciones que constituyen el programa de software. Confiar en una caché común para código y datos conduce al "cuello de botella de von Neumann", una limitación fundamental en el rendimiento del software en procesadores que implementan la arquitectura de von Neumann. Incluso en la arquitectura Harvard modificada , donde las instrucciones y los datos tienen cachés separados en la jerarquía de memoria , existe una sobrecarga para decodificar códigos de operación de instrucciones y multiplexar las unidades de ejecución disponibles en un microprocesador o microcontrolador , lo que lleva a una baja utilización del circuito. Los procesadores modernos que proporcionan subprocesos múltiples simultáneos explotan la subutilización de las unidades funcionales del procesador disponibles y el paralelismo a nivel de instrucción entre diferentes subprocesos de hardware.

Las unidades de ejecución de hardware no dependen en general de las arquitecturas de von Neumann o Harvard modificada y no necesitan realizar los pasos de búsqueda y decodificación de instrucciones de un ciclo de instrucciones ni incurrir en la sobrecarga de esas etapas. Si se especifican los cálculos necesarios en un diseño de hardware de nivel de transferencia de registros (RTL), los costos de tiempo y área de circuito que se generarían en las etapas de búsqueda y decodificación de instrucciones se pueden recuperar y destinar a otros usos.

Esta recuperación ahorra tiempo, energía y área de circuito en los cálculos. Los recursos recuperados se pueden utilizar para aumentar los cálculos en paralelo, otras funciones, la comunicación o la memoria, así como para aumentar las capacidades de entrada y salida . Esto se produce a costa de la utilidad de uso general.

Una mayor personalización RTL de los diseños de hardware permite que las arquitecturas emergentes, como la computación en memoria , las arquitecturas activadas por transporte (TTA) y las redes en chip (NoC), se beneficien aún más de una mayor localidad de los datos en el contexto de ejecución, reduciendo así la latencia de computación y comunicación entre módulos y unidades funcionales.

El hardware personalizado está limitado en su capacidad de procesamiento en paralelo únicamente por el área y los bloques lógicos disponibles en la matriz del circuito integrado . [10] Por lo tanto, el hardware es mucho más libre para ofrecer paralelismo masivo que el software en procesadores de propósito general, lo que ofrece la posibilidad de implementar el modelo de máquina de acceso aleatorio paralelo (PRAM).

Es común construir unidades de procesamiento multinúcleo y de muchos núcleos a partir de esquemas de núcleo IP de microprocesador en un solo FPGA o ASIC. [11] [12] [13] [14] [15] De manera similar, las unidades funcionales especializadas se pueden componer en paralelo, como en el procesamiento de señales digitales , sin estar integradas en un núcleo IP de procesador . Por lo tanto, la aceleración de hardware se emplea a menudo para tareas repetitivas y fijas que implican poca ramificación condicional , especialmente en grandes cantidades de datos. Así es como se implementa la línea CUDA de GPU de Nvidia .

A medida que ha aumentado la movilidad de los dispositivos, se han desarrollado nuevas métricas que miden el rendimiento relativo de protocolos de aceleración específicos, teniendo en cuenta características como las dimensiones físicas del hardware, el consumo de energía y el rendimiento de las operaciones. Estas pueden resumirse en tres categorías: eficiencia de la tarea, eficiencia de la implementación y flexibilidad. Las métricas adecuadas consideran el área del hardware junto con el rendimiento de las operaciones correspondientes y la energía consumida. [16]

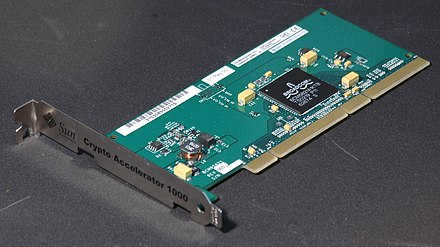

Los ejemplos de aceleración de hardware incluyen la funcionalidad de aceleración bit blit en unidades de procesamiento gráfico (GPU), el uso de memristores para acelerar redes neuronales y la aceleración de hardware de expresiones regulares para el control de spam en la industria de servidores , destinada a prevenir ataques de denegación de servicio de expresiones regulares (ReDoS). [17] El hardware que realiza la aceleración puede ser parte de una CPU de propósito general o una unidad separada llamada acelerador de hardware, aunque generalmente se los conoce con un término más específico, como acelerador 3D o acelerador criptográfico .

Tradicionalmente, los procesadores eran secuenciales (las instrucciones se ejecutaban una por una) y estaban diseñados para ejecutar algoritmos de propósito general controlados por la obtención de instrucciones (por ejemplo, mover resultados temporales hacia y desde un archivo de registros ). Los aceleradores de hardware mejoran la ejecución de un algoritmo específico al permitir una mayor concurrencia , tener rutas de datos específicas para sus variables temporales y reducir la sobrecarga del control de instrucciones en el ciclo de obtención-decodificación-ejecución.

Los procesadores modernos son multinúcleo y a menudo cuentan con unidades paralelas de "instrucción única; múltiples datos" ( SIMD ). Aun así, la aceleración de hardware sigue ofreciendo ventajas. La aceleración de hardware es adecuada para cualquier algoritmo de cálculo intensivo que se ejecute con frecuencia en una tarea o programa. Según la granularidad, la aceleración de hardware puede variar desde una pequeña unidad funcional hasta un gran bloque funcional (como la estimación de movimiento en MPEG-2 ).

La simulación de hardware en FPGA aumentó el rendimiento del filtro digital.