La familia PowerPC 600 fue la primera familia de procesadores PowerPC que se construyó. Fueron diseñados en las instalaciones de Somerset en Austin, Texas , financiadas y dotadas de personal de manera conjunta por ingenieros de IBM y Motorola como parte de la alianza AIM . Somerset se inauguró en 1992 y su objetivo era fabricar el primer procesador PowerPC y luego seguir diseñando procesadores PowerPC de propósito general para computadoras personales . La primera encarnación se convirtió en el PowerPC 601 en 1993, y pronto siguió la segunda generación con el PowerPC 603, el PowerPC 604 y el PowerPC 620 de 64 bits.

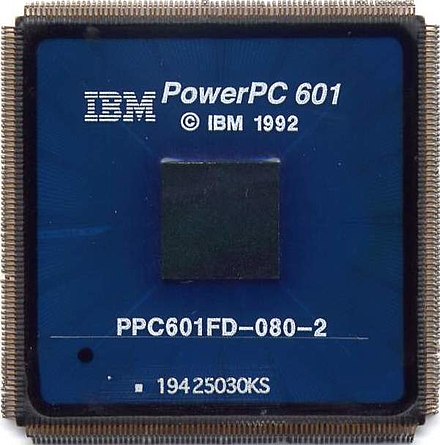

El PowerPC 601 fue la primera generación de microprocesadores que admitieron el conjunto básico de instrucciones PowerPC de 32 bits . El esfuerzo de diseño comenzó en serio a mediados de 1991 y los primeros chips prototipo estuvieron disponibles en octubre de 1992. Los primeros procesadores 601 se introdujeron en una estación de trabajo IBM RS/6000 en octubre de 1993 (junto con su primo multichip más potente , la línea de procesadores IBM POWER2 ) y los primeros Apple Power Macintosh el 14 de marzo de 1994. El 601 fue la primera implementación avanzada de un solo chip de la arquitectura POWER/PowerPC diseñada según un cronograma de choque para establecer PowerPC en el mercado y consolidar la alianza AIM. Para lograr un cronograma extremadamente agresivo al tiempo que se incluía una funcionalidad sustancialmente nueva (como mejoras sustanciales de rendimiento, nuevas instrucciones y, lo que es más importante, la primera implementación de multiprocesamiento simétrico (SMP) de POWER/PowerPC), el diseño aprovechó una serie de tecnologías clave y estrategias de gestión de proyectos. El equipo 601 aprovechó gran parte de la estructura básica y partes del procesador IBM RISC Single Chip (RSC), [1] pero también incluyó soporte para la gran mayoría de las nuevas instrucciones PowerPC que no estaban en el conjunto de instrucciones POWER . Si bien se modificó casi cada parte del diseño RSC, y muchos bloques de diseño se modificaron sustancialmente o se rediseñaron por completo dada la estructura de bus de E/S unificada completamente diferente y el soporte de coherencia de memoria /SMP . Nuevos cambios de PowerPC, aprovechar la estructura básica de RSC fue muy beneficioso para reducir la incertidumbre en el área del chip/planificación de piso y el análisis/ajuste de tiempos. Vale la pena destacar que el 601 no solo implementó nuevas funciones clave sustanciales como SMP, sino que también actuó como un puente entre POWER y los futuros procesadores PowerPC para ayudar a IBM y a los desarrolladores de software en sus transiciones a PowerPC. Desde el inicio del diseño hasta la producción en cinta del primer prototipo 601 fueron solo 12 meses para presionar con fuerza para establecer PowerPC en el mercado temprano.

Para ayudar a la rápida incorporación de la arquitectura de bus 88110 al 601 en beneficio de la alianza y sus clientes, la gerencia de Motorola proporcionó no sólo las especificaciones de la arquitectura de bus 88110, sino también un puñado de diseñadores expertos en bus 88110 para ayudar con la implementación y verificación de la lógica del bus 60x. Dado que el equipo de diseño del sistema de Apple estaba familiarizado con la estructura del bus de E/S del 88110 de Motorola y esta implementación del bus de E/S estaba bien definida y documentada, el equipo del 601 adoptó la tecnología de bus para mejorar el tiempo de comercialización. El bus pasó a denominarse bus 60x una vez implementado en el 601. [2] Estos diseñadores de Motorola (y un pequeño número de Apple) se unieron a más de 120 diseñadores de IBM para crear el 601.

El uso del bus 88110 como base para el bus 60x ayudó a los cronogramas de varias maneras. Ayudó al equipo Apple Power Macintosh al reducir la cantidad de rediseño de sus ASIC de soporte y redujo la cantidad de tiempo requerido para que los diseñadores y arquitectos de procesadores propusieran, documentaran, negociaran y cerraran una nueva interfaz de bus (evitando con éxito las "Guerras de Bus" esperadas por el equipo de administración del 601 si no se hubiera adoptado el bus 88110 o los buses RSC anteriores). Vale la pena señalar que la aceptación del bus 88110 para el beneficio de los esfuerzos de Apple y la alianza se hizo a expensas de los esfuerzos del primer equipo de diseño del sistema IBM RS/6000, que ya tenía sus ASIC de soporte implementados en torno a la estructura de bus totalmente diferente del RSC.

Este bus 60x más tarde se convirtió en una interfaz básica de larga duración para las numerosas variantes de los procesadores 601, 603, 604, G3 , G4 y Motorola/Freescale PowerQUICC .

El chip fue diseñado para adaptarse a una amplia variedad de aplicaciones y tenía soporte para caché L2 externa y multiprocesamiento simétrico . Tenía cuatro unidades funcionales, incluida una unidad de punto flotante , una unidad de enteros , una unidad de ramificación y una unidad de secuenciador. El procesador también incluía una unidad de gestión de memoria . La tubería de enteros tenía cuatro etapas de longitud, la tubería de ramificación dos etapas de longitud, la tubería de memoria cinco etapas de longitud y la tubería de punto flotante seis etapas de longitud.

Lanzado por primera vez en sistemas IBM en el otoño de 1993, fue comercializado por IBM como PPC601 y por Motorola como MPC601. Operaba a velocidades que iban de 50 a 80 MHz. Se fabricó utilizando un proceso CMOS de 0,6 μm con cuatro niveles de interconexión de aluminio . La matriz tenía 121 mm2 de largo y contenía 2,8 millones de transistores. El 601 tiene una caché L1 unificada de 32 KB , una capacidad que se consideró grande en ese momento para una caché en chip. Gracias en parte a la gran caché, se consideró un procesador de alto rendimiento en su segmento, superando al Intel Pentium de la competencia . El PowerPC 601 se utilizó en las primeras computadoras Power Macintosh de Apple , y en una variedad de estaciones de trabajo RS/6000 y servidores SMP de IBM y Groupe Bull .

IBM fue el único fabricante de los microprocesadores 601 y 601+ en sus instalaciones de producción de Burlington, Vermont y East Fishkill, Nueva York . El 601 utilizaba el proceso IBM CMOS-4s y el 601+ utilizaba el proceso IBM CMOS-5x. Una cantidad extremadamente pequeña de estos procesadores 601 y 601+ fueron reetiquetados con logotipos y números de pieza de Motorola y distribuidos a través de Motorola. Estos hechos están un tanto oscurecidos debido a que existen varias fotografías del "Motorola MPC601", en particular un caso específico de marketing magistral de Motorola donde el 601 fue nombrado uno de los "Productos del año" de 1994 por la revista Time con una marca de Motorola.

En 1994 se introdujo una versión actualizada, la PowerPC 601v o PowerPC 601+ , que funcionaba entre 90 y 120 MHz. Se fabricó con un proceso CMOS de 0,5 μm más nuevo con cuatro niveles de interconexión, lo que dio como resultado una matriz de 74 mm2 . El diseño de la 601+ fue reasignado de CMOS-4s a CMOS-5x por un equipo exclusivo de IBM. Para evitar retrasos en el tiempo de comercialización debido a cambios en las herramientas de diseño y la puesta en común de las reglas básicas de fabricación, tanto la 601 como la 601+ se diseñaron con herramientas EDA de IBM en sistemas IBM y se fabricaron en instalaciones exclusivas de IBM. [3] [4] [5] [6]

El PowerPC 603 fue el primer procesador que implementó la arquitectura PowerPC de 32 bits completa tal como se especifica. Introducido en 1994, fue un diseño avanzado para su época, siendo uno de los primeros microprocesadores en ofrecer emisión dual (hasta tres con plegado de ramas) y ejecución fuera de orden combinada con un bajo consumo de energía de 2,2 W y un pequeño chip de 85 mm 2 . [7] [8] [9] [10] Fue diseñado para ser un procesador de bajo costo y bajo consumo para aplicaciones portátiles. Una de las principales características eran las funciones de ahorro de energía (modo doze, nap y sleep) que podían reducir drásticamente los requisitos de energía, consumiendo solo 2 mW en modo sleep. El 603 tiene una tubería de cuatro etapas y cinco unidades de ejecución: unidad de enteros, unidad de punto flotante, unidad de predicción de ramas , unidad de carga/almacenamiento y una unidad de registro del sistema. Tiene cachés L1 separados de 8 KB para instrucciones y datos y un bus de memoria 60x de 32/64 bits, que alcanza hasta 120 MHz a 3,8 V. [10] El núcleo 603 no tenía soporte de hardware para SMP .

El PowerPC 603 tenía 1,6 millones de transistores y fue fabricado por IBM y Motorola en un proceso CMOS de 0,5 μm con cuatro niveles de interconexión. La matriz tenía un tamaño de 85 mm2 y consumía 2,2 W a 80 MHz. [10] [11] La arquitectura 603 es el antecesor directo de la arquitectura PowerPC 750 , comercializada por Apple como PowerPC "G3".

El 603 fue pensado para ser usado en computadoras portátiles Apple Macintosh pero no podía ejecutar software de emulación de 68K con un rendimiento que Apple consideraba adecuado, debido a los cachés de procesador más pequeños. Como resultado, Apple eligió usar el 603 solo en su línea Performa de escritorio de bajo costo. [12] [13] Esto causó el retraso del Apple PowerBook 5300 y PowerBook Duo 2300 , ya que Apple decidió esperar una revisión del procesador. El uso del 603 por parte de Apple en la línea Performa 5200 llevó a que el procesador obtuviera una mala reputación. Aparte del problema del rendimiento de emulación de 68K, las máquinas Performa se entregaron con una variedad de fallas de diseño, algunas de ellas graves, relacionadas con otros aspectos del diseño de las computadoras, incluido el rendimiento y la estabilidad de la red, problemas de bus (ancho, velocidad, contención y complejidad), errores de ROM y rendimiento del disco duro. [14] [15] Ninguno de los problemas de la línea 5200, aparte del rendimiento de la emulación 68K, se debió inherentemente al 603. Más bien, el procesador fue adaptado para ser utilizado con placas base 68K y otras piezas obsoletas. [16] El sitio Low End Mac califica al Performa 5200 como el peor Mac de todos los tiempos. [17] El 603 encontró un uso generalizado en diferentes dispositivos integrados. [ cita requerida ]

Los problemas de rendimiento del 603 se solucionaron en el PowerPC 603e . La caché L1 se amplió y mejoró a 16 KB de cachés de datos e instrucciones asociativas de cuatro vías. La velocidad de reloj de los procesadores también se duplicó, alcanzando los 200 MHz. La reducción del proceso de fabricación a 350 nm permitió velocidades de hasta 300 MHz. Esta parte a veces se llama PowerPC 603ev . El 603e y el 603ev tienen 2,6 millones de transistores cada uno y tienen un tamaño de 98 mm2 y 78 mm2 respectivamente . El 603ev consume un máximo de 6 W a 300 MHz. [18] [19]

El PowerPC 603e fue el primer procesador de escritorio convencional en alcanzar los 300 MHz, como el utilizado en el Power Macintosh 6500. El 603e también se utilizó en tarjetas aceleradoras de Phase5 para la línea de computadoras Amiga , con CPU que variaban en velocidades de 160 a 240 MHz. El PowerPC 603e todavía se vende hoy en día por IBM y Freescale, y otros como Atmel y Honeywell , que fabrica la variante reforzada con radiación RHPPC . El PowerPC 603e también fue el corazón del BeBox de Be Inc. El BeBox es notable porque es un sistema de multiprocesamiento , algo para lo que el 603 no fue diseñado. IBM también utilizó procesadores PowerPC 603e en la serie IBM ThinkPad 800. En ciertas series de osciloscopios digitales, LeCroy utilizó el PowerPC 603e como procesador principal. [20] [21] Los procesadores 603e también alimentan a los 66 satélites de la flota de teléfonos satelitales Iridium . Cada satélite contiene siete procesadores Motorola/Freescale PowerPC 603e que funcionan a aproximadamente 200 MHz cada uno. También se utiliza un procesador 603e personalizado en el Mark 54 Lightweight Torpedo .

El núcleo PowerPC 603e, rebautizado como G2 por Freescale , es la base de muchos procesadores PowerQUICC II integrados y, como tal, sigue desarrollándose. Los procesadores SoC PowerQUICC II de Freescale llevan la designación MPC82xx y vienen en una variedad de configuraciones que alcanzan los 450 MHz. El nombre G2 también se utiliza como retrónimo de los procesadores 603e y 604 para alinearse con los G3, G4 y G5.

Freescale ha mejorado el núcleo 603e, llamándolo e300 , en los procesadores integrados PowerQUICC II Pro . Se añadieron cachés L1 más grandes de 32/32 KB y otras medidas de mejora del rendimiento. Los procesadores SoC PowerQUICC II Pro de Freescale llevan la designación MPC83xx y vienen en una variedad de configuraciones que alcanzan velocidades de hasta 667 MHz. El e300 también es el núcleo del procesador SoC MPC5200B que se utiliza en el pequeño ordenador EFIKA .

El PowerPC 604 se presentó en diciembre de 1994 junto con el 603 y fue diseñado como un chip de alto rendimiento para estaciones de trabajo y servidores de nivel básico y, como tal, tenía soporte para multiprocesamiento simétrico en hardware. El 604 se utilizó ampliamente en los sistemas de gama alta de Apple y también se utilizó en clones de Macintosh , servidores y estaciones de trabajo RS/6000 de gama baja de IBM , placas aceleradoras Amiga y como CPU integrada para aplicaciones de telecomunicaciones.

El 604 es un procesador superescalar capaz de emitir cuatro instrucciones simultáneamente. El 604 tiene un pipeline de seis etapas y seis unidades de ejecución que pueden trabajar en paralelo, terminando hasta seis instrucciones en cada ciclo. Dos unidades de enteros simples y una compleja , una unidad de punto flotante , una unidad de procesamiento de ramificación que gestiona la ejecución fuera de orden y una unidad de carga/almacenamiento. Tiene cachés L1 de datos e instrucciones de 16 KB independientes. La interfaz externa es un bus 60x de 32 o 64 bits que funciona a velocidades de reloj de hasta 50 MHz.

El PowerPC 604 contiene 3,6 millones de transistores y fue fabricado por IBM y Motorola con un proceso CMOS de 0,5 μm con cuatro niveles de interconexión. La matriz medía 12,4 mm por 15,8 mm (196 mm 2 ) y consumía entre 14 y 17 W a 133 MHz. Operaba a velocidades entre 100 y 180 MHz. [22] [23] [24]

El PowerPC 604e se presentó en julio de 1996 y agregó una unidad de registro de condición y cachés L1 de 32 KB de datos e instrucciones independientes, entre otros cambios en su subsistema de memoria y unidad de predicción de saltos, lo que resultó en un aumento del rendimiento del 25% en comparación con su predecesor. Tenía 5,1 millones de transistores y fue fabricado por IBM y Motorola en un proceso CMOS de 0,35 μm con cinco niveles de interconexión. La matriz tenía un tamaño de 148 mm2 o 96 mm2 , fabricada por Motorola e IBM respectivamente, y consumía entre 16 y 18 W a 233 MHz. Operaba a velocidades entre 166 y 233 MHz y admitía un bus de memoria de hasta 66 MHz. [25] [26]

El PowerPC 604ev , 604r o "Mach 5" se presentó en agosto de 1997 y era esencialmente un 604e fabricado por IBM y Motorola con un proceso más nuevo, alcanzando velocidades más altas con un menor consumo de energía. La matriz tenía un tamaño de 47 mm2 fabricada en un proceso CMOS de 0,25 μm con cinco niveles de interconexión y consumía 6 W a 250 MHz. Operaba a velocidades entre 250 y 400 MHz y admitía un bus de memoria de hasta 100 MHz.

Aunque Apple abandonó el 604ev en 1998 en favor del PowerPC 750 , IBM siguió utilizándolo en los modelos de nivel básico de sus computadoras RS/6000 durante varios años.

El PowerPC 620 fue la primera implementación de toda la arquitectura PowerPC de 64 bits . Era un PowerPC de segunda generación junto con el 603 y el 604, pero orientado al mercado de servidores y estaciones de trabajo de gama alta. Era potente sobre el papel y se suponía que se lanzaría junto con sus hermanos, pero se retrasó hasta 1997. Cuando llegó, el rendimiento era comparativamente pobre y el 604e, considerablemente más económico, lo superó. [27] Por lo tanto, el 620 nunca se produjo en grandes cantidades y encontró muy poco uso. El único usuario del PowerPC 620 fue Groupe Bull en sus máquinas Escala UNIX , pero no entregaron grandes cantidades. IBM, que tenía la intención de usarlo en estaciones de trabajo y servidores, decidió esperar a los procesadores RS64 y POWER3 de 64 bits, aún más potentes .

El 620 fue producido por Motorola en un proceso de 0,5 μm. Tenía 6,9 millones de transistores y la matriz tenía un área de 311 mm2 . Operaba a frecuencias de reloj de entre 120 y 150 MHz y consumía 30 W a 133 MHz. Se construyó un modelo posterior utilizando un proceso de 0,35 μm, lo que le permitió alcanzar los 200 MHz. [ se necesita más explicación ]

El 620 era similar al 604. Tiene una tubería de cinco etapas, el mismo soporte para multiprocesamiento simétrico y el mismo número de unidades de ejecución: una unidad de carga/almacenamiento, una unidad de ramificación, una FPU y tres unidades de enteros. Con cachés de instrucciones y datos más grandes de 32 KB, soporte para una caché L2 que puede tener una capacidad de 128 MB y unidades de ramificación y carga/almacenamiento más potentes que tenían más buffers, el 620 era muy poderoso. La tabla de historial de ramificaciones también era más grande y podía enviar más instrucciones para que el procesador pudiera manejar la ejecución fuera de orden de manera más eficiente que el 604. La unidad de punto flotante también se mejoró en comparación con el 604. Con un ciclo de búsqueda más rápido y soporte para varias instrucciones clave en hardware (como sqrt) lo hizo, combinado con buses de datos más rápidos y más amplios, más eficiente que la FPU en el 604. [ se necesita más explicación ]

El bus del sistema era un bus de memoria de 128 bits más amplio y rápido llamado bus 6XX . Fue diseñado para ser un bus de sistema para sistemas multiprocesador donde se conectarían procesadores, cachés, memoria y E/S, asistidos por un chip de control del sistema. Admite procesadores PowerPC de 32 y 64 bits, direcciones de memoria mayores a 32 bits y entornos NUMA . También se utilizó en POWER3, RS64 y 601, así como en sistemas RS/6000 basados en 604 (con un chip puente). [28] El bus evolucionó más tarde al bus GX del POWER4 , y más tarde al GX+ y GX++ en POWER5 y POWER6 respectivamente. El bus GX también se utiliza en los mainframes System z10 y z196 de IBM .

El PowerPC 602 era una versión reducida del PowerPC 603, especialmente diseñado para consolas de juegos por Motorola e IBM, presentado en febrero de 1995. [29] Tiene cachés L1 más pequeños (4 KB de instrucciones y 4 KB de datos), una unidad de punto flotante de precisión simple [29] y una unidad de predicción de ramificación reducida. Se ofrecía a velocidades que iban de 50 a 80 MHz y consumía 1,2 W a 66 MHz. Constaba de 1 millón de transistores y tenía 50 mm2 de tamaño, fabricado en un proceso CMOS de 0,5 μm con cuatro niveles de interconexión. [30]

3DO desarrolló la consola de juegos M2 que utilizaba dos PowerPC 602, [29] [31] pero nunca se comercializó.

El 21 de octubre de 1996, la empresa de semiconductores Quantum Effect Devices (QED) anunció un procesador compatible con PowerPC 603 llamado " PowerPC 603q " en el Microprocessor Forum . A pesar de su nombre, no tenía nada en común con ningún otro 603. Era una implementación desde cero de la arquitectura PowerPC de 32 bits dirigida al mercado de sistemas integrados de alta gama desarrollado a lo largo de dos años. Como tal, era pequeño, simple, energéticamente eficiente, pero potente; igualaba al 603e más caro pero consumía menos energía. Tenía una tubería de cinco etapas en orden con una sola unidad de números enteros, una unidad de punto flotante (FPU) de doble precisión y cachés de datos de 8 KB e instrucciones independientes. Si bien la unidad de números enteros era un diseño completamente nuevo, la FPU se derivaba del R4600 para ahorrar tiempo. Tenía un tamaño de 69 mm2 utilizando un proceso de fabricación de 0,5 μm y consumía solo 1,2 W a 120 MHz. [32] [33]

El 603q fue diseñado para Motorola, pero esta se retiró del contrato antes de que el 603q entrara en plena producción. Como resultado, el 603q fue cancelado ya que QED no podía seguir comercializando el procesador ya que carecía de una licencia PowerPC propia.

"PowerPC 613" parece ser el nombre que Motorola le había dado a un PowerPC de tercera generación. [34] [35] [36] Supuestamente fue renombrado " PowerPC 750 " en respuesta al procesador x704 de Exponential Technology que fue diseñado para superar al 604 por un amplio margen. Sin embargo, casi no hay fuentes que confirmen nada de esto y podría ser pura especulación o una referencia a un procesador completamente diferente.

Similar al PowerPC 613, el "PowerPC 614" podría haber sido un nombre dado por Motorola a un PowerPC de tercera generación, [34] [36] y luego renombrado por la misma razón que 613. Se ha sugerido que la pieza fue renombrada " PowerPC 7400 ", y Motorola incluso lo elevó a la cuarta generación de PowerPC a pesar de que las diferencias arquitectónicas entre "G3" y "G4" eran pequeñas. Sin embargo, casi no hay fuentes que confirmen nada de esto y podría ser pura especulación, o una referencia a un procesador completamente diferente.

El " PowerPC 615 " es un procesador PowerPC anunciado por IBM en 1994, pero que nunca llegó a producirse en masa . Su característica principal era incorporar un núcleo x86 en la matriz, lo que hacía que el procesador fuera capaz de procesar de forma nativa tanto instrucciones PowerPC como x86. [37] Un sistema operativo que se ejecutase en el PowerPC 615 podía elegir ejecutar instrucciones PowerPC de 32 o 64 bits, instrucciones x86 de 32 bits o una mezcla de las tres. Mezclar instrucciones implicaría un cambio de contexto en la CPU con una pequeña sobrecarga. Los únicos sistemas operativos que soportaban el 615 eran Minix y una versión de desarrollo especial de OS/2 . [38]

Tenía 330 mm2 de tamaño y era fabricado por IBM con un proceso de 0,35 μm. Era compatible con los procesadores Pentium de Intel y comparable en velocidad. El procesador se presentó solo como un prototipo y el programa fue eliminado en parte por el hecho de que Microsoft nunca dio soporte al procesador. Los ingenieros que trabajaban en el PowerPC 615 encontrarían más tarde su camino hacia Transmeta , donde trabajaron en el procesador Crusoe . Con el progreso demostrado en el desarrollo de software de traducción dinámica, como la tecnología FX!32 de Digital, se expresó escepticismo sobre la dedicación de recursos de hardware para ejecutar binarios extranjeros cuando dichos recursos podrían usarse para mejorar el rendimiento nativo, lo que también beneficia el rendimiento de los binarios traducidos. [39] : 94

"PowerPC 625" fue el nombre inicial de los procesadores PowerPC de 64 bits de la serie Apache, diseñados por IBM basándose en el conjunto de instrucciones PowerPC-AS de "Amazon". Posteriormente se los rebautizó como " RS64 ". La designación "PowerPC 625" nunca se utilizó para los procesadores finales.

"PowerPC 630" fue el nombre inicial del procesador PowerPC de 64 bits de gama alta, diseñado por IBM para unificar los conjuntos de instrucciones POWER y PowerPC . Más tarde se lo renombró " POWER3 ", probablemente para distinguirlo de los procesadores "PowerPC" más orientados al consumidor utilizados por Apple .

"PowerPC 641" , cuyo nombre en código es Habanero , es un proyecto PowerPC abandonado de IBM entre 1994 y 1996. Se ha sugerido que era la tercera generación de PowerPC basada en el procesador 604. [40] [41]

Las diminutas cachés de 8K del 603 eran notoriamente deficientes para el software de Mac OS, particularmente para la emulación de 68K; incluso las cachés del 603e causan una pérdida significativa de rendimiento a velocidades de reloj más altas. Dado el objetivo de diseño de Arthur de 250 MHz y más, duplicar las cachés nuevamente tenía sentido.