IA-64 ( arquitectura Intel Itanium ) es la arquitectura de conjunto de instrucciones (ISA) de la descontinuada familia Itanium de microprocesadores Intel de 64 bits . La especificación ISA básica se originó en Hewlett-Packard (HP) y posteriormente fue implementada por Intel en colaboración con HP. El primer procesador Itanium, con nombre en código Merced , fue lanzado en 2001.

La arquitectura Itanium se basa en un paralelismo explícito a nivel de instrucciones , en el que el compilador decide qué instrucciones ejecutar en paralelo. Esto contrasta con las arquitecturas superescalares , que dependen del procesador para gestionar las dependencias de las instrucciones en tiempo de ejecución. En todos los modelos Itanium, hasta Tukwila inclusive , los núcleos ejecutan hasta seis instrucciones por ciclo de reloj .

En 2008, Itanium fue la cuarta arquitectura de microprocesador más implementada para sistemas de clase empresarial , detrás de x86-64 , Power ISA y SPARC . [1]

En 2019, Intel anunció la descontinuación de la última de las CPU que soportan la arquitectura IA-64.

En 1989, HP comenzó a preocuparse de que las arquitecturas de computación con conjunto de instrucciones reducido (RISC) se estuvieran acercando a un límite de procesamiento de una instrucción por ciclo . Tanto los investigadores de Intel como los de HP habían estado explorando opciones de arquitectura informática para diseños futuros y por separado comenzaron a investigar un nuevo concepto conocido como palabra de instrucción muy larga (VLIW) [2] que surgió de una investigación realizada por la Universidad de Yale a principios de los años 1980. [3]

VLIW es un concepto de arquitectura informática (como RISC y CISC ) donde una sola palabra de instrucción contiene múltiples instrucciones codificadas en una palabra de instrucción muy larga para facilitar que el procesador ejecute múltiples instrucciones en cada ciclo de reloj. Las implementaciones típicas de VLIW dependen en gran medida de compiladores sofisticados para determinar en el momento de la compilación qué instrucciones se pueden ejecutar al mismo tiempo y la programación adecuada de estas instrucciones para su ejecución y también para ayudar a predecir la dirección de las operaciones de rama. El valor de este enfoque es realizar un trabajo más útil en menos ciclos de reloj y simplificar la programación de instrucciones del procesador y los requisitos de hardware de predicción de bifurcaciones, con la penalización de una mayor complejidad, costo y consumo de energía del procesador a cambio de una ejecución más rápida.

Durante este tiempo, HP había comenzado a creer que ya no era rentable para empresas de sistemas empresariales individuales como ella desarrollar microprocesadores propietarios. Intel también había estado investigando varias opciones arquitectónicas para ir más allá de la ISA x86 y abordar los requisitos de servidores empresariales de alta gama y de computación de alto rendimiento (HPC).

Intel y HP se asociaron en 1994 para desarrollar el IA-64 ISA, utilizando una variación de los conceptos de diseño VLIW que Intel denominó explícitamente computación de instrucciones paralelas (EPIC). El objetivo de Intel era aprovechar la experiencia que HP había desarrollado en sus primeros trabajos VLIW junto con la suya propia para desarrollar una línea de productos en volumen dirigida a los sistemas de alta gama antes mencionados que pudieran venderse a todos los fabricantes de equipos originales (OEM), mientras que HP deseaba poder comprar procesadores disponibles en el mercado construidos utilizando la fabricación en volumen y la tecnología de proceso contemporánea de Intel que eran mejores que sus procesadores PA-RISC.

Intel tomó la iniciativa en el proceso de diseño y comercialización, mientras que HP contribuyó a la definición de ISA, la microarquitectura Merced/Itanium e Itanium 2. El año objetivo original para entregar el primer producto de la familia Itanium, Merced, era 1998. [2]

Los esfuerzos de Intel en marketing de productos y participación de la industria fueron sustanciales y lograron avances en el diseño con la mayoría de los OEM de servidores empresariales, incluidos aquellos basados en procesadores RISC en ese momento. Los analistas de la industria predijeron que IA-64 dominaría los servidores, estaciones de trabajo y computadoras de escritorio de alta gama y eventualmente suplantaría las arquitecturas RISC y CISC para todas las aplicaciones de propósito general. [4] [5] Compaq y Silicon Graphics decidieron abandonar el desarrollo de las arquitecturas Alpha y MIPS respectivamente a favor de migrar a IA-64. [6]

En 1997, era evidente que la arquitectura IA-64 y el compilador eran mucho más difíciles de implementar de lo que se pensaba originalmente, y la entrega de Itanium comenzó a fallar. [7] Dado que Itanium fue el primer procesador EPIC, el esfuerzo de desarrollo encontró más problemas imprevistos de los que el equipo estaba acostumbrado. Además, el concepto EPIC dependía de capacidades del compilador que nunca antes se habían implementado, por lo que se necesitaba más investigación. [8]

Varios grupos desarrollaron sistemas operativos para la arquitectura, incluidos Microsoft Windows , Unix y sistemas similares a Unix como Linux , HP-UX , FreeBSD , Solaris , [9] [10] [11] Tru64 UNIX , [6] y Monterey/64. [12] (los tres últimos fueron cancelados antes de llegar al mercado). En 1999, Intel lideró la formación de un consorcio industrial de código abierto para portar Linux a IA-64 al que llamaron "Trillium" (y luego rebautizado como "Trillian" debido a un problema de marca), que fue dirigido por Intel e incluía a Caldera Systems . CERN , Soluciones Cygnus , Hewlett-Packard, IBM, Red Hat , SGI , SuSE , TurboLinux y VA Linux Systems . Como resultado, se entregó antes de lo previsto un IA-64 Linux funcional y fue el primer sistema operativo que se ejecutó en los nuevos procesadores Itanium.

Intel anunció el nombre oficial del procesador, Itanium , el 4 de octubre de 1999. [13] En cuestión de horas, el nombre Itanic había sido acuñado en un grupo de noticias de Usenet como un juego de palabras con el nombre Titanic , el transatlántico "insumergible" que se hundió en su viaje inaugural en 1912. [14]

Al día siguiente, el 5 de octubre de 1999, AMD anunció sus planes de ampliar el conjunto de instrucciones x86 de Intel para incluir un modo de 64 bits totalmente compatible con versiones anteriores, revelando además la nueva arquitectura x86 de 64 bits de AMD, en la que la empresa ya había trabajado, para se incorporará al próximo microprocesador de octava generación de AMD, cuyo nombre en código es SledgeHammer . [15] AMD también anunció una divulgación completa de las especificaciones de la arquitectura y más detalles que estarían disponibles en agosto de 2000. [16]

Como AMD nunca fue invitada a contribuir con la arquitectura IA-64 y cualquier tipo de licencia parecía poco probable, la extensión de la arquitectura AMD64 de AMD se posicionó desde el principio como una forma evolutiva de agregar capacidades informáticas de 64 bits a la arquitectura x86 existente. , sin dejar de admitir el código x86 heredado de 32 bits , a diferencia del enfoque de Intel de crear una arquitectura de 64 bits completamente nueva y completamente incompatible con x86 con IA-64.

En enero de 2019, Intel anunció que Kittson se descontinuaría, con una fecha de último pedido en enero de 2020 y una última fecha de envío en julio de 2021. [17] [18] En noviembre de 2023, se eliminó la compatibilidad con IA-64 del kernel de Linux. . [19]

Intel ha documentado ampliamente el conjunto de instrucciones Itanium [20] y la prensa técnica ha proporcionado descripciones generales. [4] [7]

La arquitectura ha cambiado de nombre varias veces a lo largo de su historia. HP originalmente lo llamó PA-WideWord . Más tarde, Intel lo llamó IA-64 , luego Arquitectura de procesador Itanium (IPA), [21] antes de decidirse por la Arquitectura Intel Itanium , pero todavía se la conoce ampliamente como IA-64 .

Es una arquitectura explícitamente paralela rica en registros de 64 bits. La palabra de datos base es de 64 bits, direccionable por bytes. El espacio de direcciones lógicas es de 264 bytes. La arquitectura implementa predicción , especulación y predicción de rama . Utiliza ventanas de registro de tamaño variable para pasar parámetros. El mismo mecanismo también se utiliza para permitir la ejecución paralela de bucles. La especulación, la predicción, la predicación y el cambio de nombre están bajo el control del compilador: cada palabra de instrucción incluye bits adicionales para esto. Este enfoque es la característica distintiva de la arquitectura.

La arquitectura implementa una gran cantidad de registros: [22] [23] [24]

gr0fr0fr1pr0br0br.callbspapunta a la segunda pila, que es donde el hardware derramará automáticamente los registros cuando la ventana del registro se cierre.Cada palabra de instrucción de 128 bits se denomina paquete y contiene tres ranuras , cada una con una instrucción de 41 bits , además de una plantilla de 5 bits que indica qué tipo de instrucción hay en cada ranura. Esos tipos son unidad M (instrucciones de memoria), unidad I (ALU entera, entera no ALU o instrucciones extendidas inmediatas largas), unidad F (instrucciones de punto flotante) o unidad B (rama o rama larga extendida). instrucciones). La plantilla también codifica paradas que indican que existe una dependencia de datos entre los datos antes y después de la parada. Todas las instrucciones entre un par de paradas constituyen un grupo de instrucciones , independientemente de su agrupación, y deben estar libres de muchos tipos de dependencias de datos; este conocimiento permite al procesador ejecutar instrucciones en paralelo sin tener que realizar su propio análisis de datos complicado, ya que ese análisis ya se realizó cuando se escribieron las instrucciones.

Dentro de cada ranura, todas las instrucciones excepto unas pocas se predican, especificando un registro de predicado, cuyo valor (verdadero o falso) determinará si se ejecuta la instrucción. Las instrucciones predicadas que siempre deben ejecutarse se basan en , que siempre se lee como verdadero.pr0

El lenguaje ensamblador y el formato de instrucción IA-64 fueron diseñados deliberadamente para ser escritos principalmente por compiladores, no por humanos. Las instrucciones deben agruparse en paquetes de tres, asegurándose de que las tres instrucciones coincidan con una plantilla permitida. Las instrucciones deben emitir paradas entre ciertos tipos de dependencias de datos, y las paradas solo se pueden utilizar en lugares limitados según las plantillas permitidas.

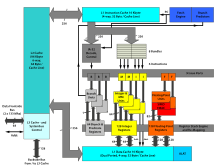

El mecanismo de recuperación puede leer hasta dos paquetes por reloj desde la caché L1 en la canalización. Cuando el compilador puede aprovechar esto al máximo, el procesador puede ejecutar seis instrucciones por ciclo de reloj. El procesador tiene treinta unidades de ejecución funcionales en once grupos. Cada unidad puede ejecutar un subconjunto particular del conjunto de instrucciones , y cada unidad se ejecuta a una velocidad de una instrucción por ciclo a menos que la ejecución se detenga esperando datos. Si bien no todas las unidades de un grupo ejecutan subconjuntos idénticos del conjunto de instrucciones, se pueden ejecutar instrucciones comunes en varias unidades.

Los grupos de unidades de ejecución incluyen:

Idealmente, el compilador puede agrupar instrucciones en conjuntos de seis que puedan ejecutarse al mismo tiempo. Dado que las unidades de punto flotante implementan una operación de multiplicación y acumulación , una única instrucción de punto flotante puede realizar el trabajo de dos instrucciones cuando la aplicación requiere una multiplicación seguida de una suma: esto es muy común en el procesamiento científico. Cuando esto ocurre, el procesador puede ejecutar cuatro FLOP por ciclo. Por ejemplo, el Itanium de 800 MHz tenía una clasificación teórica de 3,2 GFLOPS y el Itanium 2 más rápido, a 1,67 GHz, tenía una clasificación de 6,67 GFLOPS.

En la práctica, es posible que el procesador esté infrautilizado y que no todas las ranuras estén llenas de instrucciones útiles debido, por ejemplo, a dependencias de datos o limitaciones en las plantillas de paquetes disponibles. El código más denso posible requiere 42,6 bits por instrucción, en comparación con los 32 bits por instrucción de los procesadores RISC tradicionales de la época, y las no operaciones debido a las ranuras desperdiciadas disminuyen aún más la densidad del código. No es práctico generar de manera óptima instrucciones adicionales para cargas especulativas y sugerencias para ramas y caché, porque un compilador no puede predecir el contenido de los diferentes niveles de caché en un sistema que ejecuta múltiples procesos y recibe interrupciones.

De 2002 a 2006, los procesadores Itanium 2 compartieron una jerarquía de caché común. Tenían 16 KB de caché de instrucciones de nivel 1 y 16 KB de caché de datos de nivel 1. La caché L2 se unificó (tanto de instrucciones como de datos) y es de 256 KB. La caché de nivel 3 también se unificó y varió en tamaño de 1,5 MB a 24 MB. La caché L2 de 256 KB contiene suficiente lógica para manejar operaciones de semáforo sin alterar la unidad lógica aritmética (ALU) principal.

Se accede a la memoria principal a través de un bus a un conjunto de chips fuera del chip . El autobús Itanium 2 se llamaba inicialmente autobús McKinley, pero ahora se suele denominar autobús Itanium. La velocidad del bus ha aumentado constantemente con los lanzamientos de nuevos procesadores. El bus transfiere 2×128 bits por ciclo de reloj, por lo que el bus McKinley de 200 MHz transfirió 6,4 GB/s y el bus Montecito de 533 MHz transfiere 17,056 GB/s [26]

Los procesadores Itanium lanzados antes de 2006 tenían soporte de hardware para la arquitectura IA-32 para permitir la compatibilidad con aplicaciones de servidor heredadas, pero el rendimiento del código IA-32 era mucho peor que el del código nativo y también peor que el rendimiento de los procesadores x86 contemporáneos. En 2005, Intel desarrolló IA-32 Execution Layer (IA-32 EL), un emulador de software que proporciona un mejor rendimiento. Por lo tanto, con Montecito, Intel eliminó el soporte de hardware para el código IA-32.

En 2006, con el lanzamiento de Montecito , Intel realizó una serie de mejoras en la arquitectura básica del procesador, entre ellas: [27]