El sonido de circuito integrado ( I²S , pronunciado "eye-squared-ess" [ cita requerida ] ) es un protocolo de interfaz en serie para transmitir audio digital de dos canales como modulación de código de pulso (PCM) entre componentes de circuito integrado (CI) de un dispositivo electrónico. Un bus I²S separa las señales de reloj y de datos en serie, lo que da como resultado receptores más simples que los requeridos para sistemas de comunicaciones asincrónicas que necesitan recuperar el reloj del flujo de datos. Alternativamente, I²S se escribe I2S (pronunciado eye-two-ess) o IIS (pronunciado eye-eye-ess). A pesar de un nombre similar, I²S no está relacionado con I²C .

El estándar de protocolo fue introducido en 1986 por Philips Semiconductor (ahora NXP Semiconductors ) y fue revisado por primera vez el 5 de junio de 1996. [1] El estándar fue revisado por última vez el 17 de febrero de 2022 y actualizó los términos maestro y esclavo a controlador y objetivo . [2]

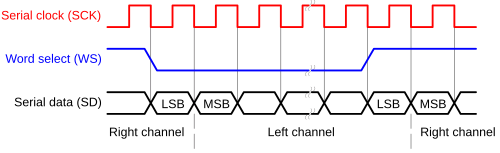

Como se muestra en el diagrama, el protocolo requiere las siguientes líneas:

El protocolo también podrá incluir las siguientes líneas:

El reloj de bits pulsa una vez por cada bit discreto de datos en las líneas de datos. La frecuencia del reloj de bits es el producto de la frecuencia de muestreo , el número de bits por canal y el número de canales. Por ejemplo, un CD de audio con una frecuencia de muestreo de 44,1 kHz, con 16 bits de precisión y dos canales (estéreo) tiene una frecuencia de reloj de bits de:

El reloj de selección de palabras permite que el dispositivo sepa si se está enviando actualmente el canal 1 (WS = 0) o el canal 2 (WS = 1), porque I²S permite que se envíen dos canales en la misma línea de datos. Es una señal con un ciclo de trabajo del 50 % que tiene la misma frecuencia que la frecuencia de muestreo. Para el material estéreo, la especificación I²S establece que el audio izquierdo se transmite en el ciclo bajo del reloj de selección de palabras y el canal derecho se transmite en el ciclo alto. Normalmente, se sincroniza con el flanco descendente del reloj en serie, ya que los datos se bloquean en el flanco ascendente. [1] El reloj de selección de palabras cambia un período de reloj de bit antes de que se transmita el MSB. Esto permite, por ejemplo, que el receptor almacene la palabra anterior y borre la entrada para la siguiente. [1]

Los datos están firmados y codificados como complemento a dos con el MSB ( bit más significativo ) primero . [1] Esto permite que la cantidad de bits por trama sea arbitraria, sin necesidad de negociación entre el transmisor y el receptor. [1]

En los equipos de audio, I²S se utiliza a veces como enlace externo entre un reproductor de CD o un dispositivo de transmisión de audio digital y un convertidor digital a analógico externo , en lugar de una conexión puramente interna dentro de un reproductor. Esto puede constituir una alternativa a los estándares AES/EBU , Toslink o S/PDIF de uso común .

La conexión I²S no fue pensada para utilizarse a través de cables, y la mayoría de los circuitos integrados no tienen la impedancia correcta para cables coaxiales. Como el error de adaptación de impedancia asociado con las diferentes longitudes de línea puede causar diferencias en el retardo de propagación entre la línea de reloj y la línea de datos, esto puede generar problemas de sincronización entre las señales SCK, WS y de datos, principalmente a frecuencias de muestreo y tasas de bits altas. Como el bus I²S no tiene ningún mecanismo de detección de errores, esto puede causar errores de decodificación significativos.

No existe un cable de interconexión estándar para esta aplicación. Algunos fabricantes simplemente proporcionan tres conectores BNC , un conector 8P8C ("RJ45") o un conector DE-9 . Otros, como Audio Alchemy (ahora desaparecida), usaban conectores DIN . PS Audio , Musica Pristina y Wyred4Sound usan un conector HDMI. [7] El fabricante holandés Van Medevoort ha implementado Q-link en algunos de sus equipos, que transfiere I²S a través de 4 conectores RCA (datos, MCK, LRCK, BCK).

Fuente de reloj para los moduladores delta-sigma y los filtros digitales. ... Es el reloj que utiliza el códec de audio ... para cronometrar y/o controlar su propio funcionamiento interno.

Es cierto que el reloj maestro (modulador) no forma parte del estándar I2S

Los conversores de audio basados en la arquitectura delta-sigma (ΔΣ) requieren un reloj maestro interno que funcione a una velocidad mucho más rápida que la frecuencia de muestreo objetivo.