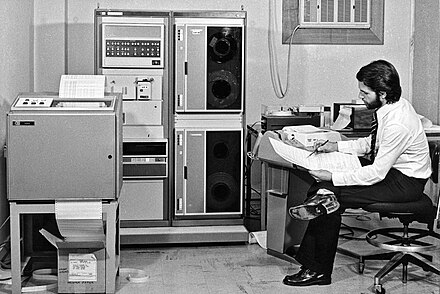

.jpg/440px-HP_2100A_Computer,_1973_(40951948745).jpg)

La HP 2100 es una serie de minicomputadoras de 16 bits que Hewlett-Packard (HP) produjo desde mediados de la década de 1960 hasta principios de la década de 1990. Se vendieron decenas de miles de máquinas de la serie durante sus veinticinco años de vida útil, lo que convirtió a HP en el cuarto mayor vendedor de minicomputadoras durante la década de 1970.

El diseño se inició en Data Systems Inc (DSI) y originalmente se conocía como DSI-1000. HP compró la empresa en 1964 y la fusionó con su división Dymec. El modelo original, el 2116A, construido con circuitos integrados y memoria de núcleo magnético , se lanzó en 1966. Durante los siguientes cuatro años, se lanzaron los modelos A a C con diferentes tipos de memoria y expansión, así como los modelos 2115 y 2114 de menor costo. Todos estos modelos fueron reemplazados por la serie HP 2100 en 1971, [1] y luego nuevamente como la serie 21MX en 1974, cuando la memoria de núcleo magnético fue reemplazada por memoria de semiconductores. [2]

Todos estos modelos también se comercializaron como la serie HP 2000 , que combinaba una máquina de la serie 2100 con componentes opcionales para ejecutar el lenguaje de programación BASIC en modo de tiempo compartido para múltiples usuarios . El BASIC de tiempo compartido de HP fue popular en la década de 1970 y muchos de los primeros programas BASIC se escribieron en o para la plataforma, en particular el influyente Star Trek que fue popular durante la era de los primeros ordenadores domésticos . La People's Computer Company publicó sus programas en formato HP 2000.

La introducción de la HP 3000 en 1974 proporcionó una competencia de alta gama a la serie 2100; toda la línea fue renombrada como HP 1000 en 1977 y posicionada como computadoras en tiempo real . Una versión muy rediseñada fue presentada en 1979 como la Serie 1000 L , utilizando chips de integración CMOS a gran escala e introduciendo un modelo de caja de torre para escritorio . Esta fue la primera versión en romper la compatibilidad con las tarjetas de expansión de la serie 2100 anteriores. La actualización final fue la serie A , con nuevos procesadores capaces de un rendimiento de más de 1 MIPS , [3] con el A990 final lanzado en 1990. [4]

HP creó Dynac en 1956 para que actuara como un taller de desarrollo para proyectos que la empresa principal normalmente no emprendería. Su logotipo original era simplemente el logotipo de HP al revés, formando algo parecido a "dy" y, por lo tanto, inspirando el nombre. Al enterarse de que Westinghouse poseía una marca registrada con ese nombre, en 1958 lo cambiaron a Dymec. La empresa se incorporó a la empresa en 1959 para convertirse en la División Dymec y, en noviembre de 1967, pasó a llamarse División Palo Alto. [5]

Dymec fabricó originalmente una variedad de productos para la familia HP, pero con el tiempo se convirtió principalmente en un integrador, construyendo equipos de prueba y sistemas similares que fueron utilizados por HP. En 1964, Kay Magleby y Paul Stoft comenzaron a experimentar con el uso de computadoras PDP-5 y PDP-8 para que actuaran como controladores para sus complejos sistemas de prueba, pero sintieron que las máquinas requerirían cambios para adaptarse realmente a sus necesidades. En ese momento, Digital Equipment Corporation (DEC) todavía era una empresa pequeña y un objetivo de adquisición. David Packard encontró que Ken Olsen era demasiado difícil de tratar, y esos planes no llegaron a ninguna parte. [5]

En busca de otro diseño que pudieran comprar, Packard fue conducido a la empresa Data Systems, Inc. (DSI) de Detroit, formada por cinco personas. DSI era propiedad de Union Carbide y, cuando Packard preguntó cómo era posible que Union Carbide llegara a ser dueña de una empresa de ordenadores, el director de HP Labs, Barney Oliver, respondió: "No pedimos una respuesta a esa pregunta". Bill Hewlett se negó inicialmente a considerar el desarrollo de un "miniordenador", pero cuando Packard lo reformuló como un "controlador de instrumentos", el acuerdo fue aprobado. [5]

DSI fue adquirida en 1964 e inicialmente se estableció en Dymec con cuatro de los cinco empleados originales de DSI y varios otros empleados provenientes de las divisiones de instrumentación de HP. [5] [6] El grupo informático luego se mudó a sus propias oficinas en Cupertino, California , en un edificio comprado a Varian Associates , convirtiéndose en la División Cupertino. [5]

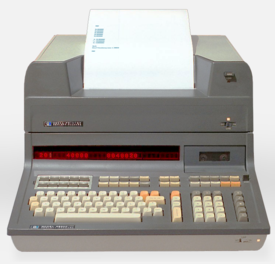

.jpg/440px-Hewlett_Packard_2115A_Computer_(1968).jpg)

Liderada por Magleby, la nueva división completó el diseño como 2116A, que se presentó del 7 al 10 de noviembre de 1966 en la Joint Computer Conference en San Francisco. [7] [8] Fue una de las primeras minicomputadoras de 16 bits que llegaron al mercado, pero en ese momento era más conocida como "una nueva computadora de instrumentación inusual" con un diseño altamente expandible y soporte en tiempo real . El sistema presentaba un gabinete de gran tamaño que albergaba hasta 16 tarjetas de expansión, o podía expandirse aún más a 48 tarjetas con una caja de expansión externa.

El sistema se puso en marcha con 20 tarjetas de instrumentación diferentes, entre las que se incluían "contadores, escaladores nucleares, termómetros electrónicos , voltímetros digitales , convertidores de CA/ohmios, amplificadores de datos y escáneres de entrada". Un conjunto adicional añadió dispositivos de entrada/salida como unidades de cinta , impresoras, tarjetas perforadas y cinta de papel , y otros periféricos. [9] Se proporcionaba un servicio en tiempo real asignando a cada ranura de tarjeta un vector de interrupción fijo que llamaba al controlador de dispositivo apropiado . [5]

Cuando la máquina entró en el mercado, rápidamente se hizo evidente que se estaba vendiendo mucho más rápidamente en el mercado de procesamiento de datos comerciales que en el mercado de instrumentación al que se dirigía originalmente. Esto llevó a la introducción del 2115A en 1967, que eliminó gran parte de las capacidades de expansión para hacer una oferta de menor costo para los usuarios comerciales. Una versión más simplificada se envió como el 2114A en 1968, [5] que tenía solo ocho ranuras, dejando espacio para que la fuente de alimentación se incorporara en el chasis principal. [10] El 2115 y el 2114 también carecían del amplio control DMA del 2116, eliminaron algunas de las operaciones matemáticas y funcionaban a velocidades ligeramente más lentas.

Estos son los modelos originales que utilizan memoria central y una CPU cableada:

En noviembre de 1968 [13] la compañía lanzó el sistema de tiempo compartido 2000A, [13] más tarde conocido como HP 2000/Access. Este se basaba en el 2116B (un 2116A con una memoria de núcleo expandida de 8k) que ejecutaba HP Time-Shared BASIC y utilizaba un 2114 separado como servidor de terminal . TS BASIC permitía crear múltiples cuentas de usuario [14] con hasta 16 usuarios conectados a la vez.

Los modelos posteriores del 2000, del B al F, utilizaban versiones más nuevas de la CPU subyacente a medida que se introducían. Algunos modelos utilizaban versiones de gama baja de la misma CPU como servidor de terminales; el 2000F, por ejemplo, utilizaba un 2100S como CPU principal y controlador de almacenamiento primario, mientras que un 2100A actuaba como servidor de terminales. [15] Los modelos B, C y F eran de doble procesador. En la última versión, el 2000F, se utilizaban una CPU 2100S y una 2100A, con la 2100A conectada a hasta 32 terminales seriales a través de interfaces de multiplexor serial. [15]

A pesar de sus costos relativamente altos (el 2000F costaba 105.000 dólares en 1974, [15] o alrededor de 649.000 dólares en 2023), fue la primera minicomputadora en ofrecer BASIC de tiempo compartido , [16] lo que la hizo muy popular a principios y mediados de los años 1970.

A lo largo de la década de 1970, la gama se mejoró constantemente con nuevos modelos que seguían siendo compatibles en software y expansión con el 2116 original.

A principios de 1970, se le pidió a Fred Allard, exmiembro de la división de núcleos de memoria de Ampex , que diseñara un nuevo sistema de memoria de núcleo magnético para los sistemas en lugar de seguir comprándolos a Ampex. Utilizando núcleos más nuevos de 18 millones , en lugar de 22 millones, y utilizando una sola línea de detección/inhibición , instalaron una memoria de 8 kW en una sola tarjeta de expansión. Esto se utilizó a partir de los modelos 2116C. [18]

En 1971, el 2100A actualizado reemplazó toda la línea 211x existente. El sistema general era similar a los modelos anteriores y seguía basándose en la memoria central. Físicamente, se parecía más al 2114, ya que la fuente de alimentación estaba incorporada y tenía una expansión interna limitada. Sin embargo, la CPU se reconstruyó con microcódigo que podía programarse por el usuario, se agregó multiplicación y división de hardware y se agregó un sistema de protección de memoria simple , que causaba una interrupción de alta prioridad cuando se activaba. Un controlador DMA de dos canales proporcionó un mayor rendimiento. También estaba disponible una unidad de punto flotante opcional . Los botones del panel frontal estaban iluminados por pequeñas lámparas incandescentes que se quemaban con el uso. El uso de una fuente de alimentación de modo conmutado [a] permitió que el chasis fuera significativamente más pequeño que los modelos anteriores.

En 1972, HP había vendido 4.500 minis, lo que la convirtió en una de las empresas más grandes del mercado. Ese año, fusionaron la División Mountain View, que fabricaba unidades de cinta magnética, con la División Cupertino para crear la División de Sistemas de Datos (DSD). En ese momento, el proyecto HP 3000 estaba en serios problemas y, en febrero de 1973, Packard envió a Paul Ely para que se hiciera cargo de la división. Las ventas de la serie 2100 se mantuvieron fuertes; la 6000.ª se envió en agosto de 1973, la 8000.ª en febrero de 1974 y la 10.000.ª en febrero de 1975. [20] Se declararon obsoletas en 1978. [1]

En 1972, la división decidió pasar a chips de memoria SRAM de 4 kbit en lugar del núcleo. Estos eran aproximadamente el doble de rápidos que los núcleos de bajo costo contemporáneos y mucho más pequeños, lo que permitía construir máquinas de 32 kbit en un factor de forma similar al 2114. En el momento en que tomaron esta decisión, las SRAM de 4 kbit no estaban realmente disponibles, por lo que inicialmente se utilizaron máquinas experimentales que usaban el núcleo de una serie 2100, reemplazado por SRAM de 1 kbit. Al principio parecía que las piezas de 4k no estarían disponibles para cuando se hubiera actualizado el resto de la máquina, por lo que la empresa sondeó a varios fabricantes y descubrió que algunos estaban desarrollando agresivamente piezas de 4k. En particular, Intel , Mostek , Motorola y Texas Instruments sugirieron que dichas piezas estarían disponibles en cantidad a fines de 1974. [21]

El uso de este tipo de memorias en un chasis de expansión, como en los sistemas anteriores, significaba que había espacio para mucha más memoria, en el rango de las megapalabras. Sin embargo, el uso de direcciones de 15 bits por parte de la CPU limitaba el tamaño a 32 000 palabras. [22] Para satisfacer el deseo de contar con sistemas más grandes, HP desarrolló el "Sistema de mapeo dinámico" o DMS, por sus siglas en inglés. El DMS amplió el formato de dirección de 15 a 20 bits, lo que permitió un máximo de 1 048 576 palabras, una expansión drástica del sistema original. [23]

Estos cambios llevaron a la introducción en 1974 de la primera de las máquinas de la serie 21MX. Esto significaba el procesador "21-M" y la memoria "21-X", ya que los sistemas de control de memoria estaban separados de la CPU para proporcionar flexibilidad en caso de que las piezas 4k elegidas se cambiaran durante la producción. Esto resultó útil en la práctica, ya que las máquinas se enviaban con memorias que utilizaban piezas Motorola o Texas Instruments, y podían mezclarse en una sola máquina, mientras que el sistema de mayor densidad basado en piezas Mostek de 16 pines podía ser compatible reemplazando el controlador 21-X/2 normal por el 21-X/1. [21]

La serie 2100 completa fue reemplazada en 1974 por la primera de estas máquinas de la serie 21MX. Al utilizar las piezas de mayor densidad, las nuevas máquinas podían admitir hasta 1,2 MB en los modelos más grandes. Cuando la CPU se actualizó aún más en 1976, los nuevos modelos se convirtieron en la "Serie 21MX E" y los modelos originales se convirtieron retroactivamente en la "Serie 21MX M". La principal diferencia entre la M y la E era que la E utilizaba una sincronización inteligente para mejorar la velocidad a aproximadamente el doble de la M. [24] Se lanzó una variedad más amplia de estilos de máquinas como parte de la serie 21MX, incluidos sistemas más pequeños con cuatro ranuras y otros más grandes con 9 o 14 ranuras. [25]

La serie 21MX contaba con una unidad de gestión de memoria y una memoria de semiconductores ampliable a 1.048.576 palabras (una megapalabra ). Las pantallas de bits de los botones del panel frontal utilizaban pequeños diodos emisores de luz (LED) rojos, en lugar de las bombillas incandescentes propensas a fundirse que se utilizaban en las versiones anteriores.

El 21MX ejecutaba el sistema operativo (OS) HP RTE (tiempo real). Comenzaron como sistemas de montaje en rack de 19 pulgadas del tamaño de un refrigerador con luces e interruptores en los paneles frontales. Los últimos modelos usaban un procesador de 1 chip y cabían debajo de un escritorio utilizando una terminal de consola en lugar de un panel frontal.

Los nuevos modelos de las series L y A tenían la capacidad de interfaz HP-IB , pero como con todos los sistemas HP en ese momento, las luces LED parpadeantes se eliminaron del panel frontal. A pesar de las demandas de los clientes de una capacidad en tiempo real y los esfuerzos de I+D de HP por utilizar una tarjeta instalable en tiempo real, el sistema operativo RTE-A no era tan bueno en operaciones en tiempo real como RTE en un 21MX. Esta fue una razón importante por la que esta computadora era difícil de eliminar. Muchas empresas utilizan operaciones en tiempo real para tomar medidas y controlar procesos: encender o apagar una bomba, un calentador, una válvula, acelerar o desacelerar un motor, etc.

A finales de 1977, toda la línea fue renombrada como "HP 1000", convirtiéndose en "HP 1000 M-Series" y "HP 1000 E-Series". Al año siguiente se introdujo la "HP 1000 F-Series", que era una serie E con una unidad de punto flotante añadida. [26] En 1978, el éxito de la línea había impulsado a HP a convertirse en el cuarto fabricante más grande en el espacio de las minicomputadoras, solo detrás de DEC, IBM y Data General . [5]

En 1980 se presentó la "Serie L HP 1000", que utilizaba un nuevo procesador basado en el proceso de integración a gran escala de silicio sobre zafiro de HP. Además, las tarjetas de expansión también estaban equipadas con sus propios procesadores que les permitían acceder a la memoria principal y realizar entradas y salidas sin afectar a la CPU. Aunque esto hizo que las tarjetas de expansión fueran incompatibles con los modelos anteriores por primera vez, también mejoró enormemente el rendimiento general. Estos modelos carecían de la unidad de gestión de memoria. [27]

La Serie L fue, a su vez, reemplazada en 1982 por la "Serie A HP 1000", que incluía un nuevo diseño de CPU "Lightning" que alcanzaba 1 MIPS y la CPU "Magic" aún más rápida de 3 MIPS. Se produjo una amplia variedad de modelos diferentes, incluidas torres de escritorio y una variedad de sistemas de montaje en bastidor de diferentes tamaños. [27] Se introdujo un modelo A400 de gama baja en 1986, [28] y el último modelo de gama alta A990 se lanzó en 1990. [29] Cada uno puede direccionar hasta 32 MB de RAM.

La serie HP 2000 se introdujo en 1969, se vendió hasta junio de 1978 y recibió soporte hasta 1985. [32]

Se escribieron versiones de muchos juegos BASIC fundamentales en la plataforma o se trasladaron a ella. Entre ellos, cabe destacar Star Trek de Mike Mayfield de 1971. [33] [34] [b] Su popularidad hizo que su dialecto de BASIC se convirtiera en una lengua franca y muchos listados de BASIC se proporcionaban normalmente en ese formato; la People's Computer Company publicó sus programas en formato HP 2000. [35] [36] Los sistemas HP también se utilizaron para enseñar estadística, análisis de regresión , [37] y economía. [c]

Se han reutilizado las designaciones 2000 y 2100:

La HP 2100 fue diseñada en una época en la que la memoria RAM en forma de memoria de núcleo magnético estaba pasando de costar unos dólares a unos céntimos por bit, [40] mientras que la implementación de registros de procesador mediante transistores o integración a pequeña escala seguía siendo muy cara. Esto favorecía los diseños con pocos registros y la mayor parte del almacenamiento en RAM, lo que a su vez influyó en la arquitectura del conjunto de instrucciones (ISA) para utilizar un diseño de memoria-memoria o de memoria - acumulador . Este concepto básico se introdujo ampliamente por primera vez en el seminal PDP-8 de 12 bits, que generó muchos diseños similares como el 2100.

En el 2100, las direcciones tienen una longitud de 15 bits, lo que permite un total de 32k palabras de memoria de 16 bits (64 KB en términos modernos). [41] La unidad de memoria direccionable más pequeña es una palabra de 16 bits; no tiene instrucciones que obtengan un solo byte de 8 bits. La dirección se divide en dos partes, los 5 bits más significativos se refieren a una de las 32 "páginas", mientras que los 10 bits menos significativos son el "desplazamiento" que apunta a una sola palabra dentro de la página de 1024 palabras. Con el sistema DMS de la serie 21MX, los 5 bits superiores se utilizan para seleccionar uno de los 32 registros, cada uno de los cuales contiene 12 bits. Los 10 bits menos significativos del registro se colocan entonces delante del desplazamiento original de 10 bits para producir una dirección de 20 bits. [23] Los dos bits más significativos se utilizan para implementar la protección de la memoria . [23]

La mayor parte del procesamiento se realiza en los dos registros A y B, cada uno de 16 bits de ancho. Los registros también son accesibles en las posiciones de memoria 0 y 1, respectivamente. Esto significa que se puede cargar un valor en un acumulador utilizando la operación normal de guardar registros, por ejemplo, LDA 1se cargará el valor del registro A en la posición de memoria 1, copiando así el valor de A en B. [42]

Además de los registros A y B, la CPU también incluye el registro M que contiene la dirección de memoria actual, y el registro T que contiene el valor en esa dirección. [43] El registro P se utiliza como contador de programa y se incrementa automáticamente con cada instrucción, pero también se utiliza como dirección base para algunos accesos a la memoria (ver más abajo) que se calculan y se colocan en M. También hay dos registros de un bit, Overflow y Extend, [41] en términos modernos, estos bits se considerarían el registro de estado . Además, está el registro S/D (Switch/Display) de 16 bits, que se utiliza para la entrada y salida desde el panel frontal. [44] [45]

Ciertas áreas de memoria están reservadas para propósitos especiales, como las posiciones 0 y 1 utilizadas por los acumuladores. Las palabras adicionales en las 64 posiciones más bajas de la memoria se utilizan para el acceso directo a memoria (DMA) y las interrupciones vectorizadas (ver más abajo). En modelos posteriores, las 64 palabras más altas de memoria disponible están reservadas para el cargador de arranque . [46]

El conjunto de instrucciones original contenía 68 [5] o 70 instrucciones. [48]

Las 68 instrucciones del conjunto de instrucciones estándar tienen una longitud de 16 bits. La mayoría se ejecutan en un ciclo de memoria, o 16 ciclos de reloj, [49] aunque el direccionamiento indirecto y el ISZpueden utilizar hasta 36 ciclos. [44] La ramificación condicional se realiza con una instrucción condicional de salto de una sola instrucción, siendo esa instrucción normalmente una instrucción de salto . No hay pila para subrutinas; en su lugar, se reserva la primera ubicación de memoria de la rutina y la instrucción escribe la dirección de retorno en esa ubicación JSB. [50] Esto significa que no hay soporte interno para código reentrante ; el soporte para esto debe agregarse mediante una pila implementada por el usuario.

Existen tres estilos básicos de instrucciones en la ISA: referencias de memoria, referencias de registro y entrada/salida. Algunos modelos ampliaron la ISA con hardware adicional, agregando, por ejemplo, instrucciones de punto flotante o instrucciones matemáticas y de memoria de números enteros adicionales, pero estas entrarían en las mismas tres categorías básicas. [42]

Las instrucciones de memoria utilizan cuatro bits para la instrucción y dos más para indicadores especiales, para un total de seis bits de la palabra de 16 bits. Esto deja espacio para una dirección de 10 bits en la instrucción, almacenada en los bits menos significativos (LSB), del 0 al 9. Si se establece el bit 15, esto indica direccionamiento "indirecto" en lugar de "directo". En el modo directo, la dirección en la instrucción es la dirección del operando, mientras que en el modo indirecto, la dirección era un puntero a otra ubicación de memoria que contenía la dirección del operando. También se podía establecer el bit 15 en esa ubicación, lo que permitía que la indirección tuviera la profundidad requerida y finalizara cuando una de las ubicaciones tuviera un 0 en el bit 15. [41] [51]

Además del modo directo/indirecto, el bit 10 de la instrucción controla el indicador Z/C. Cuando se establece en 0, esto significa que los cinco bits superiores de la dirección eran cero, mientras que los 10 inferiores eran el valor de la instrucción. Esto permite un acceso rápido a la página Z(ero), las primeras 1024 palabras de memoria. Cuando se establece en 1, la dirección se construye combinando los 10 bits de la instrucción con los 5 bits superiores del registro P, la página C(urrent) de la memoria, lo que permite acceder a la memoria como 32 páginas de 1024 palabras. [52] Por lo tanto, se pueden direccionar 2048 palabras en un momento dado; 1024 de ellas dentro de la página cero y otras 1024 dentro de la misma página que la instrucción que realiza la referencia. [51]

Las instrucciones de registro no requieren una dirección y, por lo tanto, tienen más bits libres con los que trabajar. Esto se utiliza para agrupar cuatro u ocho instrucciones en una sola palabra de memoria [53] , lo que, si se utiliza correctamente, puede acelerar significativamente las operaciones. Se incluyen un total de 39 operaciones de registro, que se dividen en instrucciones de desplazamiento y rotación y las instrucciones de modificación y salto, indicadas por el bit 10 [54] , mientras que el bit 11 indica si se está aplicando al registro A o B [55].

Existen dos clases generales de instrucciones de registro: el grupo de desplazamiento y rotación y el grupo de modificación y salto. El primero se utiliza para la manipulación básica de los valores de un registro a nivel de bit y puede tener hasta cuatro instrucciones por palabra, aunque las dos instrucciones del medio son siempre una CLE,SLA/B(borrar E, saltar si A/B es cero). El segundo grupo tiene ocho instrucciones que realizan incrementos en los registros y luego una bifurcación condicional. Normalmente se utilizan para implementar bucles. [54]

Las instrucciones de entrada/salida normalmente se comunican a través de los acumuladores. El formato de la instrucción comienza con los bits "1000" en los bits más significativos, seguido de un solo bit que indica qué registro utilizar (A=0, B=1), seguido de un "1", el bit de bandera H/C, y luego tres bits para la instrucción y los seis bits restantes para el ID del dispositivo de E/S, [56] o canal, lo que permite hasta 64 dispositivos. Algunos números de dispositivo son utilizados por el propio sistema. [57]

La entrada/salida se inicia borrando el bit de bandera con STFy luego configurando el bit C con STC. El hardware detecta este patrón y comienza su operación. Cuando se completa la operación, el dispositivo configura el bit de bandera y luego el programa carga los datos resultantes de la tarjeta utilizando la LI*instrucción o los envía a la tarjeta con OT*. [56]

La transferencia de datos real normalmente se lleva a cabo utilizando el sistema de interrupción. Las posiciones de memoria 4 a 63 (decimal) contienen las direcciones de las rutinas a las que se debe saltar cuando se dispara una interrupción, lo que proporciona 60 niveles de interrupción. [58] Las posiciones 4 a 7 están conectadas directamente a fallas de energía, errores de verificación de paridad y, en modelos posteriores, errores de protección de memoria. Las posiciones 8 y superiores son vectores de interrupción accesibles para el usuario, asignados a un canal de E/S y dispuestos en orden de prioridad. [59] Por lo tanto, si el dispositivo de E/S 13 produjo una interrupción, la CPU salta a la posición en la posición de memoria 13, pero solo si no está enmascarada por una interrupción de mayor prioridad, 1 a 12. [58]

Otra característica clave de la serie 2100 es un controlador de acceso directo a memoria independiente que utiliza el robo de ciclos para acceder a la memoria cuando la CPU no la está utilizando, por ejemplo, durante los momentos en que está realizando cálculos internos. Con esta característica, se pueden completar procesos de E/S largos mientras la CPU trabaja en otros problemas. El sistema se configura enviando una instrucción al controlador DMA utilizando los comandos de E/S; el controlador DMA es el canal 6 y se le envía inicialmente una instrucción que contiene el número del dispositivo de E/S que desea utilizar DMA, ya sea una entrada (escritura en memoria desde el dispositivo) o una salida (lectura desde la memoria al dispositivo), la ubicación inicial en la memoria para los datos y el número de palabras. Este código de configuración a menudo se instala en uno de los vectores de interrupción, automatizando el proceso. [57] El DMS tiene tablas separadas para la CPU y el sistema DMA, por lo que DMA puede cargar datos en partes separadas de la memoria extendida. [23]

HP suministró un ensamblador de tres pasadas para la máquina [60] , que utiliza un formato delimitado por columnas. La primera área, a la izquierda de la línea de código, es la etiqueta, que debe comenzar en la columna 1 si está presente. A continuación viene la mnemotecnia de la instrucción y luego los parámetros. El resto de la línea se puede utilizar para un comentario. El ensamblador permite escribir expresiones matemáticas básicas directamente, en lugar de utilizar mnemotecnias, y también incluye una serie de pseudoinstrucciones como ORGla de establecer la dirección base del programa. [56]

Además del ensamblador y el enlazador asociado , las máquinas se entregaron inicialmente con un compilador FORTRAN 66 , el sistema operativo y controladores de E/S. Con el tiempo, se agregaron lenguajes adicionales, incluidos BASIC, ALGOL , FORTRAN IV [61] y FORTRAN 77. [ 62]

HP trasladó implementaciones de AGL a la plataforma, lo que añadió comandos a su BASIC para producir gráficos en sus terminales gráficos y plotters . Una expansión similar en su FORTRAN se denominó GRAPHICS/1000.

Los modelos 2100 se utilizaban normalmente con el sistema operativo "Real Time Executive", o RTE para abreviar. [63] Se lanzaron varias versiones de RTE para las diferentes versiones de la máquina: RTE-II para los modelos 2114-2116, RTE-III para los modelos 2100, RTE-IV para la serie 21MX y RTE-A para la serie "A".

El shell del sistema operativo, incluso a finales de los años 70, era muy primitivo, con un sistema de archivos de un solo nivel , el Administrador de archivos o FMGR. Por ejemplo, el comando para ejecutar un compilador FORTRAN sería el siguiente: [62]

es, f77, &prueba,'prueba,%prueba

significa ejecutar el programa f77, utilizando caracteres especiales para distinguir entre archivo fuente, objeto y archivos ejecutables.

La HP 1000 también fue una de las pocas minicomputadoras que restringió los nombres de archivo a solo cinco caracteres, en lugar de los seis habituales en ese momento, lo que hizo que la portabilidad e incluso la escritura de programas fueran un desafío. El RTE-A posterior para HP 1000 proporcionó una estructura de directorio convencional con nombres de archivo de 16,4 caracteres e hizo que el comando ru fuera opcional.

TODS (Test Oriented Disk System) fue desarrollado por un técnico del centro de reparación de placas de HP para mejorar el tiempo de respuesta en el centro. Se utilizó para cargar diagnósticos desde un repositorio central en lugar de cargar cintas de papel individuales. TODS también se utilizó en las series HP 2116 a 21MX-F para sistemas de prueba de misiles como Phoenix (9206B), Harpoon (9500D-354), Tomahawk y muchos otros. Los primeros equipos de prueba fueron el 9500A, que evolucionó al 9500D, seguido por el ATS (Automated Test System); sistemas de prueba específicos de HP, como el equipo de prueba de componentes de lanzamiento Minuteman 9500D-A46 y el equipo de prueba de componentes de lanzamiento Peacekeeper/Minuteman ATS-E35; el ANA/ASA (Analizador automático de red/Analizador automático de espectro) de microondas HP 8580/8542 que se ejecutaba en TODS; y el conjunto de pruebas del transpondedor de microondas TDRSS utilizó TODS y era un sistema muy grande.

También existía el MTOS (sistema operativo de cinta magnética) similar al TODS.

Las computadoras de escritorio HP 9810, 9820 y 9830 usan una versión TTL serializada y lenta de la CPU 2116, aunque en última instancia no usaron ninguno de los sistemas operativos o software de aplicación, sino que confiaron en intérpretes basados en ROM fáciles de usar , como BASIC , que funcionan cuando se encienden, y teclados y pantallas integrados en lugar de discos o terminales estándar . En 1975, HP presentó el BPC (Binary Processing Chip), uno de los primeros microprocesadores de 16 bits del mundo , que usaba el proceso NMOS -II de HP. [64] [65] El BPC generalmente se empaquetaba en un módulo híbrido de cerámica con los chips EMC e IOC, que agregaban instrucciones matemáticas y de E/S extendidas. El híbrido se desarrolló como el corazón de la nueva computadora de escritorio 9825. [66] La posterior estación de trabajo 9845 agregó un chip MMU . Estos fueron los precursores de las computadoras personales y las estaciones de trabajo técnicas.

Las principales diferencias entre la arquitectura original del 2116 y el microprocesador BPC son una estructura de E/S completamente rediseñada, la eliminación de múltiples niveles de direccionamiento indirecto y la provisión de un registro de pila para llamadas y retornos de subrutinas. La eliminación del direccionamiento indirecto múltiple hizo que un bit adicional estuviera disponible en una palabra de memoria que contenía una dirección indirecta, lo que permitió aumentar la capacidad máxima de memoria de 32 000 palabras de 16 bits a 64 000. El BPC también agregó una entrada que permite que la "página actual" sea relativa a la ubicación de la instrucción actual, en lugar de una página alineada con una potencia de dos.

El BPC se utilizó en una amplia gama de computadoras, periféricos y equipos de prueba de HP, hasta que se discontinuó a fines de la década de 1980.

Polonia fabricó un clon del HP 2114B desde 1973. Los clones polacos se denominaron MKJ-28 (prototipo, 1973), SMC-3 (producción piloto, 17 máquinas, 1975-1977) y PRS-4 (producción en serie de más de 150 máquinas, 1978-1987).

Checoslovaquia produjo sus propios clones compatibles con HP 1000, denominados ADT4000 (4300, 4500, 4700, 4900). Los proveedores Aritma Prague (desarrollo), ZPA Čakovice y ZPA Trutnov suministraron más de 1000 unidades entre 1973 y 1990. Estos ordenadores se utilizaron en centrales eléctricas, incluidas las nucleares, en otras industrias, en el ejército, en universidades, etc., por su alta fiabilidad y sus funciones de tiempo real. Los sistemas operativos eran DOS/ADT (varias versiones) y Unix. El híbrido más antiguo, el ADT7000 (1974), estaba compuesto por partes digitales del ADT4000 y analógicas del ADT3000, pero sólo la parte digital resultaba interesante para los clientes. El ADT4316 (1976) tenía 16K palabras de memoria de núcleo de ferrita, el ADT4500 (1978) hasta 4M palabras de RAM de semiconductores. El ADT 4900 fue diseñado como un ordenador de placa única , pero su producción en serie no se inició. El Ejército Popular Checoslovaco utilizó los miniordenadores móviles MOMI 1 y MOMI 2 basados en el ADT, integrados en un contenedor transportado por el camión Tatra 148.

El 2000A fue el primer sistema de tiempo compartido HP 2000 que salió al mercado en 1969 aproximadamente

La HP 2000-2b19wm... una computadora portátil de 15 pulgadas por menos de $300