En la fabricación de semiconductores , el proceso de "7 nm" es un término para el nodo de tecnología MOSFET que sigue al nodo de "10 nm" , definido por la Hoja de Ruta Internacional para Dispositivos y Sistemas (IRDS), que fue precedida por la Hoja de Ruta Internacional de Tecnología para Semiconductores (ITRS). Se basa en la tecnología FinFET (transistor de efecto de campo de aletas), un tipo de tecnología MOSFET de múltiples puertas .

A partir de 2021, el estándar de litografía IRDS proporciona una tabla de dimensiones para el nodo "7 nm", [1] con ejemplos que se indican a continuación:

El estándar de litografía IRDS 2021 es un documento retrospectivo, ya que la primera producción en volumen de un proceso de marca "7 nm" fue en 2016 con la producción de chips de memoria SRAM de 256 Mbit de Taiwan Semiconductor Manufacturing Company ( TSMC ) utilizando un proceso de "7 nm " llamado N7. [2] Samsung comenzó la producción en masa de sus dispositivos de proceso "7 nm" (7LPP) en 2018. [3] Estos nodos de proceso tenían la misma densidad de transistores aproximada que el nodo " 10 nm Enhanced Superfin " de Intel, posteriormente rebautizado como "Intel 7". [4]

Desde al menos 1997, la escala de longitud de un nodo de proceso no se ha referido a ninguna dimensión particular en los circuitos integrados, como la longitud de la compuerta, el paso del metal o el paso de la compuerta, ya que los nuevos procesos de litografía ya no reducían de manera uniforme todas las características de un chip. A fines de la década de 2010, la escala de longitud se había convertido en un nombre comercial [5] que indicaba una nueva generación de tecnologías de proceso, sin ninguna relación con las propiedades físicas. [6] [7] [8] Las normas ITRS e IRDS anteriores no tenían una guía suficiente sobre las convenciones de nomenclatura de los nodos de proceso para abordar las dimensiones ampliamente variables de un chip, lo que llevó a una divergencia entre la forma en que las fundiciones marcaban su litografía y las dimensiones reales que lograban sus nodos de proceso.

El primer procesador móvil convencional "7nm" destinado al uso en el mercado masivo, el Apple A12 Bionic , se anunció en el evento de Apple de septiembre de 2018. [ 9] Aunque Huawei anunció su propio procesador "7nm" antes del Apple A12 Bionic, el Kirin 980 el 31 de agosto de 2018, el Apple A12 Bionic se lanzó para uso público y en el mercado masivo para los consumidores antes del Kirin 980. Ambos chips fueron fabricados por TSMC. [10]

En 2019, [11] AMD lanzó sus procesadores " Rome " (EPYC 2) para servidores y centros de datos, que se basan en el nodo N7 de TSMC [12] y cuentan con hasta 64 núcleos y 128 subprocesos. También lanzaron sus procesadores de escritorio para consumidores " Matisse " con hasta 16 núcleos y 32 subprocesos. Sin embargo, la matriz de E/S en el módulo multichip (MCM) Rome está fabricada con el proceso de 14 nm (14HP) de GlobalFoundries , mientras que la matriz de E/S de Matisse utiliza el proceso "12 nm" (12LP+) de GlobalFoundries . La serie Radeon RX 5000 también se basa en el proceso N7 de TSMC.

A principios de la década de 2000, los investigadores comenzaron a demostrar MOSFET de nivel de 7 nm , con un equipo de IBM que incluía a Bruce Doris, Omer Dokumaci, Meikei Ieong y Anda Mocuta fabricando con éxito un MOSFET de silicio sobre aislante (SOI) de 6 nm. [13] [14] Poco después, en 2003, los investigadores de NEC Hitoshi Wakabayashi y Shigeharu Yamagami avanzaron aún más al fabricar un MOSFET de 5 nm. [15] [16]

En julio de 2015, IBM anunció que había construido los primeros transistores funcionales con tecnología de "7 nm", utilizando un proceso de silicio-germanio . [17] [18] [19] [20] Con un mayor desarrollo en febrero de 2017, TSMC produjo celdas de memoria SRAM de 256 Mbit con su proceso de "7 nm", con un área de celda de 0,027 micrómetros cuadrados , [21] dando un tamaño de característica mínimo cuadrado:

Acumulando el volumen inicial de producción de 7 nm de TSMC en 2018. [2]

En 2015, Intel esperaba que en el nodo de 7 nm se tuvieran que utilizar semiconductores III-V en transistores, lo que indicaba un alejamiento del silicio. [22]

En abril de 2016, TSMC anunció que la producción de prueba de "7 nm" comenzaría en la primera mitad de 2017. [23] En abril de 2017, TSMC comenzó la producción de riesgo de chips de memoria SRAM de 256 Mbit utilizando un proceso de "7 nm" (N7FF+), [2] con litografía ultravioleta extrema (EUV). [24] Los planes de producción de "7 nm" de TSMC, a principios de 2017, [ necesita actualización ] eran utilizar litografía de inmersión ultravioleta profunda (DUV) inicialmente en este nodo de proceso (N7FF), y la transición de riesgo a fabricación comercial en volumen desde el segundo trimestre de 2017 al segundo trimestre de 2018. Además, su producción de "7 nm" (N7FF+) de última generación estaba planificada [ necesita actualización ] para utilizar patrones múltiples EUV y tener una transición estimada de riesgo a fabricación en volumen entre 2018 y 2019. [25]

En septiembre de 2016, GlobalFoundries anunció una producción de prueba en la segunda mitad de 2017 y una producción de riesgo a principios de 2018, con chips de prueba ya en funcionamiento. [26]

En febrero de 2017, Intel anunció Fab 42 en Chandler, Arizona , que según los comunicados de prensa de ese momento se esperaba [ necesita actualización ] que produjera microprocesadores utilizando un proceso de fabricación de "7 nm" (Intel 4 [27] ). [28] La compañía no había publicado, en ese momento, ningún valor esperado para las longitudes de las características en este nodo de proceso. [ necesita actualización ]

En abril de 2018, TSMC anunció la producción en serie de chips de "7 nm" (CLN7FF, N7). En junio de 2018, la empresa anunció el aumento de la producción en masa. [3]

En mayo de 2018, Samsung anunció la producción de chips de "7 nm" (7LPP) este año. ASML Holding NV es su principal proveedor de máquinas de litografía EUV. [29]

En agosto de 2018, GlobalFoundries anunció que detendría el desarrollo de chips de "7 nm", citando el costo. [30]

El 28 de octubre de 2018, Samsung anunció que su proceso de "7 nm" de segunda generación (7LPP) había entrado en producción de riesgo y en ese momento se esperaba que hubiera entrado en producción en masa en 2019. [ necesita actualización ]

El 17 de enero de 2019, durante la conferencia telefónica sobre los resultados del cuarto trimestre de 2018, TSMC mencionó que los distintos clientes tendrían "diferentes sabores" de la segunda generación de "7 nm". [31] [ Necesita actualización ]

El 16 de abril de 2019, TSMC anunció su proceso "6nm" llamado (CLN6FF, N6), que, según un comunicado de prensa realizado el 16 de abril de 2019, en ese momento se esperaba que estuviera en productos masivos a partir de 2021. [32] [ necesita actualización ] En ese momento, se esperaba que N6 hubiera usado EUVL en hasta 5 capas, en comparación con hasta 4 capas en su proceso N7+. [33]

El 28 de julio de 2019, TSMC anunció su proceso de "7 nm" de segunda generación llamado N7P, que se proyectaba que se basaría en DUV como su proceso N7. [34] Dado que N7P era totalmente compatible con IP con el "7 nm" original, mientras que N7+ (que usa EUV) no lo era, N7+ (anunciado anteriormente como "7 nm+") debía haber sido un proceso separado de "7 nm". N6 ("6 nm"), otro proceso basado en EUV, estaba planeado en ese momento para haber sido lanzado más tarde incluso que el proceso "5 nm" (N5) de TSMC, con la compatibilidad de IP con N7. En su llamada de ganancias del primer trimestre de 2019, TSMC reiteró su declaración del cuarto trimestre de 2018 [31] de que en ese momento se esperaba que N7+ hubiera generado menos de mil millones de dólares taiwaneses en ingresos en 2019. [35] [ necesita actualización ]

El 5 de octubre de 2019, AMD anunció su hoja de ruta EPYC , que incluye chips Milan fabricados con el proceso N7+ de TSMC. [36] [ necesita actualización ]

El 7 de octubre de 2019, TSMC anunció que había comenzado a entregar productos N7+ al mercado en grandes volúmenes. [37] [ necesita actualización ]

El 26 de julio de 2021, Intel anunció su nueva hoja de ruta de fabricación, renombrando todos sus futuros nodos de proceso. [27] El Enhanced SuperFin (10ESF) de "10 nm" de Intel, que era aproximadamente equivalente al proceso N7 de TSMC, se conocería a partir de entonces como "Intel 7", mientras que su proceso anterior de "7 nm" se llamaría anteriormente "Intel 4". [27] [38] Como resultado, en ese momento se planeó que los primeros procesadores de Intel basados en Intel 7 comenzaran a enviarse en la segunda mitad de 2022, [ necesita actualización ] mientras que Intel anunció anteriormente que planeaba haber lanzado procesadores de "7 nm" en 2023. [39] [ necesita actualización ]

En junio de 2018, AMD anunció el lanzamiento de las GPU Radeon Instinct de 7 nm en la segunda mitad de 2018. [40] En agosto de 2018, la compañía confirmó el lanzamiento de las GPU. [41]

El 21 de agosto de 2018, Huawei anunció el uso del SoC HiSilicon Kirin 980 en los Huawei Mate 20 y Mate 20 Pro fabricados con el proceso de 7 nm (N7) de TSMC. [ necesita actualización ]

El 12 de septiembre de 2018, Apple anunció su chip A12 Bionic utilizado en el iPhone XS y el iPhone XR construidos con el proceso de 7 nm (N7) de TSMC. El procesador A12 se convirtió en el primer chip de 7 nm para uso en el mercado masivo, ya que se lanzó antes del Huawei Mate 20. [42] [43] El 30 de octubre de 2018, Apple anunció su chip A12X Bionic utilizado en el iPad Pro construido con el proceso de 7 nm (N7) de TSMC. [44]

El 4 de diciembre de 2018, Qualcomm anunció sus Snapdragon 855 y 8cx fabricados con el proceso de 7 nm (N7) de TSMC. [45] El primer producto masivo con el Snapdragon 855 fue el Lenovo Z5 Pro GT, que se anunció el 18 de diciembre de 2018. [46]

El 29 de mayo de 2019, MediaTek anunció su SoC 5G construido utilizando un proceso de 7 nm de TSMC. [47]

El 7 de julio de 2019, AMD lanzó oficialmente su serie de unidades centrales de procesamiento Ryzen 3000, basadas en el proceso de 7 nm de TSMC y la microarquitectura Zen 2 .

El 6 de agosto de 2019, Samsung anunció su SoC Exynos 9825, el primer chip construido con su proceso 7LPP. El Exynos 9825 es el primer chip para el mercado masivo construido con EUVL . [48]

El 6 de septiembre de 2019, Huawei anunció sus SoC HiSilicon Kirin 990 4G y 990 5G , construidos utilizando los procesos N7 y N7+ de TSMC. [49]

El 10 de septiembre de 2019, Apple anunció su chip A13 Bionic utilizado en el iPhone 11 y el iPhone 11 Pro fabricados con el proceso N7P de segunda generación de TSMC. [50]

La fabricación de 7 nm (nodos N7) representó el 36 % de los ingresos de TSMC en el segundo trimestre de 2020. [51]

El 17 de agosto de 2020, IBM anunció su procesador Power10 . [50]

El 26 de julio de 2021, Intel anunció que sus procesadores Alder Lake se fabricarían utilizando su nuevo proceso "Intel 7", anteriormente conocido como "10nm Enhanced SuperFin". [27] En ese momento, se esperaba, según los comunicados de prensa, que estos procesadores se lanzaran en la segunda mitad de 2021. [ necesita actualización ] La compañía confirmó anteriormente una familia de microprocesadores de 7 nm, ahora llamada "Intel 4", [27] llamada Meteor Lake que se lanzaría en 2023. [52] [53] [ necesita actualización ]

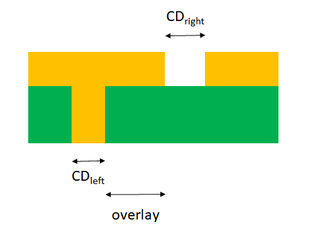

Se espera que el nodo de fundición "7nm" utilice cualquiera de las siguientes tecnologías de modelado o una combinación de ellas: división de paso , modelado autoalineado y litografía EUV . Cada una de estas tecnologías conlleva desafíos significativos en el control de la dimensión crítica (CD) así como en la colocación de patrones, todo lo cual involucra características vecinas.

La división de tonos implica dividir los elementos que están demasiado próximos entre sí en diferentes máscaras, que se exponen sucesivamente y luego se procesan mediante litograbado. Debido al uso de diferentes exposiciones, siempre existe el riesgo de que se produzca un error de superposición entre las dos exposiciones, así como diferentes CD resultantes de las diferentes exposiciones.

El patrón de espaciadores implica depositar una capa sobre características pre-estampadas, luego grabar de nuevo para formar espaciadores en las paredes laterales de esas características, denominadas características centrales. Después de eliminar las características centrales, los espaciadores se utilizan como una máscara de grabado para definir zanjas en la capa subyacente. Si bien el control de CD del espaciador es generalmente excelente, el CD de la zanja puede caer en una de dos poblaciones, debido a las dos posibilidades de estar ubicado donde se encontraba una característica central o en el espacio restante. Esto se conoce como "caminata de cabeceo". [54] Generalmente, cabeceo = CD del núcleo + CD del espacio + 2 * CD del espaciador, pero esto no garantiza que el CD del núcleo = CD del espacio. Para las características FEOL como el aislamiento de la compuerta o del área activa (por ejemplo, aletas), el CD de la zanja no es tan crítico como el CD definido por el espaciador, en cuyo caso, el patrón de espaciadores es en realidad el enfoque de patrón preferido.

Cuando se utiliza el patrón cuádruple autoalineado (SAQP), se utiliza un segundo espaciador que reemplaza al primero. En este caso, el CD del núcleo se reemplaza por el CD del núcleo - 2* 2.º espaciador CD, y el CD de la brecha se reemplaza por el CD de la brecha - 2 * 2.º espaciador CD. Por lo tanto, algunas dimensiones de las características están estrictamente definidas por el CD del segundo espaciador, mientras que las dimensiones restantes de las características están definidas por el CD del núcleo, el paso del núcleo y el primer y segundo CD del espaciador. El CD del núcleo y el paso del núcleo se definen mediante litografía convencional, mientras que los CD del espaciador son independientes de la litografía. En realidad, se espera que esto tenga menos variación que la división de paso, donde una exposición adicional define su propio CD, tanto directamente como a través de una superposición.

Las líneas definidas por espaciadores también requieren cortes. Los puntos de corte pueden desplazarse durante la exposición, lo que da como resultado extremos de línea distorsionados o intrusiones en líneas adyacentes.

Se ha implementado el método de litografía-grabado-litografía-grabado autoalineado (SALELE) para el modelado BEOL de "7 nm". [55]

La litografía ultravioleta extrema (también conocida como EUV o EUVL ) es capaz de resolver características por debajo de los 20 nm en el estilo de litografía convencional. Sin embargo, la naturaleza reflectante 3D de la máscara EUV da como resultado nuevas anomalías en la imagen. Una molestia particular es el efecto de dos barras, donde un par de características idénticas en forma de barra no se enfocan de manera idéntica. Una característica está esencialmente en la "sombra" de la otra. En consecuencia, las dos características generalmente tienen diferentes CD que cambian a través del enfoque, y estas características también cambian de posición a través del enfoque. [56] [57] [58] Este efecto puede ser similar a lo que puede encontrarse con la división de tono. Un problema relacionado es la diferencia de mejor enfoque entre características de diferentes tonos. [59]

La EUV también tiene problemas para imprimir de manera confiable todas las características en una población grande; algunos contactos pueden faltar por completo o las líneas pueden estar puenteadas. Estos se conocen como fallas de impresión estocásticas. [60] [61] El nivel de defectos es del orden de 1K/mm 2 . [62]

La brecha entre puntas es difícil de controlar para EUV, en gran medida debido a la restricción de iluminación. [63] Se prefiere una o más exposiciones separadas para las líneas de corte.

Se han utilizado máscaras de cambio de fase atenuadas en la producción para el nodo de 90 nm para obtener ventanas de enfoque adecuadas para contactos con una inclinación arbitraria con la longitud de onda del láser ArF (193 nm), [64] [65] mientras que esta mejora de resolución no está disponible para EUV. [66] [67]

En la conferencia de litografía EUV de SPIE de 2021, un cliente de TSMC informó que el rendimiento de contacto EUV era comparable al rendimiento de multipatterning por inmersión. [68]

Debido a estos desafíos, el proceso de "7 nm" plantea una dificultad de modelado sin precedentes en la parte final de la línea (BEOL). El nodo de fundición anterior, de gran volumen y larga duración (Samsung "10 nm", TSMC "16 nm") utilizaba la división de paso para las capas de metal de paso más estrecho. [69] [70] [71]

Debido a que las herramientas de inmersión son más rápidas en la actualidad, el patrón múltiple aún se utiliza en la mayoría de las capas. En las capas que requieren patrón cuádruple de inmersión, el rendimiento de finalización de capa por EUV es comparable. En las otras capas, la inmersión sería más productiva para completar la capa incluso con el patrón múltiple.

El patrón de metal de "7 nm" que practica actualmente TSMC implica líneas de patrón doble autoalineado (SADP) con cortes insertados dentro de una celda en una máscara separada según sea necesario para reducir la altura de la celda. [74] Sin embargo, se utiliza patrón cuádruple autoalineado (SAQP) para formar la aleta, el factor más importante para el rendimiento. [75] Las comprobaciones de las reglas de diseño también permiten evitar el patrón múltiple y proporcionan suficientes espacios libres para los cortes de modo que solo se necesita una máscara de corte. [75]

La denominación de los nodos de proceso por parte de 4 fabricantes diferentes (TSMC, Samsung, SMIC , Intel) está parcialmente impulsada por el marketing y no está relacionada directamente con ninguna distancia medible en un chip; por ejemplo, el nodo "7nm" de TSMC era anteriormente similar en algunas dimensiones clave al nodo "10nm" de primera iteración planificado por Intel, antes de que Intel lanzara iteraciones posteriores, que culminaron en "10nm Enhanced SuperFin", que luego se renombró como "Intel 7" por razones de marketing. [76] [77]

Dado que la implementación de EUV en "7 nm" aún es limitada, el patrón múltiple aún juega un papel importante en el costo y el rendimiento; EUV agrega consideraciones adicionales. La resolución para la mayoría de las capas críticas aún está determinada por el patrón múltiple. Por ejemplo, para "7 nm" de Samsung, incluso con capas de paso de 36 nm con patrón único EUV, las capas de paso de 44 nm aún tendrían patrón cuádruple. [78]

El proceso 7LP (Leading Performance) de GlobalFoundries "7nm" habría ofrecido un rendimiento un 40% superior o un consumo de energía un 60% inferior con una escala de densidad de 2x y un coste por chip entre un 30 y un 45% inferior en comparación con su proceso de "14 nm". El paso de policontacto (CPP) habría sido de 56 nm y el paso de metal mínimo (MMP) habría sido de 40 nm, producidos con patrón doble autoalineado (SADP). Una celda SRAM de 6T habría tenido un tamaño de 0,269 micrones cuadrados. GlobalFoundries planeó utilizar con el tiempo la litografía EUV en un proceso mejorado llamado 7LP+. [100] GlobalFoundries detuvo más tarde todo el desarrollo de procesos de "7 nm" y superiores. [101]

El nuevo proceso "Intel 7" de Intel, anteriormente conocido como "10nm Enhanced SuperFin" (10ESF), se basa en su nodo "10nm" anterior. El nodo contará con un aumento del 10-15% en el rendimiento por vatio . Mientras tanto, se esperaba que su antiguo proceso "7nm", ahora llamado "Intel 4", se lanzara en ese momento en 2023. [102] [ necesita actualización ] En ese momento se habían hecho públicos pocos detalles sobre el nodo "Intel 4", aunque en ese momento se había estimado que su densidad de transistores era de al menos 202 millones de transistores por milímetro cuadrado. [27] [103] [ necesita actualización ] A partir de 2020, Intel había estado experimentando problemas con su proceso "Intel 4" hasta el punto de externalizar la producción de sus GPU Ponte Vecchio. [104] [105] [ necesita actualización ]