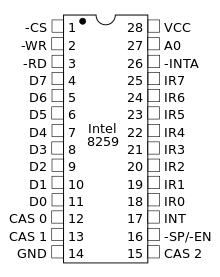

Intel 8259

Sin embargo, aunque ya no es un chip separado, la interface del 8259A todavía es proporcionada por el chipset Southbridge en las modernas tarjetas x86.

Los conectores principales en un 8259 son los siguientes: Hasta ocho 8259 esclavos pueden ser conectados en cascada a un 8259 maestro para proporcionar un máximo de 64 IRQ.

Hay tres registros internos en el 8259: El 8259 soporta los modos de prioridad fijos y rotatorios.

Un EOI específico indica el nivel de IRQ que está reconociendo en el ISR.

La estructura del controlador está formada por un conjunto de registros internos que analizaremos a continuación.

Esto es especialmente importante para hardware moderno x86 en la que una cantidad significativa de tiempo se puede gastardireccionando I / O en la comunicación con los 8259s.

Esto también permite otras optimizaciones en la sincronización, tales como las secciones críticas, en un sistema con varios procesadores x86 con 8259s.

[cita requerida] Esto puede ocurrir debido al ruido en la línea de IRQ.

En el modo accionado por flanco, el ruido debe mantener la línea en el estado bajo de 100 ns.

Un caso similar puede ocurrir cuando el 8259 desenmascarar y la deassertion entrada de IRQ no se sincronizan correctamente.

En este apartado analizamos las diferentes secuencias de inicialización que podemos introducir al 8259 para su posterior funcionamiento.

Los puertos serie son con frecuencia con discapacidad a una línea de IRQ libre para otro dispositivo.

IRQ2 / 9 es la línea tradicional de interrupción para un puerto MPU-401 MIDI, pero esto entra en conflicto con el control del sistema ACPI de interrupción (SCI se cablea directamente al IRQ9 en los chipsets Intel), lo que significa ISA MPU-401 tarjetas con un cableado IRQ 2 / 9 , y los conductores MPU-401 con un dispositivo codificado IRQ 2 / 9, no se puede utilizar en el modo controlado por interrupciones en un sistema con ACPI habilitado.