La compuerta OR es una compuerta lógica digital que implementa la disyunción lógica . La compuerta OR genera como salida "verdadero" si alguna de sus entradas es "verdadera"; de lo contrario, genera como salida "falso". Los estados de entrada y salida normalmente se representan mediante diferentes niveles de voltaje .

Cualquier compuerta OR puede construirse con dos o más entradas. Su salida es un 1 si alguna de estas entradas es 1, o un 0 solo si todas las entradas son 0. Las entradas y salidas son dígitos binarios (" bits ") que tienen dos estados lógicos posibles . Además de 1 y 0, estos estados pueden llamarse verdadero y falso, alto y bajo, activo e inactivo u otros pares de símbolos similares.

Por lo tanto, realiza una disyunción lógica (∨) a partir de la lógica matemática . La compuerta se puede representar con el signo más (+) porque se puede utilizar para la adición lógica . [1] De manera equivalente, una compuerta OR encuentra el máximo entre dos dígitos binarios, al igual que la compuerta AND encuentra el mínimo . [2]

Junto con la puerta AND y la puerta NOT , la puerta OR es una de las tres puertas lógicas básicas a partir de las cuales se puede construir cualquier circuito booleano . Todas las demás puertas lógicas se pueden hacer a partir de estas tres puertas; cualquier función en matemáticas binarias se puede implementar con ellas. [3]

A veces se la denomina compuerta OR inclusiva para distinguirla de XOR , la compuerta OR exclusiva. [4] El comportamiento de OR es el mismo que el de XOR excepto en el caso de un 1 para ambas entradas. En situaciones en las que esto nunca surge (por ejemplo, en un sumador completo ), los dos tipos de compuertas son intercambiables. Esta sustitución es conveniente cuando se implementa un circuito utilizando chips de circuitos integrados simples que contienen solo un tipo de compuerta por chip.

Actualmente, existen dos símbolos de puerta lógica que representan la puerta OR: el símbolo americano ( ANSI o "militar") y el símbolo IEC ("europeo" o "rectangular"). El símbolo DIN está en desuso. [5] [6]

El "≥1" en el símbolo IEC indica que la salida está activada por al menos una entrada activa. [7]

A partir de Unicode 16.0.0, la puerta OR también está codificada en el bloque Suplemento Símbolos para Computación Legacy como U+1CC15 PUERTA LÓGICA OR .

Las puertas OR son puertas lógicas básicas y están disponibles en las familias de circuitos integrados TTL y CMOS . El circuito integrado CMOS estándar de la serie 4000 es el 4071, que incluye cuatro puertas OR independientes de dos entradas. El dispositivo TTL es el 7432. Hay muchas derivaciones de la puerta OR 7432 original, todas con la misma distribución de pines pero diferente arquitectura interna, lo que les permite funcionar en diferentes rangos de voltaje y/o a velocidades más altas. Además de la puerta OR estándar de 2 entradas, también están disponibles puertas OR de 3 y 4 entradas. En la serie CMOS, estas son:

Las variaciones incluyen:

es la representación analítica de la puerta OR:

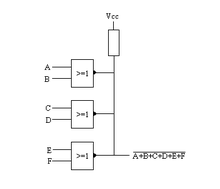

Las puertas OR con múltiples entradas se designan con el mismo símbolo, con más líneas que las preceden. [8] Si bien las implementaciones directas con más de tres entradas son posibles en familias lógicas como CMOS, estas son ineficientes. Las implementaciones más eficientes utilizan una cascada de puertas NOR y NAND , como se muestra en la siguiente imagen.

Si no hay puertas OR específicas disponibles, se puede hacer una a partir de puertas NAND o NOR en la configuración que se muestra en la imagen siguiente. Cualquier puerta lógica se puede hacer a partir de una combinación de puertas NAND o NOR .

Con salidas lógicas de colector abierto bajas y activas , como las que se utilizan para señales de control en muchos circuitos, se puede generar una función OR conectando varias salidas entre sí. Esta disposición se denomina OR cableado . Esta implementación de una función OR también se encuentra normalmente en circuitos integrados de procesos con transistores de tipo N o P únicamente.

{{cite book}}: CS1 maint: varios nombres: lista de autores ( enlace )