La función booleana NAND tiene la propiedad de completitud funcional . Esto significa que cualquier expresión booleana puede ser reexpresada por una expresión equivalente utilizando únicamente operaciones NAND . Por ejemplo, la función NOT(x) puede ser expresada de manera equivalente como NAND(x,x). En el campo de los circuitos electrónicos digitales , esto implica que es posible implementar cualquier función booleana utilizando únicamente puertas NAND .

La prueba matemática de esto fue publicada por Henry M. Sheffer en 1913 en Transactions of the American Mathematical Society (Sheffer 1913). Un caso similar se aplica a la función NOR , y se la conoce como lógica NOR .

Una compuerta NAND es una compuerta AND invertida . Tiene la siguiente tabla de verdad:

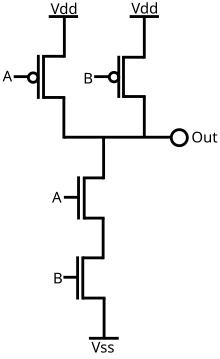

En la lógica CMOS , si las entradas A y B son altas, entonces ambos transistores NMOS (mitad inferior del diagrama) conducirán, ninguno de los transistores PMOS (mitad superior) conducirá, y se establecerá una ruta conductora entre la salida y Vss (tierra), lo que bajará la salida. Si las entradas A y B son bajas, entonces ninguno de los transistores NMOS conducirá, mientras que ambos transistores PMOS conducirán, estableciendo una ruta conductora entre la salida y Vdd (fuente de voltaje), lo que aumentará la salida. Si cualquiera de las entradas A o B es baja, uno de los transistores NMOS no conducirá, uno de los transistores PMOS sí, y se establecerá una ruta conductora entre la salida y Vdd (fuente de voltaje), lo que aumentará la salida. Como la única configuración de las dos entradas que da como resultado una salida baja es cuando ambas son altas, este circuito implementa una compuerta lógica NAND (NOT AND).

Una puerta NAND es una puerta universal , lo que significa que cualquier otra puerta puede representarse como una combinación de puertas NAND.

Una compuerta NOT se crea uniendo las entradas de una compuerta NAND. Dado que una compuerta NAND es equivalente a una compuerta AND seguida de una compuerta NOT, al unir las entradas de una compuerta NAND solo queda la compuerta NOT.

Una puerta AND se crea invirtiendo la salida de una puerta NAND como se muestra a continuación.

Si se examina la tabla de verdad de una compuerta NAND o se aplican las Leyes de De Morgan , se puede ver que si alguna de las entradas es 0, entonces la salida será 1. Sin embargo, para ser una compuerta OR, la salida debe ser 1 si alguna entrada es 1. Por lo tanto, si las entradas están invertidas, cualquier entrada alta activará una salida alta.

Una compuerta NOR es una compuerta OR con una salida invertida. La salida es alta cuando ni la entrada A ni la entrada B son altas.

Una compuerta XOR se construye conectando cuatro compuertas NAND como se muestra a continuación. Esta construcción implica un retardo de propagación tres veces mayor que el de una compuerta NAND simple.

Como alternativa, se puede construir una compuerta XOR considerando la forma normal disyuntiva , teniendo en cuenta que, según la Ley de De Morgan , una compuerta NAND es una compuerta OR con entrada invertida. Esta construcción utiliza cinco compuertas en lugar de cuatro.

Una compuerta XNOR se construye considerando la forma normal disyuntiva y teniendo en cuenta la Ley de De Morgan que una compuerta NAND es una compuerta OR con entrada invertida. Esta construcción implica un retardo de propagación tres veces mayor que el de una compuerta NAND simple y utiliza cinco compuertas.

Como alternativa, se puede utilizar la versión de 4 puertas de la compuerta XOR con un inversor. Esta construcción tiene un retardo de propagación cuatro veces mayor (en lugar de tres veces) que el de una compuerta NAND simple.

Un multiplexor o puerta MUX es una puerta de tres entradas que utiliza una de las entradas, llamada bit selector, para seleccionar una de las otras dos entradas, llamadas bits de datos , y emite solo el bit de datos seleccionado. [1]

Un demultiplexor realiza la función opuesta a la de un multiplexor: toma una única entrada y la canaliza a una de dos salidas posibles según un bit selector que especifica qué salida elegir. [1] [ ¿violación de derechos de autor ? ]