PCI Express ( Peripheral Component Interconnect Express ), abreviado oficialmente como PCIe o PCI-e , [2] es un estándar de bus de expansión de computadora serial de alta velocidad , diseñado para reemplazar los estándares de bus PCI , PCI-X y AGP más antiguos . Es la interfaz de placa base común para tarjetas gráficas , tarjetas de captura , tarjetas de sonido , adaptadores de host de unidad de disco duro , SSD , Wi-Fi y conexiones de hardware Ethernet de computadoras personales . [3] PCIe tiene numerosas mejoras con respecto a los estándares más antiguos, incluido un mayor rendimiento máximo del bus del sistema, un menor recuento de pines de E/S y una huella física más pequeña, mejor escalabilidad del rendimiento para dispositivos de bus, un mecanismo de detección y generación de informes de errores más detallado (Advanced Error Reporting, AER), [4] y funcionalidad nativa de intercambio en caliente . Las revisiones más recientes del estándar PCIe brindan soporte de hardware para la virtualización de E/S .

La interfaz eléctrica PCI Express se mide por la cantidad de carriles simultáneos. [5] (Un carril es una única línea de envío/recepción de datos, análoga a una "carretera de un carril" que tiene un carril de tráfico en ambas direcciones). La interfaz también se utiliza en una variedad de otros estándares, en particular la interfaz de tarjeta de expansión para computadoras portátiles llamada ExpressCard . También se utiliza en las interfaces de almacenamiento de SATA Express , U.2 (SFF-8639) y M.2 .

Las especificaciones formales son mantenidas y desarrolladas por el PCI-SIG (PCI Special Interest Group ), un grupo de más de 900 empresas que también mantiene las especificaciones PCI convencionales .

Conceptualmente, el bus PCI Express es un reemplazo serial de alta velocidad del antiguo bus PCI/PCI-X. [8] Una de las diferencias clave entre el bus PCI Express y el PCI antiguo es la topología del bus; PCI utiliza una arquitectura de bus paralelo compartido, en la que el host PCI y todos los dispositivos comparten un conjunto común de direcciones, datos y líneas de control. Por el contrario, PCI Express se basa en una topología punto a punto , con enlaces seriales separados que conectan cada dispositivo al complejo raíz (host). Debido a su topología de bus compartida, el acceso al bus PCI antiguo es arbitrado (en el caso de múltiples maestros) y limitado a un maestro a la vez, en una sola dirección. Además, el antiguo esquema de reloj PCI limita el reloj del bus al periférico más lento del bus (independientemente de los dispositivos involucrados en la transacción del bus). Por el contrario, un enlace de bus PCI Express admite la comunicación full-duplex entre dos puntos finales cualesquiera, sin limitación inherente en el acceso simultáneo a través de múltiples puntos finales.

En términos de protocolo de bus, la comunicación PCI Express está encapsulada en paquetes. El trabajo de empaquetar y desempaquetar el tráfico de datos y mensajes de estado lo maneja la capa de transacción del puerto PCI Express (descrita más adelante). Las diferencias radicales en la señalización eléctrica y el protocolo de bus requieren el uso de un factor de forma mecánico y conectores de expansión diferentes (y, por lo tanto, nuevas placas base y nuevas placas adaptadoras); las ranuras PCI y las ranuras PCI Express no son intercambiables. A nivel de software, PCI Express conserva la compatibilidad con versiones anteriores de PCI; el software del sistema PCI heredado puede detectar y configurar dispositivos PCI Express más nuevos sin compatibilidad explícita con el estándar PCI Express, aunque las nuevas características de PCI Express son inaccesibles.

El enlace PCI Express entre dos dispositivos puede variar en tamaño de uno a dieciséis carriles. En un enlace de varios carriles, los datos del paquete se distribuyen en varios carriles y el rendimiento máximo de los datos se escala con el ancho total del enlace. El recuento de carriles se negocia automáticamente durante la inicialización del dispositivo y puede ser restringido por cualquiera de los puntos finales. Por ejemplo, se puede insertar una tarjeta PCI Express de un solo carril (x1) en una ranura de varios carriles (x4, x8, etc.) y el ciclo de inicialización negocia automáticamente el mayor recuento de carriles mutuamente admitido. El enlace puede configurarse dinámicamente para utilizar menos carriles, lo que proporciona una tolerancia a fallos en caso de que haya carriles defectuosos o poco fiables. El estándar PCI Express define anchos de enlace de x1, x2, x4, x8 y x16. También se definieron enlaces PCIe 5.0, x12 y x32, pero nunca se utilizaron. [9] Esto permite que el bus PCI Express sirva tanto para aplicaciones sensibles a los costos donde no se necesita un alto rendimiento, como para aplicaciones críticas para el rendimiento, como gráficos 3D, redes ( 10 Gigabit Ethernet o Gigabit Ethernet multipuerto ) y almacenamiento empresarial ( SAS o Fibre Channel ). Las ranuras y los conectores solo se definen para un subconjunto de estos anchos, y los anchos de enlace intermedios utilizan el siguiente tamaño de ranura física más grande.

Como punto de referencia, un dispositivo PCI-X (133 MHz de 64 bits) y un dispositivo PCI Express 1.0 que utiliza cuatro carriles (x4) tienen aproximadamente la misma velocidad de transferencia máxima unidireccional de 1064 MB/s. El bus PCI Express tiene el potencial de funcionar mejor que el bus PCI-X en los casos en que varios dispositivos transfieren datos simultáneamente o si la comunicación con el periférico PCI Express es bidireccional .

Los dispositivos PCI Express se comunican a través de una conexión lógica denominada interconexión [10] o enlace . Un enlace es un canal de comunicación punto a punto entre dos puertos PCI Express que permite a ambos enviar y recibir solicitudes PCI ordinarias (configuración, E/S o lectura/escritura de memoria) e interrupciones ( INTx , MSI o MSI-X ). A nivel físico, un enlace se compone de uno o más carriles . [10] Los periféricos de baja velocidad (como una tarjeta Wi-Fi 802.11 ) utilizan un enlace de un solo carril (x1), mientras que un adaptador gráfico normalmente utiliza un enlace de 16 carriles (x16) mucho más amplio y, por lo tanto, más rápido.

Un carril se compone de dos pares de señalización diferencial , con un par para recibir datos y el otro para transmitir. Por lo tanto, cada carril se compone de cuatro cables o trazas de señal . Conceptualmente, cada carril se utiliza como un flujo de bytes full-duplex , que transporta paquetes de datos en formato "byte" de ocho bits simultáneamente en ambas direcciones entre los puntos finales de un enlace. [11] Los enlaces PCI Express físicos pueden contener 1, 4, 8 o 16 carriles. [12] [6] : 4, 5 [10] Los recuentos de carriles se escriben con un prefijo "x" (por ejemplo, "x8" representa una tarjeta o ranura de ocho carriles), siendo x16 el tamaño más grande de uso común. [13] Los tamaños de carril también se denominan a través de los términos "ancho" o "por", por ejemplo, una ranura de ocho carriles podría denominarse "por 8" o como "8 carriles de ancho".

Para conocer los tamaños de las tarjetas mecánicas, consulte a continuación.

La arquitectura de bus serial enlazado fue elegida en lugar del bus paralelo tradicional debido a las limitaciones inherentes de este último, incluyendo operación half-duplex , exceso de conteo de señales y ancho de banda inherentemente menor debido al sesgo de tiempo . El sesgo de tiempo resulta de señales eléctricas separadas dentro de una interfaz paralela que viajan a través de conductores de diferentes longitudes, en capas de placa de circuito impreso (PCB) potencialmente diferentes y a velocidades de señal posiblemente diferentes . A pesar de transmitirse simultáneamente como una sola palabra , las señales en una interfaz paralela tienen diferente duración de viaje y llegan a sus destinos en diferentes momentos. Cuando el período de reloj de la interfaz es más corto que la mayor diferencia de tiempo entre llegadas de señales, la recuperación de la palabra transmitida ya no es posible. Dado que el sesgo de tiempo en un bus paralelo puede ascender a unos pocos nanosegundos, la limitación de ancho de banda resultante está en el rango de cientos de megahercios.

Una interfaz serial no presenta sesgo de sincronización porque solo hay una señal diferencial en cada dirección dentro de cada carril, y no hay señal de reloj externa ya que la información de reloj está incorporada dentro de la propia señal serial. Como tal, las limitaciones típicas de ancho de banda en señales seriales están en el rango de varios gigahercios. PCI Express es un ejemplo de la tendencia general hacia reemplazar buses paralelos con interconexiones seriales; otros ejemplos incluyen Serial ATA (SATA), USB , Serial Attached SCSI (SAS), FireWire (IEEE 1394) y RapidIO . En video digital, los ejemplos de uso común son DVI , HDMI y DisplayPort .

El diseño serial multicanal aumenta la flexibilidad con su capacidad de asignar menos carriles para dispositivos más lentos.

Una tarjeta PCI Express cabe en una ranura de su tamaño físico o mayor (x16 es la más grande que se utiliza), pero puede que no encaje en una ranura PCI Express más pequeña; por ejemplo, una tarjeta x16 puede no encajar en una ranura x4 o x8. Algunas ranuras utilizan conectores abiertos para permitir tarjetas físicamente más largas y negociar la mejor conexión eléctrica y lógica disponible.

El número de carriles realmente conectados a una ranura también puede ser menor que el número admitido por el tamaño físico de la ranura. Un ejemplo es una ranura x16 que funciona a x4, que acepta cualquier tarjeta x1, x2, x4, x8 o x16, pero proporciona solo cuatro carriles. Su especificación puede leerse como "x16 (modo x4)", mientras que la notación "mecánica @ eléctrica" (por ejemplo, "x16 @ x4") también es común. [ cita requerida ] La ventaja es que dichas ranuras pueden acomodar una gama más amplia de tarjetas PCI Express sin requerir que el hardware de la placa base admita la velocidad de transferencia completa. Los tamaños mecánicos estándar son x1, x4, x8 y x16. Las tarjetas que utilizan un número de carriles diferente a los tamaños mecánicos estándar deben adaptarse físicamente al siguiente tamaño mecánico más grande (por ejemplo, una tarjeta x2 usa el tamaño x4, o una tarjeta x12 usa el tamaño x16).

Las tarjetas en sí están diseñadas y fabricadas en varios tamaños. Por ejemplo, las unidades de estado sólido (SSD) que vienen en forma de tarjetas PCI Express a menudo utilizan HHHL (altura media, longitud media) y FHHL (altura completa, longitud media) para describir las dimensiones físicas de la tarjeta. [15] [16]

Las tarjetas de video para juegos modernas (desde c. 2012 [17] ) generalmente exceden la altura y el grosor especificados en el estándar PCI Express, debido a la necesidad de ventiladores de enfriamiento más capaces y silenciosos , ya que las tarjetas de video para juegos a menudo emiten cientos de vatios de calor. [18] Las carcasas de computadora modernas suelen ser más anchas para acomodar estas tarjetas más altas, pero no siempre. Dado que las tarjetas de longitud completa (312 mm) son poco comunes, las carcasas modernas a veces no pueden adaptarse a ellas. El grosor de estas tarjetas también ocupa típicamente el espacio de 2 a 5 [19] ranuras PCIe. De hecho, incluso la metodología de cómo medir las tarjetas varía entre los proveedores, ya que algunos incluyen el tamaño del soporte de metal en las dimensiones y otros no.

Por ejemplo, comparando tres tarjetas de video de alta gama lanzadas en 2020: una tarjeta Sapphire Radeon RX 5700 XT mide 135 mm de altura (excluyendo el soporte de metal), que excede la altura estándar PCIe en 28 mm, [20] otra tarjeta Radeon RX 5700 XT de XFX mide 55 mm de grosor (es decir, 2,7 ranuras PCI a 20,32 mm), ocupando 3 ranuras PCIe, [21] mientras que una tarjeta de video Asus GeForce RTX 3080 ocupa dos ranuras y mide 140,1 mm × 318,5 mm × 57,8 mm, superando la altura, longitud y grosor máximos de PCI Express respectivamente. [22]

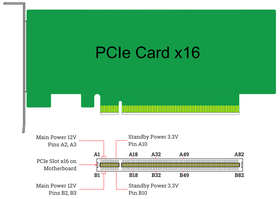

La siguiente tabla identifica los conductores de cada lado del conector de borde de una tarjeta PCI Express. El lado de soldadura de la placa de circuito impreso (PCB) es el lado A y el lado del componente es el lado B. [23] Los pines PRSNT1# y PRSNT2# deben ser ligeramente más cortos que el resto para garantizar que una tarjeta enchufada en caliente esté completamente insertada. El pin WAKE# usa voltaje completo para reactivar la computadora, pero debe elevarse desde la fuente de alimentación en espera para indicar que la tarjeta es capaz de reactivarse. [24]

Todas las tarjetas PCI Express pueden consumir hasta3 A en+3,3 V (9,9 W ). La cantidad de +12 V y la potencia total que pueden consumir dependen del factor de forma y la función de la tarjeta: [29] : 35–36 [30] [31]

Se añaden conectores opcionales75 W (6 pines) o150 W (8 pines) de potencia de +12 V para hasta300 W en total ( 2 × 75 W + 1 × 150 W ).

Algunas tarjetas usan dos conectores de 8 pines, pero esto aún no se ha estandarizado a partir de 2018 [update], por lo tanto, dichas tarjetas no deben llevar el logotipo oficial de PCI Express. Esta configuración permite un total de 375 W ( 1 × 75 W + 2 × 150 W ) y probablemente será estandarizada por PCI-SIG con el estándar PCI Express 4.0. [ necesita actualización ] El conector PCI Express de 8 pines podría confundirse con el conector EPS12V , que se usa principalmente para alimentar sistemas SMP y multinúcleo. Los conectores de alimentación son variantes de los conectores de la serie Molex Mini-Fit Jr. [32]

El conector 12VHPWR de 16 pines es un estándar para conectar unidades de procesamiento gráfico (GPU) a fuentes de alimentación de computadora para una entrega de energía de hasta 600 W. Se introdujo en 2022 para reemplazar los conectores de alimentación de 6 y 8 pines anteriores para GPU. El objetivo principal era satisfacer los crecientes requisitos de energía de las GPU de alto rendimiento. Fue reemplazado por una revisión menor llamada 12V-2x6, que cambió el conector para garantizar que los pines de detección solo hagan contacto si los pines de alimentación están colocados correctamente.

El conector original se adoptó formalmente como parte de PCI Express 5.x, [37] mientras que el diseño revisado del conector 12V-2x6 se adoptó más tarde. [38]

La tarjeta PCI Express Mini (también conocida como Mini PCI Express , Mini PCIe , Mini PCI-E , mPCIe y PEM ), basada en PCI Express, es un reemplazo del factor de forma Mini PCI . Fue desarrollada por PCI-SIG . El dispositivo host admite conectividad PCI Express y USB 2.0, y cada tarjeta puede usar cualquiera de los dos estándares. La mayoría de las computadoras portátiles fabricadas después de 2005 usan PCI Express para tarjetas de expansión; sin embargo, a partir de 2015 [update], muchos proveedores están pasando a usar el factor de forma M.2 más nuevo para este propósito. [39]

Debido a las diferentes dimensiones, las tarjetas PCI Express Mini no son físicamente compatibles con las ranuras PCI Express de tamaño completo estándar; sin embargo, existen adaptadores pasivos que permiten utilizarlas en ranuras de tamaño completo. [40]

Las dimensiones de las tarjetas mini PCI Express son 30 mm × 50,95 mm (ancho × largo) para una tarjeta mini completa. Hay un conector de borde de 52 pines , que consta de dos filas escalonadas en un paso de 0,8 mm. Cada fila tiene ocho contactos, un espacio equivalente a cuatro contactos, luego otros 18 contactos. Las placas tienen un grosor de 1,0 mm, sin contar los componentes. También se especifica una "media tarjeta mini" (a veces abreviada como HMC), que tiene aproximadamente la mitad de la longitud física de 26,8 mm. También hay tarjetas mini PCIe de tamaño medio que miden 30 x 31,90 mm, que es aproximadamente la mitad de la longitud de una tarjeta mini PCIe de tamaño completo. [41] [42]

Los conectores de borde de la tarjeta PCI Express Mini proporcionan múltiples conexiones y buses:

A pesar de compartir el factor de forma Mini PCI Express, una ranura mSATA no es necesariamente compatible eléctricamente con Mini PCI Express. Por esta razón, solo ciertos portátiles son compatibles con unidades mSATA. La mayoría de los sistemas compatibles se basan en la arquitectura de procesador Sandy Bridge de Intel, utilizando la plataforma Huron River. Los portátiles como las series ThinkPad T, W y X de Lenovo, lanzados en marzo-abril de 2011, tienen soporte para una tarjeta SSD mSATA en su ranura para tarjeta WWAN . Los ThinkPad Edge E220s/E420s y los Lenovo IdeaPad Y460/Y560/Y570/Y580 también admiten mSATA. [43] Por el contrario, la serie L, entre otras, solo puede admitir tarjetas M.2 que utilicen el estándar PCIe en la ranura WWAN.

Algunas computadoras portátiles (en particular, la Asus Eee PC , la Apple MacBook Air y las Dell mini9 y mini10) utilizan una variante de la tarjeta PCI Express Mini como SSD . Esta variante utiliza los pines reservados y varios no reservados para implementar el paso de interfaz SATA e IDE, manteniendo solo USB, líneas de tierra y, a veces, el bus PCIe x1 central intactos. [44] Esto hace que las unidades flash y de estado sólido "miniPCIe" vendidas para netbooks sean en gran medida incompatibles con las verdaderas implementaciones de PCI Express Mini.

Además, el SSD miniPCIe típico de Asus tiene 71 mm de largo, lo que hace que el modelo de 51 mm de Dell a menudo se denomine (incorrectamente) de longitud media. En 2009 se anunció un SSD Mini PCIe real de 51 mm, con dos capas de PCB apiladas que permiten una mayor capacidad de almacenamiento. El diseño anunciado conserva la interfaz PCIe, lo que lo hace compatible con la ranura mini PCIe estándar. Todavía no se ha desarrollado ningún producto funcional.

Intel cuenta con numerosas placas base para equipos de escritorio con ranura para minitarjeta PCIe x1 que normalmente no admiten SSD mSATA. En el sitio de asistencia técnica de Intel se incluye una lista de placas base para equipos de escritorio que admiten de forma nativa mSATA en la ranura para minitarjeta PCIe x1 (normalmente multiplexada con un puerto SATA). [45]

M.2 reemplaza al estándar mSATA y al Mini PCIe. [46] Las interfaces de bus de computadora proporcionadas a través del conector M.2 son PCI Express 3.0 (hasta cuatro carriles), Serial ATA 3.0 y USB 3.0 (un solo puerto lógico para cada uno de los dos últimos). Depende del fabricante del host o dispositivo M.2 elegir qué interfaces admitir, según el nivel deseado de compatibilidad del host y el tipo de dispositivo.

Las especificaciones del cableado externo PCI Express (también conocido como PCI Express externo , PCI Express cableado o ePCIe ) fueron publicadas por PCI-SIG en febrero de 2007. [47] [48]

Se han definido cables y conectores estándar para anchos de enlace x1, x4, x8 y x16, con una velocidad de transferencia de 250 MB/s por línea. El PCI-SIG también espera que la norma evolucione hasta alcanzar los 500 MB/s, como en PCI Express 2.0. Un ejemplo de los usos de Cabled PCI Express es una carcasa metálica que contiene una serie de ranuras PCIe y circuitos adaptadores PCIe a ePCIe. Este dispositivo no sería posible si no fuera por la especificación ePCIe.

OCuLink (que significa "enlace óptico-cobre", ya que Cu es el símbolo químico del cobre ) es una extensión de la "versión de cable de PCI Express". La versión 1.0 de OCuLink, lanzada en octubre de 2015, admite hasta 4 líneas PCIe 3.0 (3,9 GB/s) a través de cableado de cobre; es posible que aparezca una versión de fibra óptica en el futuro.

La versión más reciente de OCuLink, OCuLink-2, admite hasta 16 GB/s (PCIe 4.0 x8) [49] mientras que el ancho de banda máximo de un cable USB 4 es de 10 GB/s.

Aunque inicialmente estaba pensado para usarse en computadoras portátiles para la conexión de potentes cajas GPU externas, la popularidad de OCuLink radica principalmente en su uso para interconexiones PCIe en servidores, una aplicación más frecuente. [50]

Existen muchos otros formatos que utilizan o pueden utilizar PCIe, entre ellos:

El conector de ranura PCIe también puede admitir otros protocolos además de PCIe. Algunos chipsets Intel de la serie 9xx admiten Serial Digital Video Out , una tecnología patentada que utiliza una ranura para transmitir señales de video desde los gráficos integrados de la CPU host en lugar de PCIe, mediante un complemento compatible.

El protocolo de capa de transacción PCIe también se puede utilizar en otras interconexiones que no son PCIe eléctricamente:

En sus inicios, PCIe se denominó inicialmente HSI (por High Speed Interconnect, interconexión de alta velocidad ) y sufrió un cambio de nombre a 3GIO (por 3rd Generation I/O, E/S de tercera generación ) antes de decidirse finalmente por el nombre PCI-SIG, PCI Express . Un grupo de trabajo técnico llamado Arapaho Work Group (AWG) elaboró el estándar. En los borradores iniciales, el AWG estaba formado únicamente por ingenieros de Intel; posteriormente, el AWG se amplió para incluir a socios de la industria.

Desde entonces, PCIe ha experimentado varias revisiones grandes y pequeñas, mejorando el rendimiento y otras características.

En 2003, PCI-SIG introdujo PCIe 1.0a, con una velocidad de datos por carril de 250 MB/s y una velocidad de transferencia de 2,5 gigatransferencias por segundo (GT/s).

La velocidad de transferencia se expresa en transferencias por segundo en lugar de bits por segundo porque el número de transferencias incluye los bits de sobrecarga, que no proporcionan un rendimiento adicional; [56] PCIe 1.x utiliza un esquema de codificación 8b/10b , lo que da como resultado una sobrecarga del 20 % (= 2/10) en el ancho de banda del canal sin procesar. [57] Por lo tanto, en la terminología PCIe, la velocidad de transferencia se refiere a la velocidad de bits codificada: 2,5 GT/s es 2,5 Gbit/s en el enlace serial codificado. Esto corresponde a 2,0 Gbit/s de datos precodificados o 250 MB/s, lo que se conoce como rendimiento en PCIe.

En 2005, PCI-SIG [58] presentó PCIe 1.1. Esta especificación actualizada incluye aclaraciones y varias mejoras, pero es totalmente compatible con PCI Express 1.0a. No se realizaron cambios en la velocidad de datos.

PCI-SIG anunció la disponibilidad de la especificación PCI Express Base 2.0 el 15 de enero de 2007. [59] El estándar PCIe 2.0 duplica la velocidad de transferencia en comparación con PCIe 1.0 a 5 GT/s y el rendimiento por línea aumenta de 250 MB/s a 500 MB/s. En consecuencia, un conector PCIe de 16 líneas (x16) puede soportar un rendimiento agregado de hasta 8 GB/s.

Las ranuras de la placa base PCIe 2.0 son totalmente compatibles con las tarjetas PCIe v1.x. Las tarjetas PCIe 2.0 también suelen ser compatibles con las placas base PCIe 1.x, ya que utilizan el ancho de banda disponible de PCI Express 1.1. En general, las tarjetas gráficas o placas base diseñadas para la versión 2.0 funcionan, mientras que las otras son v1.1 o v1.0a.

El PCI-SIG también afirmó que PCIe 2.0 presenta mejoras en el protocolo de transferencia de datos punto a punto y su arquitectura de software. [60]

El primer chipset de Intel compatible con PCIe 2.0 fue el X38 y las placas comenzaron a enviarse de varios proveedores ( Abit , Asus , Gigabyte ) a partir del 21 de octubre de 2007. [61] AMD comenzó a admitir PCIe 2.0 con su serie de chipsets AMD 700 y nVidia comenzó con el MCP72 . [62] Todos los chipsets anteriores de Intel, incluido el chipset Intel P35 , admitían PCIe 1.1 o 1.0a. [63]

Al igual que 1.x, PCIe 2.0 utiliza un esquema de codificación 8b/10b , por lo que ofrece, por línea, una velocidad de transferencia máxima efectiva de 4 Gbit/s a partir de su velocidad de datos brutos de 5 GT/s.

PCI Express 2.1 (con su especificación del 4 de marzo de 2009) es compatible con una gran parte de los sistemas de gestión, soporte y resolución de problemas planificados para su implementación completa en PCI Express 3.0. Sin embargo, la velocidad es la misma que la de PCI Express 2.0. El aumento de potencia de la ranura rompe la compatibilidad con versiones anteriores entre las tarjetas PCI Express 2.1 y algunas placas base más antiguas con 1.0/1.0a, pero la mayoría de las placas base con conectores PCI Express 1.1 cuentan con una actualización de BIOS por parte de sus fabricantes a través de utilidades para admitir la compatibilidad con versiones anteriores de tarjetas con PCIe 2.1.

La revisión 3.0 de la especificación base PCI Express 3.0 se puso a disposición en noviembre de 2010, después de múltiples retrasos. En agosto de 2007, PCI-SIG anunció que PCI Express 3.0 tendría una tasa de bits de 8 gigatransferencias por segundo (GT/s) y que sería compatible con las implementaciones PCI Express existentes. En ese momento, también se anunció que la especificación final para PCI Express 3.0 se retrasaría hasta el segundo trimestre de 2010. [64] Las nuevas características de la especificación PCI Express 3.0 incluían una serie de optimizaciones para mejorar la señalización y la integridad de los datos, incluida la ecualización del transmisor y el receptor, mejoras de PLL , recuperación de datos de reloj y mejoras de canal de las topologías admitidas actualmente. [65]

Luego de un análisis técnico de seis meses sobre la viabilidad de escalar el ancho de banda de interconexión PCI Express, el análisis de PCI-SIG encontró que se podrían fabricar 8 gigatransferencias por segundo con la tecnología de proceso de silicio convencional y desplegarse con los materiales y la infraestructura de bajo costo existentes, manteniendo al mismo tiempo la compatibilidad total (con un impacto insignificante) con la pila de protocolos PCI Express.

PCI Express 3.0 actualizó el esquema de codificación a 128b/130b desde la codificación 8b/10b anterior , reduciendo la sobrecarga de ancho de banda del 20% de PCI Express 2.0 a aproximadamente 1,54% (= 2/130). La tasa de bits de 8 GT/s de PCI Express 3.0 ofrece efectivamente 985 MB/s por línea, casi duplicando el ancho de banda de línea en relación con PCI Express 2.0. [55]

El 18 de noviembre de 2010, el Grupo de Interés Especial de PCI publicó oficialmente la especificación PCI Express 3.0 finalizada para que sus miembros construyan dispositivos basados en esta nueva versión de PCI Express. [66]

En septiembre de 2013, se anunció el lanzamiento de la especificación PCI Express 3.1 a fines de 2013 o principios de 2014, consolidando varias mejoras en la especificación PCI Express 3.0 publicada en tres áreas: administración de energía, rendimiento y funcionalidad. [53] [67] Se lanzó en noviembre de 2014. [68]

El 29 de noviembre de 2011, PCI-SIG anunció preliminarmente PCI Express 4.0, [69] proporcionando una tasa de bits de 16 GT/s que duplica el ancho de banda proporcionado por PCI Express 3.0 a 31,5 GB/s en cada dirección para una configuración de 16 carriles, manteniendo al mismo tiempo la compatibilidad hacia atrás y hacia adelante tanto en el soporte de software como en la interfaz mecánica utilizada. [70] Las especificaciones de PCI Express 4.0 también traen OCuLink-2, una alternativa a Thunderbolt . La versión 2 de OCuLink tiene hasta 16 GT/s (16 GB/s en total para x8 carriles), [49] mientras que el ancho de banda máximo de un enlace Thunderbolt 3 es de 5 GB/s.

En junio de 2016, Cadence, PLDA y Synopsys demostraron la capa física, el controlador, el conmutador y otros bloques IP de PCIe 4.0 en la conferencia anual de desarrolladores de PCI SIG. [71]

Mellanox Technologies anunció el primer adaptador de red de 100 Gbit/s con PCIe 4.0 el 15 de junio de 2016, [72] y el primer adaptador de red de 200 Gbit/s con PCIe 4.0 el 10 de noviembre de 2016. [73]

En agosto de 2016, Synopsys presentó una configuración de prueba con FPGA que aceleraba un carril a velocidades PCIe 4.0 en el Intel Developer Forum . Su propiedad intelectual ha sido cedida bajo licencia a varias empresas que planean presentar sus chips y productos a finales de 2016. [74]

En el simposio IEEE Hot Chips de agosto de 2016, IBM anunció la primera CPU con soporte para PCIe 4.0, POWER9 . [75] [76]

PCI-SIG anunció oficialmente el lanzamiento de la especificación final PCI Express 4.0 el 8 de junio de 2017. [77] La especificación incluye mejoras en flexibilidad, escalabilidad y menor consumo de energía.

El 5 de diciembre de 2017, IBM anunció el primer sistema con ranuras PCIe 4.0, Power AC922. [78] [79]

NETINT Technologies presentó el primer SSD NVMe basado en PCIe 4.0 el 17 de julio de 2018, antes de la Flash Memory Summit 2018 [80]

El 9 de enero de 2019, AMD anunció que sus próximos procesadores basados en Zen 2 y el chipset X570 soportarían PCIe 4.0. [81] AMD esperaba habilitar un soporte parcial para chipsets más antiguos, pero la inestabilidad causada por trazas de la placa base que no se ajustaban a las especificaciones PCIe 4.0 lo hizo imposible. [82] [83]

Intel lanzó sus primeras CPU móviles con soporte para PCI Express 4.0 a mediados de 2020, como parte de la microarquitectura Tiger Lake . [84]

En junio de 2017, PCI-SIG anunció la especificación preliminar PCI Express 5.0. [77] Se esperaba que el ancho de banda aumentara a 32 GT/s, lo que produciría 63 GB/s en cada dirección en una configuración de 16 carriles. Se esperaba que la especificación preliminar se estandarizara en 2019. [ cita requerida ] Inicialmente, también se consideraron 25,0 GT/s por viabilidad técnica.

El 7 de junio de 2017 en PCI-SIG DevCon, Synopsys registró la primera demostración de PCI Express 5.0 a 32 GT/s. [85]

El 31 de mayo de 2018, PLDA anunció la disponibilidad de su IP de controlador PCIe 5.0 XpressRICH5 basado en el borrador 0.7 de la especificación PCIe 5.0 el mismo día. [86] [87]

El 10 de diciembre de 2018, el PCI SIG lanzó la versión 0.9 de la especificación PCIe 5.0 a sus miembros, [88] y el 17 de enero de 2019, PCI SIG anunció que la versión 0.9 había sido ratificada, y que la versión 1.0 se lanzaría en el primer trimestre de 2019. [89]

El 29 de mayo de 2019, PCI-SIG anunció oficialmente el lanzamiento de la especificación final PCI Express 5.0. [90]

El 20 de noviembre de 2019, Jiangsu Huacun presentó el primer controlador PCIe 5.0 HC9001 en un proceso de fabricación de 12 nm. [91] La producción comenzó en 2020.

El 17 de agosto de 2020, IBM anunció el procesador Power10 con PCIe 5.0 y hasta 32 carriles por módulo de un solo chip (SCM) y hasta 64 carriles por módulo de doble chip (DCM). [92]

El 9 de septiembre de 2021, IBM anunció el servidor Power E1080 Enterprise con fecha de disponibilidad prevista para el 17 de septiembre. [93] Puede tener hasta 16 SCM Power10 con un máximo de 32 ranuras por sistema que pueden actuar como PCIe 5.0 x8 o PCIe 4.0 x16. [94] Alternativamente, se pueden utilizar como ranuras PCIe 5.0 x16 para adaptadores de convertidor CXP ópticos opcionales que se conectan a cajones de expansión PCIe externos.

El 27 de octubre de 2021, Intel anunció la familia de CPU Intel Core de 12.ª generación, los primeros procesadores x86-64 de consumo del mundo con conectividad PCIe 5.0 (hasta 16 carriles). [95]

El 22 de marzo de 2022, Nvidia anunció la GPU Nvidia Hopper GH100, la primera GPU PCIe 5.0 del mundo. [96]

El 23 de mayo de 2022, AMD anunció su arquitectura Zen 4 con soporte para hasta 24 carriles de conectividad PCIe 5.0 en plataformas de consumo y 128 carriles en plataformas de servidor. [97] [98]

El 18 de junio de 2019, PCI-SIG anunció el desarrollo de la especificación PCI Express 6.0. Se espera que el ancho de banda aumente a 64 GT/s, lo que produce 128 GB/s en cada dirección en una configuración de 16 carriles, con una fecha de lanzamiento prevista para 2021. [99] El nuevo estándar utiliza modulación de amplitud de pulso de 4 niveles (PAM-4) con una corrección de error de avance de baja latencia (FEC) en lugar de modulación sin retorno a cero (NRZ). [100] A diferencia de las versiones anteriores de PCI Express, se utiliza la corrección de error de avance para aumentar la integridad de los datos y PAM-4 se utiliza como código de línea para que se transfieran dos bits por transferencia. Con una tasa de transferencia de datos de 64 GT/s (tasa de bits sin procesar), es posible alcanzar hasta 121 GB/s en cada dirección en la configuración x16. [99]

El 24 de febrero de 2020, se publicó la especificación PCI Express 6.0 revisión 0.5 (un "primer borrador" con todos los aspectos arquitectónicos y requisitos definidos). [101]

El 5 de noviembre de 2020, se publicó la especificación PCI Express 6.0 revisión 0.7 (un "borrador completo" con especificaciones eléctricas validadas mediante chips de prueba). [102]

El 6 de octubre de 2021, se publicó la especificación PCI Express 6.0 revisión 0.9 (un "borrador final"). [103]

El 11 de enero de 2022, PCI-SIG anunció oficialmente el lanzamiento de la especificación final PCI Express 6.0. [104]

El 18 de marzo de 2024, Nvidia anunció la GPU Nvidia Blackwell GB100, la primera GPU PCIe 6.0 del mundo. [105]

La codificación PAM-4 da como resultado una tasa de error de bit (BER) mucho más alta de 10 −6 (en comparación con 10 −12 anteriormente), por lo que en lugar de la codificación 128b/130b, se utiliza una corrección de error hacia adelante entrelazada de 3 vías (FEC) además de la verificación de redundancia cíclica (CRC). Un bloque de unidad de control de flujo (FLIT) fijo de 256 bytes transporta 242 bytes de datos, que incluyen paquetes de nivel de transacción (TLP) de tamaño variable y carga útil de capa de enlace de datos (DLLP); los 14 bytes restantes están reservados para CRC de 8 bytes y FEC de 6 bytes. [106] [107] El código Gray de 3 vías se utiliza en el modo PAM-4/FLIT para reducir la tasa de error; la interfaz no cambia a NRZ y codificación 128/130b incluso cuando se reentrena a velocidades de datos más bajas. [108] [109]

El 21 de junio de 2022, PCI-SIG anunció el desarrollo de la especificación PCI Express 7.0. [110] Ofrecerá una tasa de bits sin procesar de 128 GT/s y hasta 242 GB/s por dirección en la configuración x16, utilizando la misma señalización PAM4 que la versión 6.0. Se logrará duplicar la tasa de datos mediante el ajuste fino de los parámetros del canal para disminuir las pérdidas de señal y mejorar la eficiencia energética, pero se espera que la integridad de la señal sea un desafío. Se espera que la especificación esté finalizada en 2025.

El 2 de abril de 2024, PCI-SIG anunció el lanzamiento de la versión 0.5 de la especificación PCIe 7.0; PCI Express 7.0 sigue en camino para su lanzamiento en 2025. [111]

Algunos proveedores ofrecen productos PCIe sobre fibra, [112] [113] [114] con cables ópticos activos (AOC) para conmutación PCIe a mayor distancia en cajones de expansión PCIe, [115] [94] o en casos específicos donde el puente PCIe transparente es preferible a usar un estándar más convencional (como InfiniBand o Ethernet ) que puede requerir software adicional para soportarlo.

Thunderbolt fue desarrollado conjuntamente por Intel y Apple como una interfaz de alta velocidad de propósito general que combina un enlace PCIe lógico con DisplayPort y originalmente fue pensado como una interfaz completamente de fibra, pero debido a las dificultades iniciales para crear una interconexión de fibra amigable para el consumidor, casi todas las implementaciones son sistemas de cobre. Una excepción notable, el Sony VAIO Z VPC-Z2, utiliza un puerto USB no estándar con un componente óptico para conectarse a un adaptador de pantalla PCIe externo. Apple ha sido el principal impulsor de la adopción de Thunderbolt hasta 2011, aunque varios otros proveedores [116] han anunciado nuevos productos y sistemas que incluyen Thunderbolt. Thunderbolt 3 forma la base delestándar USB4 .

La especificación PCIe móvil (abreviada como M-PCIe ) permite que la arquitectura PCI Express funcione sobre la tecnología de capa física M-PHY de MIPI Alliance . Basándose en la adopción generalizada ya existente de M-PHY y su diseño de bajo consumo, Mobile PCIe permite que los dispositivos móviles utilicen PCI Express. [117]

Hay 5 versiones/puntos de control principales en una especificación PCI-SIG: [118]

Históricamente, los primeros en adoptar una nueva especificación PCIe generalmente comienzan a diseñar con el borrador 0.5, ya que pueden construir con confianza la lógica de su aplicación en torno a la nueva definición de ancho de banda y, a menudo, incluso comienzan a desarrollar para cualquier característica nueva del protocolo. Sin embargo, en la etapa del borrador 0.5, todavía existe una gran probabilidad de cambios en la implementación real de la capa de protocolo PCIe, por lo que los diseñadores responsables de desarrollar estos bloques internamente pueden ser más reacios a comenzar a trabajar que aquellos que usan IP de interfaz de fuentes externas.

El enlace PCIe está construido alrededor de pares dedicados unidireccionales de conexiones seriales (de 1 bit) punto a punto, conocidas como carriles . Esto contrasta marcadamente con la conexión PCI anterior, que es un sistema basado en bus donde todos los dispositivos comparten el mismo bus paralelo bidireccional de 32 o 64 bits.

PCI Express es un protocolo en capas que consta de una capa de transacción , una capa de enlace de datos y una capa física . La capa de enlace de datos se subdivide para incluir una subcapa de control de acceso al medio (MAC). La capa física se subdivide en subcapas lógicas y eléctricas. La subcapa lógica física contiene una subcapa de codificación física (PCS). Los términos se tomaron prestados del modelo de protocolo de red IEEE 802 .

La especificación de la capa física PCIe ( PHY , PCIEPHY , PCI Express PHY o PCIe PHY ) se divide en dos subcapas, que corresponden a especificaciones eléctricas y lógicas. La subcapa lógica a veces se divide en una subcapa MAC y una PCS, aunque esta división no es formalmente parte de la especificación PCIe. Una especificación publicada por Intel, la Interfaz PHY para PCI Express (PIPE), [120] define la partición funcional MAC/PCS y la interfaz entre estas dos subcapas. La especificación PIPE también identifica la capa de conexión de medios físicos (PMA), que incluye el serializador/deserializador (SerDes) y otros circuitos analógicos; sin embargo, dado que las implementaciones de SerDes varían en gran medida entre los proveedores de ASIC , PIPE no especifica una interfaz entre el PCS y PMA.

A nivel eléctrico, cada carril consta de dos pares diferenciales unidireccionales que funcionan a 2,5, 5, 8, 16 o 32 Gbit /s, en función de las capacidades negociadas. La transmisión y la recepción son pares diferenciales separados, lo que da un total de cuatro cables de datos por carril.

Una conexión entre dos dispositivos PCIe se conoce como enlace y se construye a partir de una colección de uno o más carriles . Todos los dispositivos deben admitir como mínimo un enlace de un solo carril (x1). Los dispositivos pueden admitir opcionalmente enlaces más amplios compuestos de hasta 32 carriles. [121] [122] Esto permite una muy buena compatibilidad de dos maneras:

En ambos casos, PCIe negocia el mayor número de carriles admitidos mutuamente. Muchas tarjetas gráficas, placas base y versiones de BIOS están verificadas para admitir conectividad x1, x4, x8 y x16 en la misma conexión.

El ancho de un conector PCIe es de 8,8 mm, mientras que la altura es de 11,25 mm y la longitud es variable. La sección fija del conector tiene una longitud de 11,65 mm y contiene dos filas de 11 pines cada una (22 pines en total), mientras que la longitud de la otra sección es variable según el número de carriles. Los pines están espaciados a intervalos de 1 mm y el grosor de la tarjeta que entra en el conector es de 1,6 mm. [123] [124]

PCIe envía todos los mensajes de control, incluidas las interrupciones, a través de los mismos enlaces que se utilizan para los datos. El protocolo serial nunca se puede bloquear, por lo que la latencia sigue siendo comparable a la del PCI convencional, que tiene líneas de interrupción dedicadas. Cuando se tiene en cuenta el problema de compartir IRQ de interrupciones basadas en pines y el hecho de que las interrupciones señalizadas por mensaje (MSI) pueden eludir una APIC de E/S y enviarse directamente a la CPU, el rendimiento de MSI termina siendo sustancialmente mejor. [125]

Los datos transmitidos en enlaces de múltiples carriles se entrelazan, lo que significa que cada byte sucesivo se envía por carriles sucesivos. La especificación PCIe se refiere a este entrelazado como segmentación de datos . Si bien requiere una complejidad de hardware significativa para sincronizar (o desviar ) los datos segmentados entrantes, la segmentación puede reducir significativamente la latencia del byte n en un enlace. Si bien los carriles no están estrechamente sincronizados, existe un límite para la desviación de carril a carril de 20/8/6 ns para 2,5/5/8 GT/s para que los búferes de hardware puedan realinear los datos segmentados. [126] Debido a los requisitos de relleno, la segmentación puede no reducir necesariamente la latencia de pequeños paquetes de datos en un enlace.

Al igual que con otros protocolos de transmisión en serie de alta velocidad de datos, el reloj está integrado en la señal. A nivel físico, PCI Express 2.0 utiliza el esquema de codificación 8b/10b [55] (código de línea) para garantizar que las cadenas de dígitos idénticos consecutivos (ceros o unos) tengan una longitud limitada. Esta codificación se utilizó para evitar que el receptor perdiera la pista de dónde están los bordes de los bits. En este esquema de codificación, cada ocho bits de datos de carga útil (sin codificar) se reemplazan con 10 bits (codificados) de datos de transmisión, lo que causa una sobrecarga del 20% en el ancho de banda eléctrico. Para mejorar el ancho de banda disponible, la versión 3.0 de PCI Express utiliza en cambio la codificación 128b/130b (1,54% de sobrecarga). La codificación de línea limita la longitud de ejecución de las cadenas de dígitos idénticos en los flujos de datos y garantiza que el receptor se mantenga sincronizado con el transmisor a través de la recuperación del reloj .

Se logra un equilibrio deseable (y, por lo tanto, una densidad espectral ) de bits 0 y 1 en el flujo de datos mediante la operación XOR de un polinomio binario conocido como " codificador " del flujo de datos en una topología de retroalimentación. Como se conoce el polinomio codificador, los datos se pueden recuperar aplicando la operación XOR una segunda vez. Tanto el paso de codificación como el de decodificación se llevan a cabo en hardware.

Simplex dual en PCIe significa que hay dos canales simplex en cada carril PCIe. Simplex significa que la comunicación solo es posible en una dirección. Al tener dos canales simplex, se hace posible la comunicación bidireccional. Se utiliza un par diferencial para cada canal. [127] [128] [129]

La capa de enlace de datos realiza tres servicios vitales para el enlace PCIe:

En el lado de transmisión, la capa de enlace de datos genera un número de secuencia creciente para cada TLP saliente. Sirve como etiqueta de identificación única para cada TLP transmitido y se inserta en el encabezado del TLP saliente. También se agrega un código de verificación de redundancia cíclica de 32 bits (conocido en este contexto como Link CRC o LCRC) al final de cada TLP saliente.

En el lado de recepción, el LCRC y el número de secuencia del TLP recibido se validan en la capa de enlace. Si la comprobación del LCRC falla (lo que indica un error de datos) o el número de secuencia está fuera de rango (no es consecutivo con respecto al último TLP válido recibido), entonces el TLP defectuoso, así como cualquier TLP recibido después del TLP defectuoso, se consideran inválidos y se descartan. El receptor envía un mensaje de reconocimiento negativo (NAK) con el número de secuencia del TLP inválido, solicitando la retransmisión de todos los TLP anteriores a ese número de secuencia. Si el TLP recibido pasa la comprobación del LCRC y tiene el número de secuencia correcto, se trata como válido. El receptor de enlace incrementa el número de secuencia (que rastrea el último TLP bueno recibido) y reenvía el TLP válido a la capa de transacción del receptor. Se envía un mensaje ACK al transmisor remoto, indicando que el TLP se recibió correctamente (y, por extensión, todos los TLP con números de secuencia anteriores).

Si el transmisor recibe un mensaje NAK o no recibe ningún acuse de recibo (NAK o ACK) hasta que transcurra un período de tiempo de espera, el transmisor debe retransmitir todos los TLP que no tengan un acuse de recibo positivo (ACK). Salvo que se produzca un mal funcionamiento persistente del dispositivo o del medio de transmisión, la capa de enlace presenta una conexión fiable con la capa de transacción, ya que el protocolo de transmisión garantiza la entrega de TLP a través de un medio no fiable.

Además de enviar y recibir paquetes TLP generados por la capa de transacción, la capa de enlace de datos también genera y consume paquetes de capa de enlace de datos (DLLP). Las señales ACK y NAK se comunican a través de los DLLP, al igual que algunos mensajes de administración de energía e información de crédito de control de flujo (en nombre de la capa de transacción).

En la práctica, la cantidad de TLP en vuelo sin reconocimiento en el enlace está limitada por dos factores: el tamaño del búfer de reproducción del transmisor (que debe almacenar una copia de todos los TLP transmitidos hasta que el receptor remoto los reconozca) y los créditos de control de flujo emitidos por el receptor a un transmisor. PCI Express requiere que todos los receptores emitan una cantidad mínima de créditos para garantizar que un enlace permita enviar TLP de PCIConfig y TLP de mensajes.

PCI Express implementa transacciones divididas (transacciones con solicitud y respuesta separadas por tiempo), lo que permite que el enlace transporte otro tráfico mientras el dispositivo de destino recopila datos para la respuesta.

PCI Express utiliza un control de flujo basado en créditos. En este esquema, un dispositivo anuncia una cantidad inicial de crédito para cada búfer recibido en su capa de transacción. El dispositivo en el extremo opuesto del enlace, al enviar transacciones a este dispositivo, cuenta la cantidad de créditos que cada TLP consume de su cuenta. El dispositivo emisor solo puede transmitir un TLP cuando al hacerlo no hace que su recuento de créditos consumidos exceda su límite de crédito. Cuando el dispositivo receptor termina de procesar el TLP desde su búfer, envía una señal de devolución de créditos al dispositivo emisor, lo que aumenta el límite de crédito en la cantidad restaurada. Los contadores de créditos son contadores modulares, y la comparación de los créditos consumidos con el límite de crédito requiere aritmética modular . La ventaja de este esquema (en comparación con otros métodos como los estados de espera o los protocolos de transferencia basados en protocolos de enlace) es que la latencia de la devolución de créditos no afecta el rendimiento, siempre que no se alcance el límite de crédito. Esta suposición generalmente se cumple si cada dispositivo está diseñado con tamaños de búfer adecuados.

A menudo se dice que PCIe 1.x admite una velocidad de datos de 250 MB/s en cada dirección y por carril. Esta cifra es un cálculo a partir de la velocidad de señalización física (2,5 gigabaudios ) dividida por la sobrecarga de codificación (10 bits por byte). Esto significa que una tarjeta PCIe de dieciséis carriles (x16) sería teóricamente capaz de transmitir 16x250 MB/s = 4 GB/s en cada dirección. Si bien esto es correcto en términos de bytes de datos, los cálculos más significativos se basan en la velocidad de carga útil de datos utilizable, que depende del perfil del tráfico, que es una función de la aplicación de alto nivel (software) y los niveles de protocolo intermedios.

Al igual que otros sistemas de interconexión serial de alta velocidad de datos, PCIe tiene una sobrecarga de protocolo y procesamiento debido a la robustez de transferencia adicional (CRC y reconocimientos). Las transferencias unidireccionales continuas largas (como las típicas en los controladores de almacenamiento de alto rendimiento) pueden acercarse a >95% de la velocidad de datos (carril) sin procesar de PCIe. Estas transferencias también se benefician más de un mayor número de carriles (x2, x4, etc.) Pero en aplicaciones más típicas (como un controlador USB o Ethernet ), el perfil de tráfico se caracteriza por paquetes de datos cortos con reconocimientos forzados frecuentes. [130] Este tipo de tráfico reduce la eficiencia del enlace, debido a la sobrecarga del análisis de paquetes y las interrupciones forzadas (ya sea en la interfaz de host del dispositivo o en la CPU de la PC). Al ser un protocolo para dispositivos conectados a la misma placa de circuito impreso , no requiere la misma tolerancia a los errores de transmisión que un protocolo para la comunicación a distancias más largas y, por lo tanto, esta pérdida de eficiencia no es particular de PCIe.

Como ocurre con cualquier enlace de comunicación de tipo red, parte del ancho de banda bruto se consume por la sobrecarga del protocolo: [131]

Por ejemplo, una línea PCIe 1.x ofrece una velocidad de datos sobre la capa física de 250 MB/s (símplex). Este no es el ancho de banda de la carga útil, sino el ancho de banda de la capa física: una línea PCIe debe transportar información adicional para una funcionalidad completa. [131]

La sobrecarga de Gen2 es entonces de 20, 24 o 28 bytes por transacción. [ aclaración necesaria ] [ cita necesaria ]

La sobrecarga de Gen3 es entonces de 22, 26 o 30 bytes por transacción. [ aclaración necesaria ] [ cita necesaria ]

La eficiencia para una carga útil de 128 bytes es del 86 %, y del 98 % para una carga útil de 1024 bytes. Para accesos pequeños, como configuraciones de registros (4 bytes), la eficiencia cae hasta el 16 %. [ cita requerida ]

El tamaño máximo de carga útil (MPS) se establece en todos los dispositivos en función del máximo más pequeño de cualquier dispositivo de la cadena. Si un dispositivo tiene un MPS de 128 bytes, todos los dispositivos del árbol deben establecer su MPS en 128 bytes. En este caso, el bus tendrá una eficiencia máxima del 86 % para las escrituras. [131] : 3

PCI Express funciona en aplicaciones industriales, de servidor y de consumo, como una interconexión a nivel de placa base (para vincular periféricos montados en la placa base), una interconexión de placa posterior pasiva y como una interfaz de tarjeta de expansión para placas complementarias.

En prácticamente todos los PC modernos (a partir de 2012 [update]), desde los portátiles y los ordenadores de sobremesa hasta los servidores de datos empresariales, el bus PCIe funciona como la interconexión principal a nivel de placa base, conectando el sistema host-procesador con los periféricos integrados (circuitos integrados montados en la superficie) y los periféricos adicionales (tarjetas de expansión). En la mayoría de estos sistemas, el bus PCIe coexiste con uno o más buses PCI antiguos, para lograr compatibilidad con versiones anteriores de la gran cantidad de periféricos PCI antiguos.

A partir de 2013 [update], PCI Express ha reemplazado a AGP como la interfaz predeterminada para tarjetas gráficas en sistemas nuevos. Casi todos los modelos de tarjetas gráficas lanzados desde 2010 por AMD (ATI) y Nvidia usan PCI Express. Nvidia usó la transferencia de datos de alto ancho de banda de PCIe para su tecnología Scalable Link Interface (SLI), que permitió que varias tarjetas gráficas del mismo chipset y número de modelo se ejecutaran en tándem, lo que permitió un mayor rendimiento. [ cita requerida ] Esta interfaz, desde entonces, ha sido descontinuada. AMD también ha desarrollado un sistema multi-GPU basado en PCIe llamado CrossFire . [ cita requerida ] AMD, Nvidia e Intel han lanzado chipsets de placa base que admiten hasta cuatro ranuras PCIe x16, lo que permite configuraciones de tarjetas tri-GPU y quad-GPU.

En teoría, una tarjeta PCIe externa podría proporcionar a un portátil la potencia gráfica de un ordenador de sobremesa, conectando un portátil con cualquier tarjeta de vídeo PCIe de sobremesa (encerrada en su propia carcasa externa, con fuente de alimentación y refrigeración); esto es posible con una interfaz ExpressCard o Thunderbolt . Una interfaz ExpressCard proporciona velocidades de bits de 5 Gbit/s (rendimiento de 0,5 GB/s), mientras que una interfaz Thunderbolt proporciona velocidades de bits de hasta 40 Gbit/s (rendimiento de 5 GB/s).

En 2006, Nvidia desarrolló la familia de GPU PCIe externas Quadro Plex que se pueden utilizar para aplicaciones gráficas avanzadas para el mercado profesional. [132] Estas tarjetas de video requieren una ranura PCI Express x8 o x16 para la tarjeta del lado del host, que se conecta al Plex a través de un VHDCI que lleva ocho carriles PCIe. [133]

En 2008, AMD anunció la tecnología ATI XGP , basada en un sistema de cableado propietario que es compatible con transmisiones de señales PCIe x8. [134] Este conector está disponible en los portátiles Fujitsu Amilo y Acer Ferrari One. Fujitsu lanzó su carcasa AMILO GraphicBooster para XGP poco después. [135] Alrededor de 2010, Acer lanzó la base gráfica Dynavivid para XGP. [136]

En 2010, se introdujeron concentradores de tarjetas externas que se pueden conectar a una computadora portátil o de escritorio a través de una ranura PCI ExpressCard. Estos concentradores pueden aceptar tarjetas gráficas de tamaño completo. Los ejemplos incluyen MSI GUS, [137] ViDock de Village Instrument, [138] la estación XG de Asus , el adaptador Bplus PE4H V3.2, [139] así como dispositivos DIY más improvisados. [140] Sin embargo, estas soluciones están limitadas por el tamaño (a menudo solo x1) y la versión de la ranura PCIe disponible en una computadora portátil.

La interfaz Intel Thunderbolt ha proporcionado una nueva opción para conectar una tarjeta PCIe externamente. Magma ha lanzado el ExpressBox 3T, que puede albergar hasta tres tarjetas PCIe (dos a x8 y una a x4). [141] MSI también lanzó el Thunderbolt GUS II, un chasis PCIe dedicado a tarjetas de video. [142] Otros productos como el Echo Express de Sonnet [143] y el mLink de mLogic son chasis PCIe Thunderbolt en un formato más pequeño. [144]

En 2017, se introdujeron concentradores de tarjetas externas con más funciones, como el Razer Core, que tiene una interfaz PCIe x16 de longitud completa. [145]

El protocolo PCI Express se puede utilizar como interfaz de datos para dispositivos de memoria flash , como tarjetas de memoria y unidades de estado sólido (SSD).

La tarjeta XQD es un formato de tarjeta de memoria que utiliza PCI Express, desarrollado por la Asociación CompactFlash, con velocidades de transferencia de hasta 1 GB/s. [146]

Muchos SSD de clase empresarial y alto rendimiento están diseñados como tarjetas controladoras RAID PCI Express . [ cita requerida ] Antes de que NVMe se estandarizara, muchas de estas tarjetas utilizaban interfaces propietarias y controladores personalizados para comunicarse con el sistema operativo; tenían tasas de transferencia mucho más altas (más de 1 GB/s) e IOPS (más de un millón de operaciones de E/S por segundo) en comparación con las unidades Serial ATA o SAS . [ cuantificar ] [147] [148] Por ejemplo, en 2011, OCZ y Marvell desarrollaron conjuntamente un controlador de unidad de estado sólido PCI Express nativo para una ranura PCI Express 3.0 x16 con una capacidad máxima de 12 TB y un rendimiento de hasta 7,2 GB/s en transferencias secuenciales y hasta 2,52 millones de IOPS en transferencias aleatorias. [149] [ ¿relevante? ]

SATA Express era una interfaz para conectar SSD a través de puertos compatibles con SATA, proporcionando opcionalmente múltiples líneas PCI Express como una conexión PCI Express pura al dispositivo de almacenamiento conectado. [150] M.2 es una especificación para tarjetas de expansión de computadora montadas internamente y conectores asociados, que también utiliza múltiples líneas PCI Express. [151]

Los dispositivos de almacenamiento PCI Express pueden implementar tanto la interfaz lógica AHCI para compatibilidad con versiones anteriores como la interfaz lógica NVM Express para operaciones de E/S mucho más rápidas gracias al uso del paralelismo interno que ofrecen dichos dispositivos. Los SSD de clase empresarial también pueden implementar SCSI sobre PCI Express . [152]

Ciertas aplicaciones de centros de datos (como grandes clústeres de computadoras ) requieren el uso de interconexiones de fibra óptica debido a las limitaciones de distancia inherentes al cableado de cobre. Por lo general, un estándar orientado a la red como Ethernet o Fibre Channel es suficiente para estas aplicaciones, pero en algunos casos la sobrecarga introducida por los protocolos enrutables no es deseable y se necesita una interconexión de nivel inferior, como InfiniBand , RapidIO o NUMAlink . Los estándares de bus local como PCIe y HyperTransport se pueden utilizar en principio para este propósito, [153] pero a partir de 2015 [update], las soluciones solo están disponibles de proveedores especializados como Dolphin ICS y TTTech Auto.

Otros estándares de comunicaciones basados en arquitecturas seriales de alto ancho de banda incluyen InfiniBand , RapidIO , HyperTransport , Intel QuickPath Interconnect , la Interfaz de Procesador de la Industria Móvil (MIPI) y NVLink . Las diferencias se basan en las compensaciones entre flexibilidad y extensibilidad frente a latencia y sobrecarga. Por ejemplo, hacer que el sistema sea conectable en caliente, como ocurre con Infiniband pero no con PCI Express, requiere que el software realice un seguimiento de los cambios en la topología de la red. [ cita requerida ]

Otro ejemplo es acortar los paquetes para reducir la latencia (como se requiere si un bus debe funcionar como interfaz de memoria). Los paquetes más pequeños implican que los encabezados de los paquetes consumen un mayor porcentaje del paquete, lo que reduce el ancho de banda efectivo. Algunos ejemplos de protocolos de bus diseñados para este propósito son RapidIO y HyperTransport. [ cita requerida ]

PCI Express se encuentra en algún punto intermedio, [ aclaración necesaria ] diseñado para ser una interconexión de sistemas ( bus local ) en lugar de una interconexión de dispositivos o un protocolo de red enrutada. Además, su objetivo de diseño de transparencia del software limita el protocolo y aumenta un poco su latencia. [ cita requerida ]

Los retrasos en las implementaciones de PCIe 4.0 llevaron a que el consorcio Gen-Z , el esfuerzo CCIX y una Interfaz de Procesador Acelerador Coherente (CAPI) abierta se anunciaran a fines de 2016. [154]

El 11 de marzo de 2019, Intel presentó Compute Express Link (CXL) , un nuevo bus de interconexión basado en la infraestructura de capa física PCI Express 5.0. Los promotores iniciales de la especificación CXL incluyeron: Alibaba , Cisco , Dell EMC , Facebook , Google , HPE , Huawei , Intel y Microsoft . [155]

La lista de integradores de PCI-SIG incluye productos fabricados por empresas miembros de PCI-SIG que han pasado pruebas de cumplimiento. La lista incluye conmutadores, puentes, tarjetas de interfaz de red, unidades SSD, etc. [156]

{{cite web}}: CS1 maint: numeric names: authors list (link)Este ECN define las codificaciones de tipo de conector para el nuevo conector 12V-2x6. Este conector, definido en CEM 5.1, reemplaza al conector 12VHPWR.