En lógica digital, una compuerta inversora o NOT es una compuerta lógica que implementa la negación lógica . Emite un bit opuesto al bit que se le introduce. Los bits se implementan normalmente como dos niveles de voltaje diferentes.

La compuerta NOT genera un cero cuando se le da un uno, y un uno cuando se le da un cero. Por lo tanto, invierte sus entradas. Coloquialmente, esta inversión de bits se llama "inversión de bits". [1] Al igual que con todas las compuertas lógicas binarias, se pueden utilizar otros pares de símbolos (como verdadero y falso, o alto y bajo) en lugar de uno y cero.

Es equivalente al operador de negación lógica (¬) en lógica matemática . Debido a que solo tiene una entrada, es una operación unaria y tiene el tipo más simple de tabla de verdad . También se le llama puerta del complemento [2] porque produce el complemento a unos de un número binario, intercambiando 0 y 1.

La puerta NOT es una de las tres puertas lógicas básicas a partir de las cuales se puede construir cualquier circuito booleano . Junto con la puerta AND y la puerta OR , se puede implementar cualquier función en matemáticas binarias. Todas las demás puertas lógicas se pueden construir a partir de estas tres. [3]

Los términos "inversor programable" o "inversor controlado" no se refieren a esta puerta; en cambio, estos términos se refieren a la puerta XOR porque puede funcionar condicionalmente como una puerta NOT. [1] [3]

El símbolo tradicional de un circuito inversor es un triángulo que toca un pequeño círculo o "burbuja". Las líneas de entrada y salida están unidas al símbolo; la burbuja normalmente está unida a la línea de salida. Para simbolizar la entrada activa baja , a veces la burbuja se coloca en la línea de entrada. [4] A veces solo se utiliza la parte circular del símbolo, y se la une a la entrada o salida de otra compuerta; los símbolos para NAND y NOR se forman de esta manera. [3]

Una barra o raya superior (‾) sobre una variable puede indicar una negación (o inversión o complemento) realizada por una compuerta NOT. [4] También se utiliza una barra (/) antes de la variable. [3]

Un circuito inversor genera una tensión que representa el nivel lógico opuesto a su entrada. Su función principal es invertir la señal de entrada aplicada. Si la entrada aplicada es baja, la salida se vuelve alta y viceversa. Los inversores se pueden construir utilizando un solo transistor NMOS o un solo transistor PMOS acoplado a una resistencia . Dado que este enfoque de "drenaje resistivo" utiliza solo un tipo de transistor, se puede fabricar a bajo costo. Sin embargo, debido a que la corriente fluye a través de la resistencia en uno de los dos estados, la configuración de drenaje resistivo tiene desventajas para el consumo de energía y la velocidad de procesamiento. Alternativamente, los inversores se pueden construir utilizando dos transistores complementarios en una configuración CMOS . Esta configuración reduce en gran medida el consumo de energía ya que uno de los transistores siempre está apagado en ambos estados lógicos. [5] La velocidad de procesamiento también se puede mejorar debido a la resistencia relativamente baja en comparación con los dispositivos de tipo solo NMOS o solo PMOS. Los inversores también se pueden construir con transistores de unión bipolar (BJT) en una configuración de lógica de resistencia-transistor (RTL) o de lógica de transistor-transistor (TTL).

Los circuitos electrónicos digitales funcionan a niveles de voltaje fijos correspondientes a un 0 o 1 lógico (ver binario ). Un circuito inversor funciona como la puerta lógica básica para intercambiar entre esos dos niveles de voltaje. La implementación determina el voltaje real, pero los niveles comunes incluyen (0, +5 V) para circuitos TTL.

El inversor es un componente básico de la electrónica digital. Los multiplexores, decodificadores, máquinas de estados y otros dispositivos digitales sofisticados pueden utilizar inversores.

El inversor hexadecimal es un circuito integrado que contiene seis inversores ( hexa ). Por ejemplo, el chip TTL 7404 que tiene 14 pines y el chip CMOS 4049 que tiene 16 pines, 2 de los cuales se utilizan para alimentación/referencia y 12 de los cuales se utilizan para las entradas y salidas de los seis inversores (el 4049 tiene 2 pines sin conexión).

es la representación analítica de la puerta NOT:

Si no hay puertas NOT específicas disponibles, se puede crear una a partir de las puertas NAND o NOR universales , [6] o una puerta XOR configurando una entrada en alta.

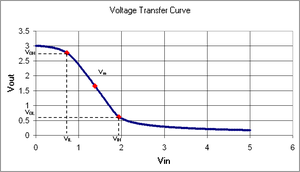

La calidad de los inversores digitales suele medirse mediante la curva de transferencia de tensión (VTC), que es un gráfico de la tensión de salida frente a la de entrada. A partir de este gráfico, se pueden obtener parámetros del dispositivo, como la tolerancia al ruido, la ganancia y los niveles de lógica de funcionamiento.

Idealmente, el VTC aparece como una función de paso invertido (esto indicaría una conmutación precisa entre encendido y apagado ), pero en los dispositivos reales existe una región de transición gradual. El VTC indica que, para un voltaje de entrada bajo, el circuito genera un voltaje alto; para un voltaje de entrada alto, la salida se reduce gradualmente hacia el nivel bajo. La pendiente de esta región de transición es una medida de calidad: las pendientes pronunciadas (casi verticales) producen una conmutación precisa.

La tolerancia al ruido se puede medir comparando la entrada mínima con la salida máxima para cada región de operación (encendido / apagado).

Dado que la región de transición es empinada y aproximadamente lineal, una puerta lógica digital inversora CMOS polarizada correctamente se puede utilizar como un amplificador lineal analógico de alta ganancia [7] [8] [9] [10] [11] o incluso combinarse para formar un amplificador operacional . [12] La ganancia máxima se logra cuando los puntos operativos de entrada y salida son el mismo voltaje, que se puede polarizar conectando una resistencia entre la salida y la entrada. [13]