La puerta NOR es una puerta lógica digital que implementa NOR lógico : se comporta según la tabla de verdad de la derecha. Se obtiene una salida ALTA (1) si ambas entradas a la puerta son BAJAS (0); si una o ambas entradas son ALTAS (1), se obtiene una salida BAJA (0). NOR es el resultado de la negación del operador OR . En algunos sentidos, también puede verse como la inversa de una puerta AND . NOR es una operación funcionalmente completa : las puertas NOR se pueden combinar para generar cualquier otra función lógica. Comparte esta propiedad con la puerta NAND . Por el contrario, el operador OR es monótono ya que sólo puede cambiar de BAJO a ALTO pero no al revés.

En la mayoría de las implementaciones de circuitos, aunque no en todas, la negación es gratuita, incluidas CMOS y TTL . En tales familias lógicas, OR es la operación más complicada; puede utilizar un NOR seguido de un NOT. Una excepción importante son algunas formas de la familia de la lógica dominó .

Hay tres símbolos para las puertas NOR: el símbolo americano (ANSI o 'militar') y el símbolo IEC ('europeo' o 'rectangular'), así como el símbolo DIN en desuso. Para obtener más información, consulte Símbolos de puerta lógica . El símbolo ANSI para la puerta NOR es una puerta OR estándar con una burbuja de inversión conectada. La burbuja indica que la función de la puerta o se ha invertido.

Las puertas NOR son puertas lógicas básicas y, como tales, se reconocen en los circuitos integrados TTL y CMOS . El IC CMOS estándar de la serie 4000 es el 4001, que incluye cuatro puertas NOR independientes de dos entradas. El diagrama de distribución de pines es el siguiente:

Estos dispositivos están disponibles en la mayoría de los fabricantes de semiconductores, como Fairchild Semiconductor , Philips o Texas Instruments . Por lo general, están disponibles en formato DIP y SOIC de orificio pasante . Las hojas de datos están disponibles en la mayoría de las bases de datos .

En las populares familias lógicas CMOS y TTL , están disponibles puertas NOR con hasta 8 entradas:

En las familias RTL y ECL más antiguas , las puertas NOR eran eficientes y se usaban con mayor frecuencia.

Los diagramas anteriores muestran la construcción de una puerta NOR de 2 entradas utilizando circuitos lógicos NMOS . Si cualquiera de las entradas está en nivel alto, el MOSFET de canal N correspondiente se activa y la salida se reduce; de lo contrario, la salida se eleva a través de la resistencia pull-up .

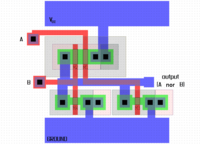

El siguiente diagrama muestra una puerta NOR de 2 entradas que utiliza tecnología CMOS . Los diodos y resistencias de las entradas sirven para proteger los componentes CMOS de daños debidos a descargas electrostáticas (ESD) y no desempeñan ningún papel en el funcionamiento lógico del circuito.

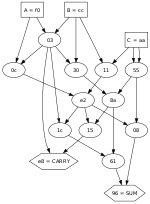

La puerta NOR tiene la propiedad de integridad funcional , que comparte con la puerta NAND. Es decir, cualquier otra función lógica (Y, O, etc.) se puede implementar utilizando únicamente puertas NOR. [1] Se puede crear un procesador completo utilizando únicamente puertas NOR. La computadora de guía Apollo original utilizó 4.100 circuitos integrados (IC), cada uno de los cuales contenía solo dos puertas NOR de 3 entradas. [2]

Como las puertas NAND también son funcionalmente completas, si no hay puertas NOR específicas disponibles, se puede crear una a partir de puertas NAND utilizando lógica NAND . [1]