Colector abierto , drenaje abierto , emisor abierto y código abierto se refieren a configuraciones de pines de salida de circuito integrado (IC) que procesan la función interna del IC a través de un transistor con un terminal expuesto que está internamente desconectado (es decir, "abierto"). Uno de los rieles internos de alto o bajo voltaje del IC generalmente se conecta a otro terminal de ese transistor. Cuando el transistor está apagado, la salida se desconecta internamente de cualquier riel de alimentación interno, un estado llamado "alta impedancia" ( Hi-Z ). Por lo tanto, las configuraciones de salidas abiertas difieren de las salidas push-pull , que utilizan un par de transistores para generar un voltaje o corriente específica .

Estas configuraciones de salidas abiertas se utilizan a menudo para aplicaciones digitales cuando el transistor actúa como un interruptor , para permitir la conversión de nivel lógico, conexiones lógicas por cable y uso compartido de líneas. Por lo general, se requieren resistencias pull-up/down externas para configurar la salida durante el estado Hi-Z a un voltaje específico. Las aplicaciones analógicas incluyen ponderación analógica, suma, limitación y convertidores de digital a analógico .

El NPN BJT ( transistor de unión bipolar tipo n ) y el nMOS ( transistor de efecto de campo semiconductor de óxido metálico tipo n ) tienen mayor conductancia que sus parientes PNP y pMOS, por lo que pueden usarse más comúnmente para estas salidas. Las salidas abiertas que utilizan transistores PNP y pMOS utilizarán el riel de voltaje interno opuesto utilizado por los transistores NPN y nMOS.

Una salida de colector abierto procesa la salida de un circuito integrado a través de la base de un transistor de unión bipolar interno (BJT), cuyo colector está expuesto como pin de salida externo .

Para las salidas de colector abierto NPN, el emisor del transistor NPN está conectado internamente a tierra, [1] por lo que el colector abierto NPN forma internamente una conexión de cortocircuito (técnicamente de baja impedancia o "baja Z") al bajo voltaje ( que podría ser tierra ) cuando el transistor está encendido , o un circuito abierto (técnicamente de alta impedancia o "hi-Z") cuando el transistor está apagado. La salida generalmente está conectada a una resistencia pull-up externa , que lleva el voltaje de salida al voltaje de suministro de la resistencia cuando el transistor está apagado.

Para las salidas de colector abierto PNP, el emisor del transistor PNP está conectado internamente al riel de voltaje positivo , por lo que el colector genera un voltaje alto cuando el transistor está encendido o es de alta Z cuando está apagado. A esto a veces se le llama "colector abierto, conduce alto".

La salida del emisor abierto expone el emisor como salida. [2]

Para una salida de emisor abierto NPN, el colector está conectado al riel de voltaje positivo , por lo que el emisor emite un voltaje alto cuando el transistor está encendido y es de alta Z cuando está apagado.

Para una salida de emisor abierto PNP, el colector está conectado al suministro de bajo voltaje, por lo que el emisor emite un voltaje bajo cuando el transistor está encendido y es alto-Z cuando está apagado.

La salida de drenaje abierto utiliza un transistor MOS (MOSFET) en lugar de BJT y expone el drenaje del MOSFET como salida. [1] : 488 y siguientes

Una salida de drenaje abierto nMOS se conecta a tierra cuando se aplica un voltaje alto a la puerta del MOSFET, o presenta una impedancia alta cuando se aplica un voltaje bajo a la puerta. El voltaje en este estado de alta impedancia sería flotante (indefinido) porque el MOSFET no es conductor, razón por la cual las salidas de drenaje abierto nMOS requieren una resistencia pull-up conectada a un riel de voltaje positivo para producir un voltaje de salida alto.

Los dispositivos microelectrónicos que utilizan salida de drenaje abierto nMOS pueden proporcionar una resistencia pull-up interna "débil" (de alta resistencia, a menudo del orden de 100 kΩ) para conectar el terminal en cuestión a la fuente de alimentación positiva del dispositivo de modo que su voltaje de salida no No flota. Estos pull-ups débiles reducen el consumo de energía debido a su menor calentamiento óhmico y posiblemente evitan la necesidad de un pull-up externo. Los pullups externos pueden ser "más fuertes" (menor resistencia, quizás 3 kΩ) para reducir los tiempos de subida de la señal (como con I²C ) o para minimizar el ruido (como en las entradas RESET del sistema ).

Los microcontroladores modernos pueden permitir programar pines de salida particulares para usar drenaje abierto en lugar de salida push-pull , la fuerza del pull-up interno y permitir deshabilitar los pullups internos cuando no se desee. [3]

Para el drenaje abierto pMOS, la salida se conecta al riel de alimentación positivo cuando el transistor está encendido y es alta Z cuando está apagado. A esto a veces se le llama "drenaje abierto, eleva el nivel".

La salida de código abierto expone la fuente del MOSFET como salida.

Para una salida de código abierto nMOS, el drenaje está conectado internamente al riel de voltaje positivo, por lo que la fuente genera un voltaje alto cuando el transistor está encendido y es de alta Z cuando está apagado.

Para una salida de código abierto pMOS, el drenaje está conectado internamente al riel de bajo voltaje, por lo que la salida se conecta al riel de bajo voltaje cuando el transistor está encendido, o es de alta Z cuando está apagado.

Las configuraciones que se conectan internamente a un alto voltaje son controladores fuente. [4] Las configuraciones que se conectan internamente a un voltaje bajo son controladores disipadores. [5]

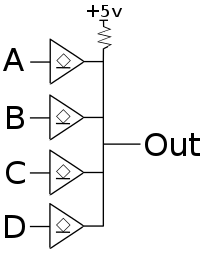

La salida abierta se indica en los esquemas con estos símbolos IEEE : [7]

Nota: esta sección trata principalmente de los colectores abiertos npn; sin embargo, el drenaje abierto nMOS generalmente también se aplica.

Debido a que la resistencia pull-up es externa y no necesita conectarse al voltaje de suministro del chip, en su lugar se puede usar un voltaje más bajo o más alto que el voltaje de suministro del chip (siempre que no exceda la clasificación máxima absoluta de salida del chip). . Por lo tanto, a veces se utilizan salidas abiertas para interconectar diferentes familias de dispositivos que tienen diferentes niveles de voltaje operativo. El transistor de colector abierto puede dimensionarse para soportar un voltaje más alto que el voltaje de suministro del chip. Esta técnica se utiliza comúnmente en circuitos lógicos que funcionan a 5 V o menos para accionar dispositivos de voltaje más alto, como motores eléctricos , LED en serie , [8] relés de 12 V , pantallas fluorescentes de vacío de 50 V o tubos Nixie que requieren más de 100 V.

Otra ventaja es que se puede conectar más de una salida de colector abierto a una sola línea. Si todas las salidas de colector abierto conectadas a una línea están apagadas (es decir, en el estado de alta impedancia), la resistencia pull-up será el único dispositivo que establecerá el voltaje de la línea y elevará el voltaje de la línea. Pero si una o más salidas de colector abierto conectadas a la línea están encendidas (es decir, conduciendo a tierra), dado que cualquiera de ellas es lo suficientemente fuerte como para superar la capacidad limitada de la resistencia pull-up para mantener el voltaje alto, el voltaje de la línea será en cambio bajado. Esta conexión lógica por cable tiene varios usos.

Al unir la salida de varios colectores abiertos y conectarlos a una resistencia pull-up, la línea común se convierte en un Y cableado en lógica alta activa . La salida será alta (verdadera) solo cuando todas las puertas estén en el estado de alta impedancia y será baja (falsa) en caso contrario, como el AND booleano. Cuando se trata como lógica activa-baja, esto se comporta como booleano OR, ya que la salida es baja (verdadera) cuando cualquier entrada es baja. Ver: Lógica transistor-transistor § Lógica cableada de colector abierto .

La línea compartida se utiliza para interrupciones y buses (como I²C o 1-Wire ). La salida de colector abierto permite que un dispositivo activo conduzca la línea compartida sin interferencia de los otros dispositivos inactivos. Si en su lugar se utilizara por error la salida push-pull , el dispositivo activo que intenta establecer el voltaje de línea bajo competiría con los otros dispositivos que intentan establecer el voltaje de línea alto, lo que resultaría en una salida y calor impredecibles.

Los dispositivos SCSI -1 utilizan un colector abierto para la señalización eléctrica. [9] SCSI-2 y SCSI-3 pueden utilizar EIA-485 .

Las salidas de colector abierto también pueden ser útiles para ponderación analógica, suma, limitación, convertidores de digital a analógico , etc., pero dichas aplicaciones no se analizan aquí.

Un problema de estos dispositivos de colector abierto y similares con una resistencia pull-up es que la resistencia consume energía constantemente mientras la salida es baja. Las velocidades de funcionamiento más altas requieren valores de resistencia más bajos para un pull-up más rápido, lo que consume aún más energía.

Además, cuando se acciona una carga, la corriente a través de la resistencia pull-up reduce el alto voltaje de salida en una caída de voltaje igual a la corriente multiplicada por la resistencia, de acuerdo con la ley de Ohm .

Los controladores de drenaje pseudo abierto ( POD ) tienen una fuerte fuerza de tracción hacia abajo pero una fuerza de tracción más débil. El propósito es reducir la demanda general de energía en comparación con el uso de un fuerte pull-up y un fuerte pull-down. [10] En comparación, un controlador de drenaje abierto puro no tiene fuerza de pull-up excepto por la corriente de fuga: toda la acción de pull-up se realiza en la resistencia de terminación externa. Es por eso que aquí se debe usar el término "pseudo": hay algo de pull-up en el lado del conductor cuando la salida está en estado alto, la fuerza de pull-up restante se proporciona al terminar en paralelo el receptor en el otro extremo para el ALTO voltaje, a menudo usando un terminador en matriz conmutable en lugar de una resistencia separada.

JEDEC estandarizó los términos POD15, [11] POD125, [12] POD135, [13] y POD12 [14] para voltajes de suministro de interfaz de 1,5 V, 1,25 V, 1,35 V y 1,2 V, respectivamente.

La memoria DDR4 utiliza controladores POD12 pero con la misma potencia del controlador (34 Ω/48 Ω) para pull-down (R onPd ) y pull-up (R onPu ). El término POD en DDR4 se refiere únicamente al tipo de terminación que es solo pull-up paralelo sin la terminación pull-down en el otro extremo. [ se necesita aclaración ] El punto de referencia (V REF ) para la entrada no es la mitad del suministro como lo era en DDR3 y puede ser mayor. A finales de 2011 se publicó una comparación [15] de los esquemas de terminación DDR3 y DDR4 en términos de inclinación, apertura ocular y consumo de energía. [¿ Relevante? ]