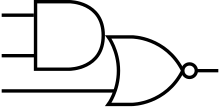

La lógica AND-OR-invertida (AOI) y las puertas AOI son funciones lógicas compuestas (o complejas) de dos niveles construidas a partir de la combinación de una o más puertas AND seguidas de una puerta NOR (equivalente a una puerta OR a través de una puerta Inversora , que es la parte "OI" de "AOI"). La construcción de celdas AOI es particularmente eficiente utilizando tecnología CMOS , donde la cantidad total de puertas de transistores se puede comparar con la misma construcción utilizando lógica NAND o lógica NOR . El complemento de la lógica AOI es la lógica OR-AND-invertida (OAI), donde las puertas OR preceden a una puerta NAND. [1]

La mayoría de las optimizaciones lógicas dan como resultado una expresión lógica de suma de productos o de producto de sumas. [2]

AOI se utiliza para la suma de productos, las variables se combinan mediante AND para formar mintérminos que luego se invierten mediante OR, como:

Las puertas AOI realizan una o más operaciones AND seguidas de una operación OR y luego una inversión.

La puerta AOI 2-1 se puede representar mediante la siguiente ecuación booleana y tabla de verdad :

Se encuentran ejemplos del mundo real de una puerta AOI 2-2 en los circuitos integrados lógicos CD4085B, SN74LS51, SN5450 (ver más abajo). [3] [4] [6]

La puerta AOI 2-2 se puede representar mediante la siguiente ecuación booleana y tabla de verdad :

Se encuentran ejemplos del mundo real de una puerta AOI 3-3 en el CI lógico SN74LS51 (ver más abajo). [4]

La puerta AOI 3-3 se puede representar mediante la siguiente ecuación booleana y tabla de verdad :

Su tabla lógica tendría 64 entradas, pero no se muestra.

Se encuentran ejemplos del mundo real de una puerta AOI 4-4 en el CI lógico CD4048B (ver más abajo). [5]

La puerta AOI 4-4 se puede representar mediante la siguiente ecuación booleana y tabla de verdad :

Su tabla lógica tendría 256 entradas, pero no se muestra.

Es posible crear puertas compuestas de varios niveles, que combinan la lógica de las puertas AND-OR-Invert con las puertas OR-AND-Invert . [7] A continuación se muestra un ejemplo. Las partes que implementan la misma lógica se han colocado en cuadros con el mismo color.

Las puertas AND-OR-invert (AOI) y OAI se pueden implementar fácilmente en circuitos CMOS . Las puertas AOI tienen la ventaja particular de que la cantidad total de transistores (o puertas) es menor que si las funciones AND, NOT y OR se implementaran por separado. Esto da como resultado mayor velocidad, menor consumo de energía, menor área y un costo de fabricación potencialmente menor. Por ejemplo, una puerta AOI 2-1 se puede construir con 6 transistores en CMOS, en comparación con 10 transistores utilizando una puerta NAND de 2 entradas (4 transistores), un inversor (2 transistores) y una puerta NOR de 2 entradas (4 transistores).

En la lógica NMOS , la mitad inferior del circuito CMOS se utiliza en combinación con un dispositivo de carga o un transistor pull-up (normalmente una carga de agotamiento o una carga dinámica ).

Las puertas AOI son igualmente eficientes en la lógica transistor-transistor (TTL).

Familia lógica de la serie CMOS 4000 :

Familia lógica de la serie TTL 7400 : (en décadas pasadas, había varias piezas AOI disponibles en la familia 7400, pero actualmente la mayoría están obsoletas (ya no se fabrican))