El Pentium Pro es un microprocesador x86 de sexta generación desarrollado y fabricado por Intel y presentado el 1 de noviembre de 1995. [1] : D-2 Introdujo la microarquitectura P6 (a veces denominada i686) y originalmente estaba destinado a reemplazar al Pentium original en una gama completa de aplicaciones. Más tarde, se redujo a un papel más estrecho como procesador de escritorio de alta gama y servidor. El Pentium Pro también se utilizó en supercomputadoras , especialmente ASCI Red , que usaba dos CPU Pentium Pro en cada nodo de computación y fue la primera computadora en alcanzar más de un teraFLOPS en 1996, ocupando el puesto número uno en la lista TOP500 de 1997 a 2000. [2]

Mientras que el Pentium y el Pentium MMX tenían 3,1 y 4,5 millones de transistores , respectivamente, el Pentium Pro contenía 5,5 millones de transistores. [3] : 12 Era capaz de configuraciones de dos y cuatro procesadores y solo venía en un factor de forma, el relativamente grande y rectangular Socket 8. El Pentium Pro fue reemplazado por el Pentium II Xeon en 1998.

El arquitecto principal de Pentium Pro fue Fred Pollack , quien se especializó en superescalaridad y también había trabajado como ingeniero principal del Intel iAPX 432. [ 4]

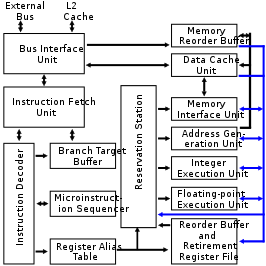

El Pentium Pro incorporó una nueva microarquitectura , diferente de la microarquitectura P5 del Pentium . Tiene una arquitectura superpipelined desacoplada de 14 etapas que usaba un pool de instrucciones. El Pentium Pro ( P6 ) implementó muchas diferencias arquitectónicas radicales que reflejaban otros diseños x86 contemporáneos como el NexGen Nx586 y Cyrix 6x86 . La tubería del Pentium Pro tenía etapas de decodificación adicionales para traducir dinámicamente las instrucciones IA-32 en secuencias de microoperaciones almacenadas en búfer que luego podían analizarse, reordenarse y renombrarse para detectar operaciones paralelizables que pudieran emitirse a más de una unidad de ejecución a la vez. Por lo tanto, el Pentium Pro presentaba ejecución fuera de orden , incluida la ejecución especulativa mediante el cambio de nombre de registros . También tenía un bus de direcciones de 36 bits más amplio , utilizable por Physical Address Extension (PAE), lo que le permitía acceder a hasta 64 GB de memoria.

El Pentium Pro tiene una caché de instrucciones de 8 KB, de la que se obtienen hasta 16 bytes en cada ciclo y se envían a los decodificadores de instrucciones . Hay tres decodificadores de instrucciones. Los decodificadores son desiguales en capacidad: solo uno puede decodificar cualquier instrucción x86, mientras que los otros dos solo pueden decodificar instrucciones x86 simples. Esto restringe la capacidad del Pentium Pro para decodificar múltiples instrucciones simultáneamente, lo que limita la ejecución superescalar. Las instrucciones x86 se decodifican en microoperaciones de 118 bits (microops). Las microoperaciones son similares a las de un ordenador con conjunto de instrucciones reducido (RISC); es decir, codifican una operación, dos fuentes y un destino. El decodificador general puede generar hasta cuatro microoperaciones por ciclo, mientras que los decodificadores simples pueden generar una microoperación cada uno por ciclo. Por lo tanto, las instrucciones x86 que operan en la memoria (por ejemplo, agregar este registro a esta ubicación en la memoria) solo pueden ser procesadas por el decodificador general, ya que esta operación requiere un mínimo de tres microoperaciones. De la misma manera, los decodificadores simples están limitados a instrucciones que pueden traducirse en una microoperación. Las instrucciones que requieren más de cuatro microoperaciones se traducen con la ayuda de un secuenciador, que genera las microoperaciones requeridas durante varios ciclos de reloj. El Pentium Pro fue el primer procesador de la familia x86 que admitió microcódigo actualizable bajo el control del BIOS y/o del sistema operativo (OS). [5]

Las microoperaciones salen del búfer de reordenamiento (ROB) y entran en una estación de reserva (RS), donde esperan ser enviadas a las unidades de ejecución. En cada ciclo de reloj, se pueden enviar hasta cinco microoperaciones a cinco unidades de ejecución. El Pentium Pro tiene un total de seis unidades de ejecución: dos unidades enteras, una unidad de punto flotante (FPU), una unidad de carga, una unidad de dirección de almacenamiento y una unidad de datos de almacenamiento. [6] Una de las unidades enteras comparte los mismos puertos que la FPU y, por lo tanto, el Pentium Pro solo puede enviar una microoperación entera y una microoperación de punto flotante, o dos microoperaciones enteras por ciclo, además de las microoperaciones para las otras tres unidades de ejecución. De las dos unidades enteras, solo la que comparte la ruta con la FPU en el puerto 0 tiene el complemento completo de funciones, como un desplazador de barril , un multiplicador, un divisor y soporte para instrucciones LEA. La segunda unidad entera, que está conectada al puerto 1, no tiene estas funciones y está limitada a operaciones simples como sumar, restar y el cálculo de direcciones de destino de rama. [6]

La FPU ejecuta operaciones de punto flotante. La suma y la multiplicación se procesan en pipeline y tienen una latencia de tres y cinco ciclos, respectivamente. La división y la raíz cuadrada no se procesan en pipeline y se ejecutan en unidades separadas que comparten los puertos de la FPU. La división y la raíz cuadrada tienen una latencia de 18-36 y 29-69 ciclos, respectivamente. El número más pequeño es para números de punto flotante de precisión simple (32 bits) y el más grande para números de precisión extendida (80 bits). La división y la raíz cuadrada pueden operar simultáneamente con sumas y multiplicaciones, lo que evita que se ejecuten solo cuando el resultado debe almacenarse en el ROB.

Después de que se lanzó el microprocesador, se descubrió un error en la unidad de punto flotante , comúnmente llamado "error de FPU de Pentium Pro y Pentium II" y por Intel como "error de bandera". El error ocurre bajo ciertas circunstancias durante la conversión de punto flotante a entero cuando el número de punto flotante no cabe en el formato entero más pequeño, lo que hace que la FPU se desvíe de su comportamiento documentado. El error se considera menor y ocurre bajo circunstancias tan especiales que muy pocos programas de software, si es que hay alguno, se ven afectados.

La microarquitectura Pentium Pro P6 fue utilizada de una forma u otra por Intel durante más de una década. La línea de desarrollo se ampliaría desde su inicio a 150 MHz, hasta 1,4 GHz con el Pentium III "Tualatin" . Las diversas características del diseño continuarían después en el núcleo derivado llamado " Banias " en Pentium M e Intel Core ( Yonah ), que a su vez evolucionaría hacia la microarquitectura Core ( procesador Core 2 ) en 2006 y en adelante. [7]

El Pentium Pro (P6) introdujo nuevas instrucciones en la gama Intel; las instrucciones CMOVxx ('movimiento condicional') pueden mover un valor que es el contenido de un registro o ubicación de memoria a otro registro o no, de acuerdo con alguna condición lógica de predicado xx en el registro de indicadores, siendo xx un código de predicado de indicadores como el dado en la condición para instrucciones de salto condicional. Por ejemplo, CMOVNE mueve un valor especificado a un registro o no dependiendo de si la condición NE (no igual) es verdadera en el registro de indicadores, es decir, Z indicador = 0. Esto permite la evaluación de operaciones if-then-else y, por ejemplo, la operación ? : en C. Estas instrucciones dan un impulso al rendimiento al permitir evitar instrucciones costosas de salto y bifurcación. En CMOVxx destreg1, source_operand2, por ejemplo, el primer operando es el registro de destino, el segundo el registro de origen o ubicación de memoria. El segundo operando, lamentablemente, no puede ser un valor inmediato (constante en línea) y dicha constante tendría que colocarse primero en un registro. El código de predicado xx puede tomar el rango completo de valores permitido en las ramas condicionales.

Un segundo avance fue la documentación de la instrucción ilegal UD2. Este código de operación está reservado y se garantiza que provocará una excepción de instrucción ilegal en el P6 y todos los procesadores posteriores. Esto permite a los desarrolladores bloquear fácilmente el programa actual de forma que no se produzcan errores en el futuro cuando el software detecte un error.

A pesar de ser avanzado para la época, la arquitectura de renombramiento de registros fuera de orden del Pentium Pro tenía problemas para ejecutar código de 16 bits y código mixto ( 8 bits con 16 bits (8/16), o 16 bits con 32 bits (16/32), ya que el uso de registros parciales causaba un vaciado frecuente de la tubería. [8] El uso específico de registros parciales era entonces una optimización de rendimiento común, ya que no incurría en ninguna penalización de rendimiento en los procesadores Intel anteriores a P6; además, los sistemas operativos dominantes en el momento del lanzamiento del Pentium Pro eran DOS de 16 bits y Windows 3.1x y Windows 95 mixtos de 16/32 bits (aunque este último requiere una CPU 80386 de 32 bits como mínimo, gran parte de su código sigue siendo de 16 bits por razones de rendimiento, como la biblioteca de vínculo dinámico USER de Windows de 16 bits , user.exe ). Esto, junto con el alto costo de los sistemas Pentium Pro, condujo a ventas tibias entre los usuarios de PC. Los compradores de la época no tenían idea de lo que era. Para utilizar plenamente la microarquitectura P6 del Pentium Pro , se necesitaba un sistema operativo de 32 bits, como Windows NT , Linux , Unix u OS/2 . Los problemas de rendimiento del código heredado fueron mitigados en parte por Intel con el Pentium II.

En comparación con los microprocesadores RISC, el Pentium Pro, cuando se presentó, superó ligeramente a los microprocesadores RISC más rápidos en rendimiento de números enteros al ejecutar el punto de referencia SPECint95 , [9] : 2 pero el rendimiento de punto flotante fue significativamente menor, la mitad del de algunos microprocesadores RISC. [9] : 3 La ventaja del Pentium Pro en rendimiento de números enteros desapareció rápidamente, superado primero por el MIPS Technologies R10000 en enero de 1996, y luego por la variante EV56 de Digital Equipment Corporation del Alpha 21164. [10 ]

Los revisores rápidamente notaron que las escrituras muy lentas en la memoria de video eran el punto débil de la plataforma P6, con un rendimiento aquí tan bajo como el 10% de un sistema Pentium con frecuencia de reloj idéntica en pruebas de referencia como VIDSPEED. Los métodos para evitar esto incluían configurar el dibujo VESA en la memoria del sistema en lugar de la memoria de video en juegos como Quake , [11] y más tarde surgieron utilidades como FASTVID, que podían duplicar el rendimiento en ciertos juegos al habilitar las características de combinación de escritura de la CPU. [12] [13] Los registros de rango de tipo de memoria (MTRR) son configurados automáticamente por los controladores de video de Windows a partir de 1997, y desde allí, el subsistema de caché/memoria mejorado y el rendimiento de la FPU hicieron que superara al Pentium reloj por reloj en los juegos 3D emergentes de mediados y fines de la década de 1990, particularmente cuando se usaba Windows NT 4.0 . Sin embargo, su falta de implementación de MMX reduce el rendimiento en aplicaciones multimedia que hacían uso de esas instrucciones.

Probablemente la adición más notable del Pentium Pro fue su caché L2 en el paquete , que variaba de 256 KB en su introducción a 1 MB en 1997. En ese momento, la tecnología de fabricación no permitía de manera factible integrar una gran caché L2 en el núcleo del procesador. En su lugar, Intel colocó el chip L2 por separado en el paquete, lo que aún le permitía funcionar a la misma velocidad de reloj que el núcleo de la CPU. Además, a diferencia de la mayoría de los esquemas de caché basados en la placa base que compartían el bus principal del sistema con la CPU, la caché del Pentium Pro tenía su propio bus posterior (llamado bus independiente dual por Intel). Debido a esto, la CPU podía leer la memoria principal y la caché simultáneamente, lo que reducía en gran medida un cuello de botella tradicional. [14] La caché también era "sin bloqueo", lo que significa que el procesador podía emitir más de una solicitud de caché a la vez (hasta 4), lo que reducía las penalizaciones por falla de caché. (Este es un ejemplo de MLP, Memory Level Parallelism ). Estas propiedades se combinaron para producir una caché L2 que era inmensamente más rápida que las cachés basadas en la placa base de los procesadores más antiguos. Esta caché por sí sola le dio a la CPU una ventaja en el rendimiento de entrada/salida sobre las CPU x86 más antiguas . En configuraciones multiprocesador, la caché integrada de Pentium Pro disparó el rendimiento en comparación con las arquitecturas en las que cada CPU compartía una caché central.

Sin embargo, esta caché L2 mucho más rápida trajo consigo algunas complicaciones. La disposición de la "caché en el paquete" del Pentium Pro era única. El procesador y la caché estaban en matrices separadas en el mismo paquete y conectados estrechamente por un bus de alta velocidad. Las dos o tres matrices tenían que unirse entre sí al principio del proceso de producción, antes de que fuera posible realizar pruebas. Esto significaba que un solo y diminuto defecto en cualquiera de las matrices hacía necesario descartar todo el conjunto, lo que era una de las razones del rendimiento de producción relativamente bajo y el alto coste del Pentium Pro. Todas las versiones del chip eran caras, especialmente las de 1024 KB, ya que requerían dos matrices de caché de 512 KB además de la matriz del procesador.

Las velocidades de reloj del Pentium Pro eran de 150, 166, 180 o 200 MHz con un reloj de bus externo de 60 o 66 MHz. En sus primeras etapas de desarrollo se desarrolló un prototipo de Pentium Pro de 133 MHz, pero nunca se lanzó al mercado. Algunos usuarios optaron por hacer overclocking de sus chips Pentium Pro, y la versión de 200 MHz solía funcionar a 233 MHz, la versión de 180 MHz a 200 MHz y la versión de 150 MHz a 166 MHz. El chip era popular en configuraciones de multiprocesamiento simétrico , y las configuraciones de servidores y estaciones de trabajo con SMP dual y cuádruple eran habituales.

Intel decidió no ofrecer una versión móvil del Pentium Pro original debido a problemas de consumo de energía y de temperatura. [15] Al menos un proveedor vendió una computadora portátil con un Pentium Pro (el 6200TLP de Imperial Computer). [16]

En el esquema "Familia/Modelo/Paso" de Intel, el Pentium Pro es la familia 6, modelo 1, y su código de producto Intel es 80521.

El proceso utilizado para fabricar la matriz del procesador Pentium Pro y su matriz de memoria caché separada cambió, lo que dio lugar a una combinación de procesos utilizados en el mismo paquete:

El Pentium Pro (hasta 512 KB de caché) está empaquetado en un módulo multichip cerámico (MCM). El MCM contiene dos cavidades inferiores en las que se encuentran la matriz del microprocesador y la matriz de caché que la acompaña. Las matrices están unidas a un slug térmico, cuya parte superior expuesta ayuda a que el calor de las matrices se transfiera de forma más directa a aparatos de refrigeración como un disipador térmico. Las matrices están conectadas al paquete mediante una conexión por cable convencional. Las cavidades están tapadas con una placa cerámica.

El Pentium Pro con 1 MB de caché utiliza un MCM de plástico. En lugar de dos cavidades, hay una sola, en la que se encuentran los tres chips, unidos al encapsulado en lugar de una barra de calor. Las cavidades están rellenas con epoxi.

El MCM tiene 387 pines, de los cuales aproximadamente la mitad están dispuestos en una matriz de rejilla de pines (PGA) y la otra mitad en una matriz de rejilla de pines intersticial (IPGA). El encapsulado fue diseñado para el Socket 8 .

En 1998, se lanzó el procesador Pentium II OverDrive de 300/333 MHz para Socket 8. Basado en parte de la tecnología utilizada en el Deschutes Pentium II Xeon , presentaba doble L1 y 512 KB de caché L2 de velocidad completa con capacidades MMX , y fue producido por Intel como una opción de actualización directa para los propietarios de sistemas Pentium Pro. Sin embargo, solo admitía multiprocesamiento sin pegamento de dos vías , no de cuatro vías o superior, lo que no lo convertía en una actualización utilizable para sistemas de cuatro procesadores. Estos procesadores Pentium II OverDrive especialmente empaquetados también se utilizaron para actualizar la supercomputadora ASCI Red en 1999. Esto hace que la supercomputadora ASCI Red, la primera computadora en alcanzar la marca de rendimiento de un teraFLOPS con procesadores Pentium Pro duales en 1996, se convierta ahora en la primera computadora en general en superar la marca de rendimiento de dos teraFLOPS con la actualización a procesadores Pentium II OverDrive duales en 1999. ASCI Red continuó utilizando procesadores Pentium II OverDrive duales durante el resto de su vida útil antes de ser desmantelada en 2006.

A medida que las placas base con ranura 1 se hicieron más comunes, varios fabricantes lanzaron adaptadores de ranura (o slocket), como el Tyan M2020, Asus C-P6S1, Tekram P6SL1 y el Abit KP6. Estos zócalos permitían utilizar procesadores Pentium Pro con placas base con ranura 1. Sin embargo, solo unos pocos chipsets admitían estos slotkets, por lo que no se utilizaron de forma generalizada. El chipset Intel 440FX admitía explícitamente tanto procesadores Pentium Pro como Pentium II, sin embargo, el Intel 440BX y los chipsets con ranura 1 posteriores no admitían explícitamente Pentium Pro. Los slotkets finalmente volvieron a ganar popularidad en forma de adaptadores de Socket 370 a Slot 1, cuando Intel introdujo los procesadores Celeron y Pentium III con ranura 370 a fines de la década de 1990. Este tipo de slotkets permitieron menores costos para los constructores de computadoras, especialmente con máquinas de procesador dual, y le dieron a las placas base Slot 1 la capacidad de continuar recibiendo actualizaciones de CPU más allá de las CPU Slot 1 disponibles en ese momento.

El Pentium Pro utilizaba señalización GTL+ en su bus frontal. [21] El Pentium Pro podía utilizarse por sí solo en diseños de hasta cuatro vías. También se construyeron computadoras Pentium Pro de ocho vías, pero estas utilizaban múltiples buses. [22]

El diseño del bus Pentium Pro estuvo influenciado por Futurebus , el bus iAPX 432 de Intel y elementos del bus i960 de Intel . [23] Futurebus había sido pensado como un bus avanzado para reemplazar VMEbus usado con el Motorola 68000 desde finales de los años 1970, pero se estancó en el comité de estandarización durante más de una década si se cuentan todos los giros y vueltas. [23] La iniciativa iAPX 432 de Intel también fue un fracaso comercial, pero en el proceso aprendieron a construir un bus de transacción dividida para soportar un sistema multiprocesador sin caché. El i960 había desarrollado aún más el bus iAPX 432 de transacción dividida para incluir un protocolo de coherencia de caché, terminando con un conjunto de características que recordaba mucho a las ambiciones originales de Futurebus. [23]

El arquitecto principal del i960 fue el especialista en superescalaridad Fred Pollack, que también fue el ingeniero principal del Intel iAPX 432 y el arquitecto principal del chip i686, el Pentium Pro. Sin duda, estaba íntimamente familiarizado con toda esta historia. El Pentium Pro fue diseñado para incluir el bus coherente de caché de transacciones divididas SMP de 4 vías como una característica obligatoria de cada chip producido. [23] Esto también sirvió para negar a la competencia el acceso al zócalo para producir procesadores clonados. [23]

Si bien el Pentium Pro no tuvo éxito como máquina para las masas debido al escaso soporte de 16 bits para Windows 95 y muchos otros sistemas operativos de 16 bits y mixtos de 16/32 bits, sí tuvo un éxito significativo en el espacio de servidores de archivos debido a su diseño de bus integrado avanzado, [23] introduciendo en el mercado de productos básicos muchas características avanzadas que anteriormente solo estaban disponibles en el costoso segmento de estaciones de trabajo.

Pero aunque el rendimiento del chip es superior al esperado y su precio más bajo, los analistas dijeron que su impacto inmediato probablemente no igualaría al de su predecesor, el Pentium.

La supercomputadora ASCI Red de Intel fue la primera computadora de teraflop/s, ocupando el puesto número 1 en la novena lista TOP500 en junio de 1997 con un rendimiento Linpack de 1.068 teraflop/s. [...] Era una máquina masivamente paralela MIMD basada en malla (38 X 32 X 2) que inicialmente constaba de 7264 nodos de cómputo, 1212 gigabytes de memoria distribuida total y 12,5 terabytes de almacenamiento en disco. La encarnación original de esta máquina utilizaba procesadores Intel Pentium Pro, cada uno con una velocidad de reloj de 200 MHz. Estos se actualizaron posteriormente a procesadores Pentium II OverDrive. El sistema se actualizó a un total de 9.632 procesadores Pentium II Over-Drive, cada uno con una velocidad de reloj de 333 MHz.

Había muchas piezas involucradas en este chip, pero el Pentium Pro actual consta de dos chips y también de otros chips de soporte necesarios. Curiosamente, el ingeniero principal del 432 fue el diseñador superestrella Fred Pollack, quien se convirtió en el arquitecto principal del Pentium Pro.

Offenbar hat der PPro einen ladbaren Microcode, for the Board-BIOS dos funciones im Interrupt 15h zum Auslesen and Laden bereithält (näheres im nächsten Update der Interrupt-Liste). Gedacht ist das für Patches, doch wer weiß, welch ungeahnte Möglichkeiten noch darinstecken. Somit hat man es beim PPro in Zukunft nur mit dos Masken-Versionen (für CPU and Cache), sondern auch noch mit der Update-Version des Microcode-BIOS zu tun (zum Beispiel beim aktuellen 200-MHz-'P6S' mit der Kennung SY013: CPU-Paso A0, Caché-Paso B1, BIOS: sA0C05).[Aparentemente el PPro tiene un microcódigo cargable, para el cual el BIOS de la placa proporciona dos funciones en interrupción 15h para lectura y carga (más información en la próxima actualización de la lista de interrupciones). Esto está destinado a parches, pero quién sabe qué posibilidades inimaginables aún existen. En el futuro, por lo tanto, el PPro no solo tendrá que lidiar con dos versiones de máscara (para CPU y caché), sino también con la versión de actualización del microcódigo BIOS (por ejemplo, con el actual 'P6S' de 200 MHz con el identificador SY013: Paso de CPU A0, paso de caché B1, BIOS: sA0C05).]

El linaje P6 desde Pentium Pro hasta Pentium M [...] Una de las características más distintivas de la línea P6 es su estructura de puerto de emisión. (Intel los llama "puertos de despacho", pero por el bien de la coherencia con el resto de mi trabajo, utilizaré los términos "despacho" y "emisión" de forma diferente a Intel). Core utiliza una estructura similar en su núcleo de ejecución, aunque existen algunas diferencias importantes entre la combinación de puerto de emisión y RS de Core y la del P6.

Los chips RISC van por delante de los enteros y los de función fija por detrás