El TMS9900 fue uno de los primeros microprocesadores de 16 bits de un solo chip disponibles comercialmente . [a] Presentado en junio de 1976, implementó la arquitectura de minicomputadora TI-990 de Texas Instruments en un formato de un solo chip, y se utilizó inicialmente para modelos de gama baja de esa línea.

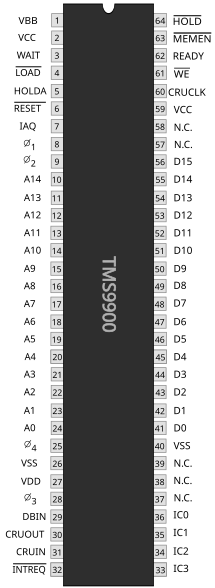

Su formato DIP de 64 pines hizo que su implementación en máquinas más pequeñas fuera más costosa que el formato más común de 40 pines, y tuvo relativamente pocos éxitos de diseño fuera del uso propio de TI. Entre esos usos se encontraban sus computadoras hogareñas TI-99/4 y TI-99/4A , que finalmente vendieron alrededor de 2,8 millones de unidades.

Las implementaciones de microcomputadoras en chip del 9900 en paquetes de 40 pines incluyeron el TMS9940, el TMS9980/81 y el TMS9995. El TMS99105/10 fue la última versión del 9900 en 1981 e incorporó características del miniordenador 990/10 de TI. [1]

A mediados de la década de 1980, el campo de las microcomputadoras estaba pasando a sistemas de 16 bits como el Intel 8088 y diseños más nuevos de 16/32 bits como el Motorola 68000. Sin un futuro evidente para el chip, TI centró su atención en procesadores para propósitos especiales como el Texas Instruments TMS320 , presentado en 1983.

El TMS9900 fue diseñado como una versión de un solo chip de la serie de minicomputadoras TI 990 , de manera similar a como el Intersil 6100 era un PDP-8 de un solo chip (12 bits), y el Fairchild 9440 y el Data General mN601 eran versiones de un solo chip del Nova de Data General . A diferencia de los microprocesadores de 16 bits de múltiples chips, como el National Semiconductor IMP-16 o el DEC LSI-11 , algunos de los cuales fueron anteriores al TMS9900, el 9900 era un microprocesador autónomo de 16 bits de un solo chip.

Las raíces de la minicomputadora TMS9900 dan lugar a una serie de características arquitectónicas que no se encuentran comúnmente en diseños que comenzaron desde una hoja en blanco. Entre ellas, destaca el uso de registros de procesador en la TMS9900 que se asignan a la memoria principal . Esto permite un cambio rápido de contexto , que se puede lograr modificando un solo registro, el puntero de espacio de trabajo, para que apunte a la primera entrada en una lista de valores de registro. Los diseños más tradicionales requerirían que todo el conjunto de registros internos se almacenara en la memoria o en la pila.

La desventaja de este enfoque es que acceder a estos registros requiere más tiempo. En una implementación de minicomputadora con memoria rápida, el efecto es relativamente pequeño y la ventaja en un entorno de tiempo real o multitarea es significativa, ya que los cambios de contexto son comunes. En otras funciones, como las microcomputadoras de un solo usuario, esta compensación puede no valer la pena. Las implementaciones de 40 pines del 9900 incluían 128 o 256 bytes de RAM rápida incorporada para registros.

TI utilizó la misma arquitectura en las distintas divisiones para lograr sinergia corporativa: "una empresa, una arquitectura informática". A finales de los años 70, Walden C. Rhines hizo una presentación del TMS99110, que entonces tenía el nombre en código "Alpha", [2] a un grupo de IBM que estaba desarrollando un ordenador personal. "Hasta 1981 no sabríamos exactamente lo que habíamos perdido", porque IBM eligió el Intel 8088 para el IBM PC , recordó. Un factor fue la falta de una hoja de ruta para acceder a más de 64 K de memoria lógica. La familia 9900 podía ampliar su espacio de direcciones a 16 MiB sólo mediante mapeo de páginas; el 9900 podía direccionar 256 K mediante segmentos.

Después de abandonar el mercado de computadoras personales con productos como el TI-99/4A , la división de microprocesadores de la compañía finalmente cambió su enfoque a la serie de procesadores de propósito especial TMS320 . [3]

El TMS9900 tiene tres registros internos de 16 bits : contador de programa (PC), registro de estado (ST) y registro de puntero de espacio de trabajo (WP). [4] El registro WP apunta a una dirección base en la RAM externa donde se guardan los 16 registros de usuario de propósito general del procesador (cada uno de 16 bits de ancho). Esta arquitectura permite un cambio rápido de contexto ; por ejemplo, cuando se ingresa una subrutina , solo se necesita cambiar el registro de espacio de trabajo en lugar de requerir que los registros se guarden individualmente. Los bits se numeran de manera poco convencional y el bit más significativo es 0.

Las direcciones se refieren a bytes con la convención de ordenación big endian . El TMS9900 es una máquina clásica de 16 bits con un espacio de direcciones de 216 bytes (65.536 bytes o 32.768 palabras).

No existe un registro de puntero de pila dedicado. En su lugar, existen instrucciones de bifurcación que guardan el contador del programa en un registro (Branch and Link) o cambian el contexto del registro (Branch and Link Workspace o XOP). Los 16 vectores de interrupción de hardware y los 16 vectores de interrupción de software constan cada uno de un par de valores PC y WP, por lo que el cambio de contexto de registro también lo realiza automáticamente una interrupción. Las pilas se pueden implementar sobre cualquiera de estos mecanismos. [5]

El TMS9900 tiene 69 instrucciones de una, dos o tres palabras de longitud y siempre alineadas en la memoria. El conjunto de instrucciones es bastante ortogonal , lo que significa que, con pocas excepciones, las instrucciones pueden utilizar todos los métodos de acceso a los operandos (modos de direccionamiento).

Los modos de direccionamiento incluyen Inmediato (operando en instrucción), Directo o "Simbólico" (dirección del operando en instrucción), Registro (operando en registro de espacio de trabajo), Registro Indirecto (dirección del operando en registro de espacio de trabajo) con o sin incremento automático, Indexado (dirección del operando en instrucción indexada con el contenido del registro de espacio de trabajo) y Contador de programa relativo.

Las instrucciones de doble operando más importantes (sumar, restar, comparar, mover, etc.) contienen un modo de direccionamiento de 2 bits y campos de selección de registro de 4 bits para los operandos de origen y destino. En el código de operación, el modo "simbólico" se representa como modo indexado con el campo de registro establecido en 0, por lo tanto, el registro de espacio de trabajo 0 (WR0) no se puede utilizar en modo indexado. En instrucciones de doble operando menos utilizadas, como XOR, el operando de destino debe ser un registro de espacio de trabajo (o un par de registros de espacio de trabajo en el caso de instrucciones de multiplicación y división).

El control de flujo se facilita mediante un grupo de una instrucción de salto incondicional y doce instrucciones de salto condicionales. Los objetivos de salto son relativos a la PC con un desplazamiento de direcciones de palabra de -128 a +127.

Para las llamadas a subrutinas, la instrucción Branch and Load Workspace Pointer (BLWP) carga nuevos valores de WP y PC, luego guarda los valores de WP, PC y ST en los (nuevos) registros 13, 14 y 15 respectivamente. Al final de la subrutina, la instrucción Return Workspace Pointer (RTWP) los restaura en orden inverso. Con BLWP/RTWP, es posible anidar llamadas a subrutinas a pesar de la ausencia de una pila; sin embargo, el programador debe asignar el espacio de trabajo de registro apropiado explícitamente.

El conjunto de instrucciones también contiene un código de operación de bifurcación y enlace (BL) que solo guarda PC en el registro 11 sin cambiar WP. En este caso, una instrucción de bifurcación (B) que utiliza WR11 como dirección de destino puede servir como código de operación de retorno, pero las subrutinas de tipo BL no se pueden anidar sin que el programador realice acciones para guardar la dirección de retorno.

El TMS9900 admite una instrucción de ejecución "X" (eXecute). Esta instrucción ejecuta la instrucción en un registro. Se puede utilizar para depurar (como una instrucción de punto de interrupción ), para crear tablas de códigos de operación indexados como las que se utilizan en los intérpretes de código de bytes y también se puede utilizar para ejecutar una instrucción de E/S crítica en el tiempo durante una interrupción. Un ejemplo de su utilidad se muestra en el código siguiente, donde se atiende una interrupción de una manera muy encapsulada que, de lo contrario, requeriría muchas más instrucciones.

;************************************;; ESTA INTERRUPCIÓN SIMULA EL CONTROL DMA; ORGANIZADO DE LA SIGUIENTE MANERA:;; R9 MANTIENE EL COMANDO ACTUAL, POR EJEMPLO; IOREAD(34B8H): STCR *R8+,BYTEWIDE ;LECTURA DE DATOS FDC DE ANCHO BYTE; IOWRITE(30B8H):LDCR *R8+,BYTEWIDE ;ESCRIBIR DATOS FDC DE ANCHO BYTE; R8 CONTIENE LA DIRECCIÓN DMA ACTUAL.; R12 CONTIENE EL PUERTO IO ACTUAL - DATREG;************************************INTDRQ X R9 ;PUEDE SER DE LECTURA o DE ESCRITURA Regreso al futuro

Este fragmento de código común durante la interrupción podría ser utilizado tanto por comandos de lectura como de escritura de E/S. Se podrían emplear métodos similares en cualquier método de depuración que se desee utilizar.

El TMS9900 también admite la instrucción eXtended OPeration (XOP). A XOP se le asigna un número en el rango de 0 a 15, así como una dirección de origen. Cuando se invoca, la instrucción realizará un cambio de contexto a través de uno de los dieciséis vectores en ubicaciones predefinidas en la memoria. La instrucción XOP también coloca la dirección efectiva del operando de origen en el registro 11 del nuevo espacio de trabajo. La función de guardado de contexto de la instrucción XOP también se puede utilizar para implementar la depuración en línea. [6]

XOP es menos flexible que un BLWP, ya que los vectores de transferencia deben estar en ubicaciones fijas, pero permite que un operando de origen se direccione directamente en lugar de pasarlo en un registro o de otra manera.

XOP se puede utilizar para implementar una función de llamada al sistema. En el sistema operativo DX10 de TI, XOP 15 invoca una llamada al sistema. Un programador podría definir una macro de ensamblador, por ejemplo SVC, que invoca XOP 15. Otro uso de XOP era implementar instrucciones en software que podrían ser manejadas por hardware dedicado en futuras versiones de la serie de minicomputadoras 990. Un ejemplo de tales acciones se puede mostrar en el código a continuación, donde se implementa una función CALL utilizando una instrucción XOP 6. La belleza de esta implementación de una función CALL utilizando una instrucción XOP es que es sencillo agregar verificaciones para determinar si la pila se ha desbordado; por ejemplo, C R10,@2*R9(R13), donde R9 apunta a la dirección del límite de la pila.

; ;************************************************ ;LLAMAR SUBRUTINA ; DEFINIR XOP: LLAMADA DXOP,6 ; MÉTODO DE LLAMADA: CALL @SUBROUTINE_ADDRESS ; R10 <=> PUNTERO DE PILA ;*************************************************** ; ED32 C2AD 0014 XOP6: MOV @2*R10(R13),R10 ;OBTENER PUNTERO DE PILA ED36 064A DECT R10 ;PUNTERO DE PILA DE DECREMENTO ED38 C68E MOV R14,*R10 ;EMPUJE EL PC DE RETORNO EN LA PILA ED3A C38B MOV R11,R14;MOVER EA A R14 (PC) PARA LLAMADA ED3C CB4A 0014 MOV R10,@2*R10(R13) ;ACTUALIZAR PUNTERO DE PILA ED40 0380 RTWP; AHORA ESTAMOS UTILIZANDO EL WP ORIGINAL

En comparaciones típicas con el Intel 8086 , el TMS9900 tenía programas más pequeños. [ cita requerida ] Algunas [ cita requerida ] desventajas eran el pequeño espacio de direcciones y la necesidad de una RAM rápida.

El TMS9900 se implementó en un proceso MOS de compuerta de silicio de canal N, [4] que requirió fuentes de alimentación de +5 V, −5 V y +12 V y un reloj de cuatro fases (sin superposición) con una frecuencia máxima de 3 MHz (ciclo de 333 ns), [7] generalmente generado a partir de un cristal de 48 MHz utilizando un chip generador de reloj TIM9904 (también conocido como 74LS362).

Las instrucciones más cortas requieren ocho ciclos de reloj o 2,7 μs para completarse (suponiendo que no haya ciclos de espera externos), muchas otras tardan entre 10 y 14 ciclos (3,3...4,7 μs); la instrucción de ejecución más larga (DIV) puede tardar hasta 124 ciclos (41,3 μs). [8]

El chip estaba empaquetado en un DIP de 0,9" de ancho y 64 pines (algo inusual en aquel entonces) . La cantidad comparativamente grande de pines permitía que el bus de direcciones de 15 bits (palabras) y el bus de datos de 16 bits se pudiesen utilizar en pines dedicados sin utilizar multiplexación (a diferencia, por ejemplo, de la CPU Intel 8086 ), lo que mantenía simples las conexiones de memoria externa. Al contrario de la convención utilizada por muchos otros fabricantes, TI etiquetó las líneas de datos y direcciones más importantes como "A0" y "D0", respectivamente. Todas las rutas de datos internas y la ALU tienen 16 bits de ancho.

El procesador puede pausarse con el bus de direcciones en estado triple para el acceso directo a memoria externa (DMA). Los accesos a memoria siempre tienen un ancho de 16 bits y la CPU realiza automáticamente operaciones de lectura antes de escritura para los accesos de ancho de byte.

El sistema de interrupción de hardware admite una entrada de prioridad de interrupción de 4 bits, que debe ser mayor que el nivel de prioridad almacenado en el registro de estado (bits 12-15) para que se pueda atender la solicitud de interrupción. Además, la entrada /LOAD proporciona una función de interrupción no enmascarable con un vector dedicado. [9]

La CPU TMS9900 también contiene un registro de desplazamiento de 16 bits ("CRU") diseñado para interactuar con registros de desplazamiento externos, con instrucciones dedicadas que admiten el acceso a campos de 1 a 16 bits de ancho de un total de 4096 bits direccionables.

Los periféricos paralelos se pueden conectar mediante mapas de memoria al bus de direcciones y datos normal.

El TMS9900 se utilizó en los ordenadores domésticos TI-99/4 y TI-99/4A . Lamentablemente, para reducir los costes de producción, TI decidió utilizar en estos sistemas sólo 128 palabras de 16 bits del tipo rápido de RAM a la que el TMS9900 podía acceder directamente. El resto de la memoria eran 16 KB de DRAM de 8 bits a los que sólo se podía acceder indirectamente a través del controlador de pantalla de vídeo, lo que perjudicaba el rendimiento del TI-99/4.

TI desarrolló la serie TM990 de módulos informáticos, que incluían CPU, memoria y E/S, que, al enchufarse a un chasis de tarjeta, podían formar una minicomputadora de 16 bits. Estos se utilizaban normalmente para el control de procesos. [10] Se lanzó un entrenador de microprocesadores en forma de TM990/189. [11]

A finales de la década de 1970, John Walker y Dan Drake desarrollaron tarjetas de bus S100 basadas en el TMS9900 y una pila de software completa para acompañarlo. [12] [13] Más tarde se convirtieron en cofundadores de Autodesk , en parte basándose en el software desarrollado primero para estos sistemas basados en TMS9900. [14]

La segunda generación de la familia de microprocesadores TMS9900 fue el TMS9995, que ofrecía "un rendimiento funcional a velocidades tres veces más rápidas que cualquier procesador anterior de la familia 9900", [15] en gran medida debido a la inclusión de la tecnología de precarga de instrucciones. En el ámbito de las computadoras domésticas, el TMS9995 solo encontró uso en el Tomy Tutor , una actualización esotérica de la TI99-4/A llamada Geneve 9640 y un proyecto publicado en Electronics Today : el Powertran Cortex. [16] Se planeó que se utilizara en los sistemas informáticos TI-99/2 y TI-99/8, pero ninguno avanzó más allá de la etapa de prototipo.

Más tarde, TI desarrolló la familia de microprocesadores TMS99000, más potente, que se utilizó como CPU en la minicomputadora 990/10A para reducir costos. Desafortunadamente, cuando la 990/10A llegó al mercado, el fin de la era de las minicomputadoras ya estaba a la vista.

La familia TMS99000 incluye dos microprocesadores, [1] el TMS99105A y el TMS99110A, que son idénticos excepto por el contenido de la memoria ROM macrostore en chip (la memoria macrostore contiene funciones o instrucciones agregadas a través de rutinas de emulación escritas en código de máquina estándar). La memoria ROM macrostore en chip en el microprocesador TMS99110A contiene instrucciones de punto flotante que están disponibles como parte del conjunto de instrucciones de lenguaje de máquina, mientras que el TMS99105A de referencia no las contiene. Ambos chips pueden implementar instrucciones Macrostore en una ROM externa. Se anunció un tercer miembro de la familia TMS99000, el TMS99120, [17] pero es posible que nunca se haya producido comercialmente. La memoria ROM macrostore en chip en el TMS99120 debía contener rutinas de soporte de tiempo de ejecución para el lenguaje de alto nivel PASCAL.

El conjunto de instrucciones de la familia TMS99000 amplía el conjunto de instrucciones 9900 manteniendo la compatibilidad. Las instrucciones adicionales incluyen las de multiplicación y división con signo (que aparecieron por primera vez en el TMS9995), desplazamiento de palabras largas, suma y resta; registro de estado de carga, puntero de espacio de trabajo de carga, operaciones de pila, compatibilidad con multiprocesador y manipulación de bits. Los miembros de la familia pueden acceder a 256 KB de memoria a través de la segmentación de código/datos y pueden utilizar el mapeador de memoria TIM99610 para direccionar hasta 16 MiB. La arquitectura contiene muchos otros avances con respecto al TMS9900 y al TMS9995. [1]