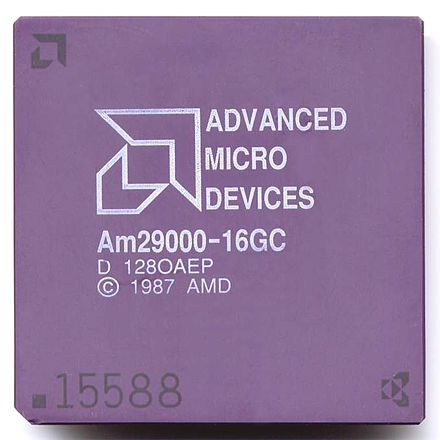

El AMD Am29000 , comúnmente abreviado como 29k , es una familia de microprocesadores y microcontroladores RISC de 32 bits desarrollados y fabricados por Advanced Micro Devices (AMD). Basado en el seminal Berkeley RISC , el 29k agregó una serie de mejoras significativas. Fueron, durante un tiempo, los chips RISC más populares del mercado, [ cita requerida ] ampliamente utilizados en impresoras láser de una variedad de fabricantes.

Desarrollado desde 1984-1985, anunciado en marzo de 1987 y lanzado en mayo de 1988, [1] [2] [3] el Am29000 inicial fue seguido por varias versiones, terminando con el Am29040 en 1995. [4] El 29050 fue notable por ser uno de los primeros en incorporar una unidad de punto flotante capaz de ejecutar una operación de multiplicación-suma por ciclo.

AMD estuvo diseñando una versión superescalar hasta finales de 1995, cuando abandonó el desarrollo del 29k porque el equipo de diseño fue transferido para dar soporte al sector de PC ( x86 ) del negocio. Lo que quedaba del negocio integrado de AMD se reorientó hacia la familia 186 integrada de derivados del 80186. Para entonces, la mayoría de los recursos de AMD se concentraron en sus procesadores x86 de alto rendimiento para PC de escritorio, utilizando muchas de las ideas y partes individuales de los diseños 29k para producir el AMD K5 .

El 29k evolucionó a partir del mismo diseño RISC de Berkeley que también condujo a Sun SPARC , Intel i960 , ARM y RISC-V .

Un elemento de diseño utilizado en algunos de los diseños derivados de RISC de Berkeley es el concepto de ventanas de registro , una técnica utilizada para acelerar significativamente las llamadas a procedimientos . La idea es utilizar un gran conjunto de registros como una pila, cargando datos locales en un conjunto de registros durante una llamada y marcándolos como "muertos" cuando el procedimiento retorna. Los valores que se devuelven de las rutinas se colocarían en la "página global", los ocho registros superiores en el SPARC (por ejemplo). El diseño RISC temprano competidor de la Universidad de Stanford , Stanford MIPS , también analizó este concepto, pero decidió que los compiladores mejorados podrían hacer un uso más eficiente de los registros de propósito general que una ventana cableada.

En el diseño original de Berkeley, SPARC e i960, las ventanas tenían un tamaño fijo. Una rutina que usara solo una variable local seguiría utilizando ocho registros en SPARC, desperdiciando este costoso recurso. Fue aquí donde el 29000 se diferenció de estos diseños anteriores, utilizando un tamaño de ventana variable. En este ejemplo, solo se utilizarían dos registros, uno para la variable local y otro para la dirección de retorno . También agregó más registros, incluidos los mismos 128 registros para la pila de procedimientos, pero agregó otros 64 para el acceso global. En comparación, SPARC tenía 128 registros en total y el conjunto global era una ventana estándar de ocho. Este cambio resultó en un uso mucho mejor de los registros en el 29000 bajo una amplia variedad de cargas de trabajo.

El 29000 también amplió la pila de ventanas de registro con una pila en memoria (y en teoría, en caché). Cuando la ventana se llenaba, las llamadas se enviaban desde el final de la pila de registros a la memoria y se restauraban cuando la rutina volvía. En general, el uso de registros del 29000 era considerablemente más avanzado que el de los diseños de la competencia basados en los conceptos de Berkeley.

Otra diferencia con el diseño de Berkeley es que el 29000 no incluía ningún registro de código de condición de propósito especial. Cualquier registro podía ser utilizado para este propósito, permitiendo que las condiciones se guardaran fácilmente a costa de complicar algún código. Un Branch Target Cache (512 bytes en el 29000 y 1024 bytes en el 29050) almacenaba conjuntos de 4 o 2 instrucciones secuenciales encontradas en la dirección de destino de la bifurcación, reduciendo la latencia de búsqueda de instrucciones durante las bifurcaciones tomadas; el 29000 no incluía ningún sistema de predicción de bifurcaciones, por lo que había un retraso si se tomaba una bifurcación. Esto significa que el 29000 tiene una única ranura de retraso de bifurcación . [5] El búfer mitigaba esto almacenando cuatro o dos instrucciones de la dirección de destino de la bifurcación, que podían ejecutarse instantáneamente mientras el búfer de búsqueda se rellenaba con nuevas instrucciones de la memoria. [6]

El soporte para la traducción de direcciones virtuales siguió un enfoque similar al de la arquitectura MIPS. Un buffer de traducción de 64 entradas (TLB) conservaba las asignaciones de direcciones virtuales a físicas y, al encontrar una dirección no traducida, el "error" de TLB resultante hacía que el procesador pasara a una rutina de software responsable de proporcionar cualquier asignación adecuada a la memoria física. A diferencia del enfoque MIPS que empleaba un registro aleatorio para seleccionar la entrada TLB que se reemplazaría en caso de un evento de error de TLB, el 29000 proporcionaba un registro lru (menos utilizado recientemente) dedicado. [7] Algunos productos de la familia 29000 proporcionaban solo 16 entradas TLB para poder dedicar parte del silicio a los periféricos. Para compensar, el tamaño máximo de página empleado por una asignación se aumentó de 8 KB a 16 MB. [8] : 305–306

El primer Am29000 se lanzó en 1988, incluyendo una MMU incorporada, pero el soporte de punto flotante fue transferido a la FPU Am29027 . Las unidades con MMU o Branch Target Cache fallidos se vendieron como Am29005 . [6]

En 1991, la línea se amplió con el Am29030 y el Am29035 , que incluían un caché de instrucciones de 8 KB o 4 KB, respectivamente. [9] Para entonces, [10] también estaba disponible el Am29050 , sin caché en chip pero con una unidad de punto flotante con operaciones de multiplicación-acumulación totalmente canalizadas , un caché de destino de ramificación de 1 KB más grande con una tasa de aciertos declarada del 80% y operaciones de carga mejor canalizadas aceleradas por un caché de direcciones físicas de 4 entradas tipo TLB . Aunque no es un procesador superescalar , permite que una operación de punto flotante y una operación de números enteros se completen en el mismo ciclo. Los lados de números enteros y de punto flotante tienen cada uno su propio puerto de escritura a los registros. [11] Contenía 428.000 transistores [12] en un proceso de 1 micrón [13] con una longitud de canal efectiva de 0,8 micrones [11] y estaba disponible a 20, 25, 33 y 40 MHz. Más tarde, se lanzó el Am29040 a 33, 40 y 50 MHz, siendo como el Am29030 excepto por presentar un caché de datos de 4 KB, una unidad de multiplicación y algunas otras mejoras. [14] El Am29040 de 119 mm2 contenía 1,2 millones de transistores en un proceso de 0,7 micrones. [15] [16]

Se estaba diseñando una versión superescalar de 29K, pero se canceló a favor de x86. Se le dio el nombre en código de Jaguar , [3] y se describió en noviembre de 1994 y agosto de 1995. [17] [18] Era un diseño avanzado, capaz de despacho de cuatro vías en seis estaciones de reserva y ejecución especulativa fuera de orden de instrucciones, con retiro de cuatro vías. El archivo de registros permitía cuatro lecturas y dos escrituras a la vez. Las cachés para instrucciones y datos eran de 8 KB cada una. Las cargas desde la caché podían eludir los almacenes . No tenía FPU en chip debido a razones de costo y al mercado objetivo. Se esperaba que alcanzara una frecuencia de 100 MHz en un proceso de 0,4 micrones. [17] [19]

AMD utilizó la microarquitectura 29K, aún no publicada, como base de la serie K5 de procesadores compatibles con x86 . Las ALU se conservaron, al igual que el búfer de reordenamiento con una ligera modificación. La FPU se tomó del 29050, pero se amplió a una precisión de 80 bits . El K5 tradujo las instrucciones x86 a "RISC-OP" al decodificarlas, con la ayuda de la información de predecodificación que contenían las instrucciones almacenadas en caché. AMD afirmó que el superescalar 29K tendría solo un rendimiento ligeramente inferior al del K5, pero un coste mucho menor debido a la diferencia de tamaño. [20] [17]

La Honeywell 29KII es una CPU basada en el AMD 29050 y se utilizó ampliamente en aviónica en tiempo real.

Posicionado como un producto para "aplicaciones integradas de rendimiento medio a alto" con potencial para su uso en estaciones de trabajo Unix, [7] el 29000 se utilizó en una variedad de productos como terminales X, tarjetas controladoras de impresoras láser, tarjetas aceleradoras de gráficos, soluciones de reconocimiento óptico de caracteres y puentes de red. [21] La arquitectura de memoria del 29000 fue un atractivo particular para los diseñadores de productos, permitiéndoles renunciar a la memoria caché externa y emplear RAM dinámica directamente mientras mantenían un rendimiento aceptable, [21] : 1 permitiendo un grado de flexibilidad en la elección de las tecnologías de memoria utilizadas para retener las instrucciones y los datos del programa. [22]

El 29k se utilizó como acelerador computacional o coprocesador, particularmente en las plataformas compatibles con Macintosh e IBM PC. Por ejemplo, Yarc Systems Corporation produjo tarjetas "coprocesador RISC" basadas en el 29k para sistemas Macintosh II y PC AT , junto con otras tarjetas "coprocesador CISC" con procesadores Motorola 68020 y 68030, y tarjetas "coprocesador paralelo" con procesadores transputer T800 . [23] Sus tarjetas NuSuper (originalmente llamadas McCray [24] ) y AT-Super , que empleaban la CPU Am29000 y el acelerador de punto flotante Am29027, [23] fueron seguidas por MacRageous , que actualizó la CPU al Am29050. [25] Estas tarjetas aceleradoras ofrecían un rendimiento varias veces superior al del propio Macintosh II y competían con estaciones de trabajo RISC como la DECstation 3100. También se podían instalar varias tarjetas en un sistema. Sin embargo, el coste de un sistema Macintosh II combinado con una tarjeta de este tipo se acercaba al de las estaciones de trabajo RISC establecidas que ejecutaban Unix. [26] El precio del AT-Super rondaba los 4.600 dólares y se informó de que ejecutaba Unix, compitiendo con productos similares que empleaban el procesador i860 de Intel. [27]

Un producto notable que utilizaba el 29k era la Macintosh Display Card 8·24 GC de Apple para su Macintosh IIfx , que contaba con un procesador Am29000 de 30 MHz, 64 KB de caché de RAM estática y 2 MB de RAM de video, con la opción de 2 MB adicionales de RAM dinámica para su uso con el kit de herramientas gráficas QuickDraw. La inclusión del 29k diferenció a esta versión particular de la tarjeta de otras versiones vendidas por Apple, mejorando significativamente el rendimiento al manejar imágenes de 24 bits por píxel. [28]

Bueno, empezó en 1985. Y tardó unos tres años y tal vez cuatro revoluciones hasta que estuvo en funcionamiento.