En informática , el orden de endianidad es el orden en el que los bytes dentro de una palabra de datos digitales se transmiten a través de un medio de comunicación de datos o se direccionan (por direcciones ascendentes) en la memoria de la computadora , contando solo la importancia de los bytes en comparación con la anticipación. El orden de endianidad se expresa principalmente como big-endian (BE) o little-endian (LE), términos introducidos por Danny Cohen en la ciencia informática para el ordenamiento de datos en una Nota de Experimento de Internet publicada en 1980. [1] El adjetivo endian tiene su origen en los escritos del escritor anglo-irlandés del siglo XVIII Jonathan Swift . En la novela Los viajes de Gulliver de 1726 , retrata el conflicto entre sectas de liliputienses divididos en aquellos que rompen la cáscara de un huevo cocido desde el extremo grande o desde el extremo pequeño. [2] [3] Por analogía, una CPU puede leer una palabra digital primero el extremo grande o primero el extremo pequeño.

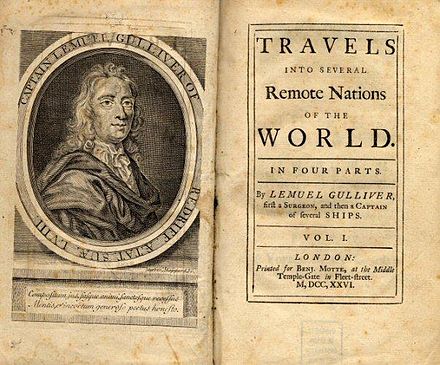

Las computadoras almacenan información en grupos de bits binarios de varios tamaños. A cada grupo se le asigna un número, llamado dirección , que la computadora usa para acceder a esos datos. En la mayoría de las computadoras modernas, el grupo de datos más pequeño con una dirección tiene ocho bits de longitud y se llama byte. Los grupos más grandes comprenden dos o más bytes, por ejemplo, una palabra de 32 bits contiene cuatro bytes. Hay dos formas posibles en que una computadora podría numerar los bytes individuales en un grupo más grande, comenzando en cualquier extremo. Ambos tipos de endianness se usan ampliamente en la ingeniería electrónica digital. La elección inicial de endianness de un nuevo diseño es a menudo arbitraria, pero las revisiones y actualizaciones tecnológicas posteriores perpetúan el endianness existente para mantener la compatibilidad con versiones anteriores .

Un sistema big-endian almacena el byte más significativo de una palabra en la dirección de memoria más pequeña y el byte menos significativo en la más grande. Un sistema little-endian, por el contrario, almacena el byte menos significativo en la dirección más pequeña. [4] [5] [6] De los dos, el big-endian se acerca más a la forma en que se escriben los dígitos de los números de izquierda a derecha en inglés, comparando dígitos con bytes. La bi-endianidad es una característica compatible con numerosas arquitecturas de computadora que presentan endianidad conmutable en las búsquedas y almacenamientos de datos o para las búsquedas de instrucciones. Otros ordenamientos se denominan genéricamente middle-endian o mixed-endian . [7] [8] [9] [10]

El ordenamiento big-endian es el ordenamiento dominante en los protocolos de red, como en el conjunto de protocolos de Internet , donde se lo conoce como orden de red , transmitiendo primero el byte más significativo. Por el contrario, el ordenamiento little-endian es el ordenamiento dominante para las arquitecturas de procesador ( x86 , la mayoría de las implementaciones ARM , implementaciones RISC-V base ) y su memoria asociada. Los formatos de archivo pueden utilizar cualquiera de los dos ordenamientos; algunos formatos utilizan una mezcla de ambos o contienen un indicador de qué ordenamiento se utiliza en todo el archivo. [11]

La memoria de una computadora consiste en una secuencia de celdas de almacenamiento ( unidades direccionables más pequeñas ); en las máquinas que admiten el direccionamiento por bytes , esas unidades se denominan bytes . Cada byte se identifica y se accede a él en hardware y software por su dirección de memoria . Si el número total de bytes en la memoria es n , entonces las direcciones se enumeran de 0 a n − 1.

Los programas informáticos suelen utilizar estructuras de datos o campos que pueden estar compuestos por más datos de los que se pueden almacenar en un byte. En el contexto de este artículo, donde su tipo no puede ser arbitrariamente complicado, un "campo" consiste en una secuencia consecutiva de bytes y representa un "valor de datos simple" que, al menos potencialmente, puede manipularse mediante una única instrucción de hardware . En la mayoría de los sistemas, la dirección de un valor de datos simple de varios bytes es la dirección de su primer byte (el byte con la dirección más baja). Hay excepciones a esta regla; por ejemplo, la instrucción Add del IBM 1401 direcciona los campos de longitud variable en su posición de orden inferior (dirección más alta) y sus longitudes se definen mediante una marca de palabra establecida en su posición de orden superior (dirección más baja). Cuando se realiza una operación como la suma, el procesador comienza en las posiciones de orden inferior en las direcciones altas de los dos campos y avanza hasta el orden superior. [ cita requerida ]

Otro atributo importante de un byte que forma parte de un "campo" es su "significado". Estos atributos de las partes de un campo desempeñan un papel importante en la secuencia en la que el hardware de la computadora accede a los bytes, más precisamente: por los algoritmos de bajo nivel que contribuyen a los resultados de una instrucción de la computadora.

Los sistemas de numeración posicional (en su mayoría de base 2, o con menos frecuencia de base 10) son la forma predominante de representar y, en particular, de manipular datos enteros por parte de las computadoras. En forma pura, esto es válido para números enteros no negativos de tamaño moderado, por ejemplo, del tipo de datos C. unsignedEn un sistema numérico de este tipo, el valor de un dígito con el que contribuye al número entero está determinado no solo por su valor como un solo dígito, sino también por la posición que ocupa en el número completo, llamada su significación. Estas posiciones se pueden mapear a la memoria principalmente de dos maneras: [12]

En estas expresiones, el término "fin" se refiere al extremo donde se escribe primero lo grande o lo pequeño , es decir, donde empieza el campo .

Los datos enteros que son directamente soportados por el hardware de la computadora tienen un ancho fijo de una potencia baja de 2, p. ej. 8 bits ≙ 1 byte, 16 bits ≙ 2 bytes, 32 bits ≙ 4 bytes, 64 bits ≙ 8 bytes, 128 bits ≙ 16 bytes. La secuencia de acceso de bajo nivel a los bytes de dicho campo depende de la operación a realizar. El byte menos significativo es accedido primero para la suma , resta y multiplicación . El byte más significativo es accedido primero para la división y comparación . Véase § Orden de cálculo.

Cuando se deben comparar cadenas de caracteres (texto) entre sí, por ejemplo, para respaldar algún mecanismo como la clasificación , esto se hace con mucha frecuencia de manera lexicográfica, donde un solo elemento posicional (carácter) también tiene un valor posicional. La comparación lexicográfica significa casi en todas partes: el primer carácter ocupa el primer lugar, como en la guía telefónica. Casi todas las máquinas que pueden hacer esto usando una sola instrucción son big-endian o al menos mixed-endian. [ cita requerida ]

Los números enteros escritos como texto siempre se representan con el dígito más significativo primero en la memoria, lo que es similar a big-endian, independientemente de la dirección del texto .

Cuando los bytes de memoria se imprimen secuencialmente de izquierda a derecha (por ejemplo, en un volcado hexadecimal ), la representación little-endian de los números enteros tiene un significado creciente de izquierda a derecha. En otras palabras, aparece al revés cuando se visualiza, lo que puede resultar contraintuitivo.

Este comportamiento surge, por ejemplo, en FourCC o técnicas similares que implican empaquetar caracteres en un entero, de modo que se convierta en una secuencia de caracteres específicos en la memoria. Por ejemplo, tomemos la cadena "JOHN", almacenada en ASCII hexadecimal . En máquinas big-endian, el valor aparece de izquierda a derecha, coincidiendo con el orden correcto de la cadena para leer el resultado ("JOH N"). Pero en una máquina little-endian, uno vería "NHO J". Las máquinas middle-endian complican esto aún más; por ejemplo, en el PDP-11 , el valor de 32 bits se almacena como dos palabras de 16 bits "JO" "HN" en big-endian, con los caracteres en las palabras de 16 bits almacenándose en little-endian, lo que da como resultado "OJN H". [ cita requerida ]

El intercambio de bytes consiste en reorganizar los bytes para cambiar su orden de bytes. Muchos compiladores proporcionan funciones integradas que probablemente se compilarán en instrucciones nativas del procesador ( bswap/ movbe), como __builtin_bswap32. Las interfaces de software para el intercambio incluyen:

winsock2.h.endian.h(desde/hacia BE y LE, hasta 64 bits). [14]OSByteOrder.h (desde/hasta BE y LE, hasta 64 bits).std::byteswapfunción en C++23 . [15]Algunos conjuntos de instrucciones de CPU proporcionan soporte nativo para el intercambio de bytes endian, como bswap[16] ( x86 — 486 y posteriores, i960 — i960Jx y posteriores [17] ) y rev[18] ( ARMv6 y posteriores).

Algunos compiladores tienen funciones integradas para el intercambio de bytes. Por ejemplo, el compilador Intel Fortran admite el especificador no estándar CONVERTal abrir un archivo, p. ej.: . Otros compiladores tienen opciones para generar código que permite globalmente la conversión para todas las operaciones de E/S de archivos. Esto permite la reutilización de código en un sistema con el orden de bytes opuesto sin modificar el código.OPEN(unit, CONVERT='BIG_ENDIAN',...)

En la mayoría de los sistemas, la dirección de un valor multibyte es la dirección de su primer byte (el byte con la dirección más baja); los sistemas little-endian de ese tipo tienen la propiedad de que, para valores de datos suficientemente bajos, el mismo valor se puede leer de la memoria en diferentes longitudes sin utilizar direcciones diferentes (incluso cuando se imponen restricciones de alineación ). Por ejemplo, una ubicación de memoria de 32 bits con contenido 4A 00 00 00se puede leer en la misma dirección que una de 8 bits (valor = 4A), 16 bits (004A), 24 bits (00004A) o 32 bits (0000004A), todas las cuales conservan el mismo valor numérico. Aunque esta propiedad little-endian rara vez es utilizada directamente por programadores de alto nivel, ocasionalmente es empleada por optimizadores de código así como por programadores de lenguaje ensamblador . Si bien no está permitido por C++, este tipo de código de juegos de palabras está permitido como "definido por la implementación" por el estándar C11 [19] y se usa comúnmente [20] en código que interactúa con hardware. [21]

Algunas operaciones en sistemas de numeración posicional tienen un orden natural o preferido en el que se deben ejecutar los pasos elementales. Este orden puede afectar su rendimiento en procesadores y microcontroladores direccionables por bytes de pequeña escala . Sin embargo, los procesadores de alto rendimiento suelen recuperar operandos de varios bytes de la memoria en el mismo tiempo que hubieran necesitado para recuperar un solo byte, por lo que la complejidad del hardware no se ve afectada por el orden de bytes.

La suma, la resta y la multiplicación comienzan en la posición del dígito menos significativo y propagan el acarreo a la posición más significativa subsiguiente. En la mayoría de los sistemas, la dirección de un valor de varios bytes es la dirección de su primer byte (el byte con la dirección más baja). La implementación de estas operaciones es ligeramente más sencilla utilizando máquinas little-endian donde este primer byte contiene el dígito menos significativo.

La comparación y la división comienzan en el dígito más significativo y propagan un posible acarreo a los dígitos menos significativos subsiguientes. Para valores numéricos de longitud fija (normalmente de longitud 1, 2, 4, 8, 16), la implementación de estas operaciones es ligeramente más sencilla en máquinas big-endian.

Algunos procesadores big-endian (por ejemplo, el IBM System/360 y sus sucesores) contienen instrucciones de hardware para comparar lexicográficamente cadenas de caracteres de longitud variable .

El transporte normal de datos mediante una declaración de asignación es, en principio, independiente del orden de bytes del procesador.

Muchos procesadores históricos y actuales utilizan una representación de memoria big-endian, ya sea de forma exclusiva o como una opción de diseño. El IBM System/360 utiliza un orden de bytes big-endian, al igual que sus sucesores System/370 , ESA/390 y z/Architecture . El PDP-10 utiliza el direccionamiento big-endian para instrucciones orientadas a bytes. La minicomputadora IBM Series/1 utiliza un orden de bytes big-endian. Los procesadores Motorola 6800/6801 , 6809 y 68000 utilizan el formato big-endian. Las arquitecturas que utilizan únicamente el formato big-endian incluyen IBM z/Architecture y OpenRISC .

El Datapoint 2200 utilizó una lógica bit-serial simple con little-endian para facilitar la propagación del acarreo . Cuando Intel desarrolló el microprocesador 8008 para Datapoint, utilizaron little-endian para compatibilidad. Sin embargo, como Intel no pudo entregar el 8008 a tiempo, Datapoint utilizó un equivalente de integración de escala media , pero el little-endian se mantuvo en la mayoría de los diseños de Intel, incluidos el MCS-48 y el 8086 y sus sucesores x86 . [22] [23] El DEC Alpha , Atmel AVR , VAX , la familia MOS Technology 6502 (incluidos Western Design Center 65802 y 65C816 ), el Zilog Z80 (incluidos Z180 y eZ80 ), el Altera Nios II y muchos otros procesadores y familias de procesadores también son little-endian.

A diferencia de otros procesadores Intel, el Intel 8051 espera direcciones de 16 bits para LJMP y LCALL en formato big-endian; sin embargo, las instrucciones xCALL almacenan la dirección de retorno en la pila en formato little-endian. [24]

Las arquitecturas de conjuntos de instrucciones IA-32 y x86-64 utilizan el formato little-endian. Otras arquitecturas de conjuntos de instrucciones que siguen esta convención, que solo permiten el modo little-endian, incluyen Nios II , Andes Technology NDS32 y Qualcomm Hexagon .

Algunas arquitecturas de conjuntos de instrucciones son "bi-endian" y permiten ejecutar software de cualquier endianidad; estas incluyen Power ISA , SPARC , ARM AArch64 , C-Sky y RISC-V . IBM AIX e IBM i se ejecutan en modo big-endian en Power ISA bi-endian; Linux originalmente se ejecutaba en modo big-endian, pero en 2019, IBM había hecho la transición al modo little-endian para Linux para facilitar la portabilidad del software Linux de x86 a Power. [25] [26] SPARC no tiene una implementación little-endian relevante, ya que tanto Oracle Solaris como Linux se ejecutan en modo big-endian en sistemas SPARC bi-endian, y pueden considerarse big-endian en la práctica. ARM, C-Sky y RISC-V no tienen implementaciones big-endian relevantes, y pueden considerarse little-endian en la práctica.

Algunas arquitecturas (incluidas las versiones ARM 3 y superiores, PowerPC , Alpha , SPARC V9, MIPS , Intel i860 , PA-RISC , SuperH SH-4 e IA-64 ) cuentan con una configuración que permite el uso de endianness conmutable en la obtención y el almacenamiento de datos, la obtención de instrucciones o ambos. Esta característica puede mejorar el rendimiento o simplificar la lógica de los dispositivos y el software de red. La palabra bi-endian , cuando se dice del hardware, denota la capacidad de la máquina para calcular o pasar datos en cualquier formato endian.

Muchas de estas arquitecturas se pueden cambiar a través del software para que tengan como formato endian predeterminado (generalmente se hace cuando se inicia la computadora); sin embargo, en algunos sistemas, el formato endian predeterminado se selecciona por hardware en la placa base y no se puede cambiar a través del software (por ejemplo, Alpha, que se ejecuta solo en modo big-endian en Cray T3E ).

El término bi-endian se refiere principalmente a cómo un procesador trata los accesos a los datos. Los accesos a instrucciones (obtención de palabras de instrucciones) en un procesador determinado pueden seguir asumiendo un orden de bytes fijo, incluso si los accesos a los datos son completamente bi-endian, aunque este no siempre es el caso, como en la CPU Itanium basada en IA-64 de Intel , que permite ambos.

Algunas CPU nominalmente bi-endian requieren la ayuda de la placa base para cambiar completamente el orden de bits. Por ejemplo, los procesadores PowerPC de 32 bits orientados a computadoras de escritorio en modo little-endian actúan como little-endian desde el punto de vista de los programas en ejecución, pero requieren que la placa base realice un intercambio de 64 bits en las 8 líneas de bytes para garantizar que la visión little-endian de las cosas se aplique a los dispositivos de E/S . En ausencia de este hardware inusual de la placa base, el software del controlador del dispositivo debe escribir en direcciones diferentes para deshacer la transformación incompleta y también debe realizar un intercambio de bytes normal. [ ¿ Investigación original? ]

Algunas CPU, como muchos procesadores PowerPC destinados para uso integrado y casi todos los procesadores SPARC, permiten la elección del orden de bytes por página.

Los procesadores SPARC desde fines de la década de 1990 (procesadores compatibles con SPARC v9) permiten elegir el orden de bytes de los datos con cada instrucción individual que se carga desde o almacena en la memoria.

La arquitectura ARM admite dos modos big-endian, llamados BE-8 y BE-32 . [27] Las CPU hasta ARMv5 solo admiten BE-32 o modo invariante de palabras. Aquí, cualquier acceso de 32 bits alineado naturalmente funciona como en modo little-endian, pero el acceso a un byte o palabra de 16 bits se redirige a la dirección correspondiente y no se permite el acceso no alineado. ARMv6 introduce BE-8 o modo invariante de bytes, donde el acceso a un solo byte funciona como en modo little-endian, pero el acceso a una palabra de 16 bits, 32 bits o (a partir de ARMv8) 64 bits da como resultado un intercambio de bytes de los datos. Esto simplifica el acceso a la memoria no alineada, así como el acceso mapeado en memoria a registros que no sean de 32 bits.

Muchos procesadores tienen instrucciones para convertir una palabra en un registro al orden de bytes opuesto, es decir, intercambian el orden de los bytes en una palabra de 16, 32 o 64 bits.

Las CPU Intel con arquitectura x86 y x86-64 más recientes tienen una instrucción MOVBE ( Intel Core desde la generación 4, después de Atom ), [28] que recupera una palabra en formato big-endian de la memoria o escribe una palabra en la memoria en formato big-endian. Estos procesadores son, por lo demás, completamente little-endian.

También hay dispositivos que utilizan formatos diferentes en distintos lugares. Por ejemplo, el medidor de batería BQ27421 de Texas Instruments utiliza el formato little-endian para sus registros y el formato big-endian para su memoria de acceso aleatorio .

SPARC históricamente utilizó big-endian hasta la versión 9, que es bi-endian. De manera similar, los primeros procesadores IBM POWER eran big-endian, pero los descendientes de PowerPC y Power ISA ahora son bi-endian. La arquitectura ARM era little-endian antes de la versión 3, cuando se convirtió en bi-endian.

Aunque muchos procesadores utilizan el almacenamiento little-endian para todos los tipos de datos (enteros, coma flotante), hay varias arquitecturas de hardware en las que los números de coma flotante se representan en forma big-endian, mientras que los enteros se representan en forma little-endian. [29] Hay procesadores ARM que tienen una representación de coma flotante mixed-endian para números de doble precisión: cada una de las dos palabras de 32 bits se almacena como little-endian, pero la palabra más significativa se almacena primero. El punto flotante VAX almacena palabras little-endian de 16 bits en orden big-endian. Debido a que ha habido muchos formatos de coma flotante sin una representación estándar de red para ellos, el estándar XDR utiliza el IEEE 754 big-endian como su representación. Por lo tanto, puede parecer extraño que el estándar de coma flotante IEEE 754, ampliamente extendido , no especifique el orden de bytes. [30] Teóricamente, esto significa que incluso los datos de coma flotante IEEE estándar escritos por una máquina podrían no ser legibles por otra. Sin embargo, en las computadoras estándar modernas (es decir, que implementan IEEE 754), se puede asumir con seguridad que el orden de bytes es el mismo para los números de punto flotante que para los números enteros, lo que hace que la conversión sea sencilla independientemente del tipo de datos. Sin embargo, los sistemas integrados pequeños que utilizan formatos especiales de punto flotante pueden ser otra cosa.

La mayoría de las instrucciones consideradas hasta ahora contienen el tamaño (longitudes) de sus operandos dentro del código de operación . Las longitudes de operando disponibles con frecuencia son 1, 2, 4, 8 o 16 bytes. Pero también hay arquitecturas en las que la longitud de un operando puede mantenerse en un campo separado de la instrucción o con el operando mismo, por ejemplo, por medio de una marca de palabra . Tal enfoque permite longitudes de operando de hasta 256 bytes o más. Los tipos de datos de tales operandos son cadenas de caracteres o BCD . Las máquinas capaces de manipular tales datos con una instrucción (por ejemplo, comparar, sumar) incluyen IBM 1401 , 1410 , 1620 , System/360 , System/370 , ESA/390 y z/Architecture , todas ellas de tipo big-endian.

Son posibles numerosos otros ordenamientos, denominados genéricamente middle-endian o mixed-endian .

El PDP-11 es en principio un sistema little-endian de 16 bits. Las instrucciones para convertir entre valores de punto flotante y enteros en el procesador de punto flotante opcional del PDP-11/45, PDP-11/70 y algunos procesadores posteriores almacenaban valores de 32 bits "enteros largos de doble precisión" con las mitades de 16 bits intercambiadas con respecto al orden little-endian esperado. El compilador C de UNIX utilizó el mismo formato para los enteros largos de 32 bits. Este ordenamiento se conoce como PDP-endian . [31]

UNIX fue uno de los primeros sistemas que permitía compilar el mismo código para plataformas con diferentes representaciones internas. Uno de los primeros programas convertidos debía imprimir Unix, pero en la Serie/1 lo hizo nUxi. [32]

Una forma de interpretar este orden de bytes es que almacena un entero de 32 bits como dos palabras little-endian de 16 bits, con un orden de palabras big-endian:

Los descriptores de segmento de los procesadores IA-32 y compatibles mantienen una dirección base de 32 bits del segmento almacenado en orden little-endian, pero en cuatro bytes no consecutivos, en las posiciones relativas 2, 3, 4 y 7 del inicio del descriptor. [33]

Los lenguajes de descripción de hardware (HDL) que se utilizan para expresar lógica digital suelen admitir orden de bytes arbitrario, con granularidad arbitraria. Por ejemplo, en SystemVerilog , una palabra se puede definir como little-endian o big-endian. [ cita requerida ]

El reconocimiento del endianness es importante al leer un archivo o un sistema de archivos creado en una computadora con un endianness diferente.

Los archivos Fortran secuenciales sin formato creados con un orden de bits normalmente no se pueden leer en un sistema que utilice el otro orden de bits porque Fortran generalmente implementa un registro (definido como los datos escritos por una sola sentencia Fortran) como datos precedidos y seguidos por campos de conteo, que son números enteros iguales a la cantidad de bytes en los datos. Un intento de leer un archivo de este tipo utilizando Fortran en un sistema con el otro orden de bits da como resultado un error en tiempo de ejecución, porque los campos de conteo son incorrectos.

El texto Unicode puede comenzar opcionalmente con una marca de orden de bytes (BOM) para indicar el orden de bytes del archivo o flujo. Su punto de código es U+FEFF. En UTF-32 , por ejemplo, un archivo big-endian debe comenzar con 00 00 FE FF; un archivo little-endian debe comenzar con FF FE 00 00.

Los formatos de datos binarios de aplicación, como los archivos .mat de MATLAB o el formato de datos .bil , utilizados en topografía, suelen ser independientes del orden de bytes. Esto se consigue almacenando los datos siempre en un orden de bytes fijo o llevando con los datos un interruptor para indicar el orden de bytes. Un ejemplo del primero es el formato de archivo binario XLS , que es portátil entre sistemas Windows y Mac y siempre little-endian, lo que requiere que la aplicación Mac intercambie los bytes al cargar y guardar cuando se ejecuta en un procesador Motorola 68K o PowerPC big-endian. [34]

Los archivos de imagen TIFF son un ejemplo de la segunda estrategia, cuyo encabezado instruye a la aplicación sobre el endianness de sus enteros binarios internos. Si un archivo comienza con la firma MMsignifica que los enteros se representan como big-endian, mientras que IIsignifica little-endian. Esas firmas necesitan una sola palabra de 16 bits cada una, y son palíndromos , por lo que son independientes del endianness. Isignifica Intel y Msignifica Motorola . Las CPU Intel son little-endian, mientras que las CPU Motorola 680x0 son big-endian. Esta firma explícita permite que un programa lector de TIFF intercambie bytes si es necesario cuando un archivo dado fue generado por un programa escritor de TIFF que se ejecuta en una computadora con un endianness diferente.

Como consecuencia de su implementación original en la plataforma Intel 8080, el sistema de archivos de la Tabla de asignación de archivos (FAT) independiente del sistema operativo se define con un orden de bytes little-endian, incluso en plataformas que usan otro orden de bytes de forma nativa, lo que requiere operaciones de intercambio de bytes para mantener la FAT en estas plataformas.

Se sabe que ZFS , que combina un sistema de archivos y un administrador de volúmenes lógicos , proporciona endianidad adaptativa y funciona con sistemas big-endian y little-endian. [35]

Muchas RFC de la IETF utilizan el término orden de red , que hace referencia al orden de transmisión de bytes por cable en los protocolos de red . Entre otras, la histórica RFC 1700 define el orden de red para los protocolos de la suite de protocolos de Internet como big-endian. [36]

Sin embargo, no todos los protocolos utilizan el orden de bytes big-endian como orden de red. El protocolo Server Message Block (SMB) utiliza el orden de bytes little-endian. En CANopen , los parámetros multibyte siempre se envían primero con el byte menos significativo (little-endian). Lo mismo ocurre con Ethernet Powerlink . [37]

La API de sockets de Berkeley define un conjunto de funciones para convertir números enteros de 16 y 32 bits hacia y desde el orden de bytes de red: las funciones (host-to-network-short) y (host-to-network-long) convierten valores de 16 y 32 bits respectivamente desde el orden de máquina ( host ) al orden de red; las funciones y convierten desde el orden de red al orden de host. [38] [39] Estas funciones pueden ser una operación sin efecto en un sistema big-endian.htonshtonlntohsntohl

Si bien los protocolos de red de alto nivel generalmente consideran al byte (generalmente entendido como octeto ) como su unidad atómica, las capas más bajas de una pila de red pueden ocuparse del ordenamiento de bits dentro de un byte.