En ingeniería informática , las ventanas de registro son una característica que dedica registros a una subrutina mediante la creación de alias dinámicos de un subconjunto de registros internos a registros fijos visibles para el programador. Las ventanas de registro se implementan para mejorar el rendimiento de un procesador al reducir la cantidad de operaciones de pila necesarias para las llamadas y devoluciones de funciones. Una de las características más influyentes del diseño RISC de Berkeley , se implementaron más tarde en arquitecturas de conjuntos de instrucciones como AMD Am29000 , Intel i960 , Sun Microsystems SPARC e Intel Itanium .

Se proporcionan varios conjuntos de registros para las distintas partes del programa. Los registros se ocultan deliberadamente al programador para obligar a varias subrutinas a compartir los recursos del procesador.

La invisibilidad de los registros se puede implementar de manera eficiente; la CPU reconoce el movimiento de una parte del programa a otra durante una llamada a un procedimiento. Esto se logra mediante una de una pequeña cantidad de instrucciones ( prólogo ) y termina con una de un conjunto igualmente pequeño ( epílogo ) . En el diseño de Berkeley, estas llamadas harían que se "intercambie" un nuevo conjunto de registros en ese punto, o que se marquen como "muertos" (o "reutilizables") cuando finalice la llamada.

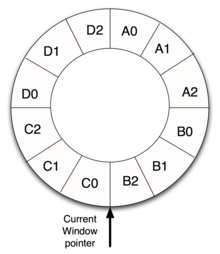

En el diseño RISC de Berkeley, sólo ocho registros de un total de 64 son visibles para los programas. El conjunto completo de registros se conoce como archivo de registros y cualquier conjunto particular de ocho como ventana . El archivo permite que hasta ocho llamadas a procedimientos tengan sus propios conjuntos de registros. Mientras el programa no invoque cadenas de más de ocho llamadas de profundidad, los registros nunca tienen que ser volcados , es decir, guardados en la memoria principal o caché, lo que es un proceso lento en comparación con el acceso a los registros.

En comparación, la arquitectura SPARC de Sun Microsystems proporciona visibilidad simultánea en cuatro conjuntos de ocho registros cada uno. Tres conjuntos de ocho registros cada uno están "en ventana". Ocho registros (i0 a i7) forman los registros de entrada al nivel de procedimiento actual. Ocho registros (L0 a L7) son locales al nivel de procedimiento actual, y ocho registros (o0 a o7) son las salidas del nivel de procedimiento actual al siguiente nivel llamado. Cuando se llama a un procedimiento, la ventana de registros se desplaza dieciséis registros, ocultando los antiguos registros de entrada y los antiguos registros locales y convirtiendo los antiguos registros de salida en los nuevos registros de entrada. Los registros comunes (antiguos registros de salida y nuevos registros de entrada) se utilizan para el paso de parámetros. Finalmente, ocho registros (g0 a g7) son visibles globalmente para todos los niveles de procedimiento.

El AMD 29000 mejoró el diseño al permitir que las ventanas sean de tamaño variable, lo que facilita su utilización en el caso común en el que se necesitan menos de ocho registros para una llamada. También separó los registros en un conjunto global de 64 y 128 adicionales para las ventanas. De manera similar, la arquitectura IA-64 (Itanium) utilizó ventanas de tamaño variable, con 32 registros globales y 96 para las ventanas.

En la arquitectura Infineon C166 , la mayoría de los registros son simplemente ubicaciones en la memoria RAM interna que tienen la propiedad adicional de ser accesibles como registros. De estos, las direcciones de los 16 registros de propósito general (R0-R15) no son fijas. En cambio, el registro R0 se encuentra en la dirección indicada por el registro "Context Pointer" (CP), y los 15 registros restantes siguen secuencialmente a partir de ahí. [1]

Las ventanas de registro también proporcionan una vía de actualización sencilla. Dado que los registros adicionales son invisibles para los programas, se pueden añadir ventanas adicionales en cualquier momento. Por ejemplo, el uso de la programación orientada a objetos suele dar lugar a una mayor cantidad de llamadas "más pequeñas", que se pueden gestionar aumentando las ventanas de ocho a dieciséis, por ejemplo. Este fue el enfoque utilizado en SPARC, que ha incluido más ventanas de registro con las nuevas generaciones de la arquitectura. El resultado final es una menor cantidad de operaciones de llenado y desbordamiento de ventanas de registro porque las ventanas de registro se desbordan con menos frecuencia.

Las ventanas de registro no son la única forma de mejorar el rendimiento de los registros. El grupo de la Universidad de Stanford que diseñó el MIPS vio el trabajo de Berkeley y decidió que el problema no era la falta de registros, sino la mala utilización de los existentes. En su lugar, invirtieron más tiempo en la asignación de registros de su compilador , asegurándose de que utilizara sabiamente el conjunto más grande disponible en MIPS. Esto dio como resultado una menor complejidad del chip, con la mitad del número total de registros, al tiempo que ofrecía un rendimiento potencialmente mayor en aquellos casos en los que un solo procedimiento podía hacer uso del espacio de registros visible más grande. Al final, con los compiladores modernos, MIPS hace un mejor uso de su espacio de registros incluso durante las llamadas a procedimientos. [ cita requerida ]