En telecomunicaciones y transmisión de datos , la comunicación serial es el proceso de enviar datos bit a bit , de manera secuencial, a través de un canal de comunicación o bus de computadora . Esto contrasta con la comunicación paralela , donde se envían varios bits en conjunto, en un enlace con varios canales paralelos.

La comunicación en serie se utiliza para todas las comunicaciones de larga distancia y la mayoría de las redes de ordenadores , donde el coste del cable y las dificultades de sincronización hacen que la comunicación en paralelo sea poco práctica. Los buses de ordenador en serie se han vuelto más comunes incluso a distancias más cortas, ya que la integridad de la señal mejorada y las velocidades de transmisión en las tecnologías en serie más nuevas han comenzado a superar la ventaja de simplicidad del bus paralelo (no se necesita serializador y deserializador, o SerDes ) y a superar sus desventajas ( desfase de reloj , densidad de interconexión). La migración de PCI a PCI Express es un ejemplo.

Las interfaces seriales modernas de alta velocidad como PCIe [2] [3] [4] envían datos varios bits a la vez utilizando técnicas de modulación/codificación como PAM4 que agrupa 2 bits a la vez en un solo símbolo, y varios símbolos se siguen enviando uno a la vez. Esto reemplaza a PAM2 o sin retorno a cero (NRZ) que solo envía un bit a la vez, o en otras palabras, un bit por símbolo. [5] [6] [7] [8] [9] [10] [11] [12] Los símbolos se envían a una velocidad conocida como tasa de símbolos o tasa de baudios. [13] [14] [15] [16]

Muchos sistemas de comunicación en serie fueron diseñados originalmente para transferir datos a distancias relativamente grandes a través de algún tipo de cable de datos .

Prácticamente todas las comunicaciones a larga distancia transmiten los datos bit a bit, en lugar de hacerlo en paralelo, porque así se reduce el coste del cable. Los cables que transportan estos datos (excepto "el" cable serial) y los puertos de ordenador a los que se conectan suelen recibir un nombre más específico para reducir la confusión.

Los cables y puertos del teclado y del mouse son casi invariablemente seriales, como el puerto PS/2 , Apple Desktop Bus y USB .

Los cables que transportan vídeo digital también son en su mayoría seriales, como un cable coaxial conectado a un puerto HD-SDI , una cámara web conectada a un puerto USB o FireWire , un cable Ethernet que conecta una cámara IP a un puerto Power over Ethernet , FPD-Link , líneas telefónicas digitales (por ejemplo, ISDN ), etc.

Otros cables y puertos similares, que transmiten datos bit a bit, incluyen Serial ATA , Serial SCSI , cable Ethernet conectado a puertos Ethernet , el canal de datos de pantalla que utiliza pines previamente reservados del conector VGA o el puerto DVI o el puerto HDMI .

Muchos sistemas de comunicación fueron diseñados generalmente para conectar dos circuitos integrados en la misma placa de circuito impreso , conectados por trazas de señal en esa placa (en lugar de cables externos).

Los circuitos integrados son más caros cuando tienen más pines. Para reducir la cantidad de pines en un encapsulado, muchos circuitos integrados utilizan un bus serial para transferir datos cuando la velocidad no es importante. Algunos ejemplos de estos buses seriales de bajo costo y menor velocidad incluyen RS-232 , DALI , SPI , bus CAN , I²C , UNI/O y 1-Wire . Los buses seriales de mayor velocidad incluyen USB , SATA y PCI Express .

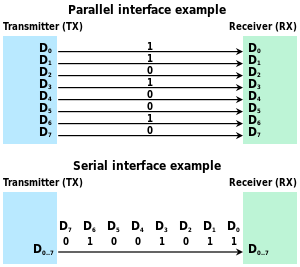

Los enlaces de comunicación a través de los cuales los ordenadores (o partes de ordenadores) se comunican entre sí pueden ser seriales o paralelos. Un enlace paralelo transmite varios flujos de datos simultáneamente a lo largo de múltiples canales (por ejemplo, cables, pistas de circuitos impresos o fibras ópticas); mientras que un enlace serial transmite solo un único flujo de datos. La razón de ser de la comunicación paralela era el beneficio adicional de tener acceso directo a la memoria a las direcciones de registro de 8 o 16 bits en una época en la que la asignación de líneas de datos directas era más conveniente y rápida que la sincronización de datos en serie. [ cita requerida ]

Aunque un enlace en serie puede parecer inferior a uno en paralelo, ya que puede transmitir menos datos por ciclo de reloj, a menudo se da el caso de que los enlaces en serie pueden sincronizarse considerablemente más rápido que los enlaces en paralelo para lograr una mayor velocidad de datos. Varios factores permiten que el enlace en serie se sincronice a una velocidad mayor:

La transición de buses paralelos a buses seriales fue posible gracias a la ley de Moore , que permitió la incorporación de SerDes en circuitos integrados. [20] Un enlace serial eléctrico solo requiere un par de cables, mientras que un enlace paralelo requiere varios. Por lo tanto, los enlaces seriales pueden ahorrar costos (también conocido como Lista de materiales ). La señalización diferencial utiliza cables o conductores de longitud coincidente y se utilizan en enlaces seriales de alta velocidad. [21] La coincidencia de longitud es más fácil de realizar en enlaces seriales, ya que requieren menos conductores.

En muchos casos, la implementación en serie es más barata que en paralelo. Muchos circuitos integrados tienen interfaces en serie, en lugar de en paralelo, por lo que tienen menos pines y, por lo tanto, son más económicos.