List of computer processors by Intel

CPU Intel Haswell Core i7-4771, colocada sobre su embalaje original que contiene un disipador térmico refrigerado por ventilador OEM Esta lista generacional de procesadores Intel intenta presentar todos los procesadores Intel desde el 4004 de 4 bits (1971) hasta las ofertas de gama alta actuales. Se proporcionan datos técnicos concisos para cada producto.

El último

Core de 13.ª y 14.ª generación Lago Raptor ") (14ª generación)El 17 de octubre de 2023 se lanzó una actualización iterativa de los procesadores de escritorio Raptor Lake-S, llamada 14.ª generación de Intel Core. [1] [2]

Las CPU en negrita a continuación cuentan con soporte de memoria ECC solo cuando se combinan con una placa base basada en el chipset W680 según cada página de producto Intel Ark respectiva.

Lago Raptor ") (14ª generación)El 9 de enero de 2024 se lanzó una actualización iterativa de los procesadores móviles Raptor Lake-HX, llamada 14.ª generación de Intel Core [3] .

Lago Raptor ") (13.ª generación)Lago Raptor ") (13.ª generación)

12.ª generación de núcleos

Núcleo de 11.ª generación

Núcleo de décima generación

Núcleo de novena generación

Octava generación de núcleos

Séptima generación de núcleos

Todos los procesadores Todos los procesadores están enumerados en orden cronológico.

El4 bitsprocesadores Intel D4004 (variante cerámica) Intel P4004 (variante de plástico) Primer microprocesador (procesador de circuito integrado de un solo chip)

Familia MCS-4:

4004 – Procesador 4001 – ROM y puerto de 4 bits 4002 – RAM y puerto de 4 bits 4003 – Registro de desplazamiento de 10 bits 4008 – Interfaz de memoria + E/S 4009 – Interfaz de memoria + E/S 4211 – Puerto de E/S de bytes de propósito general 4265 – Dispositivo de E/S programable de propósito general 4269 – Dispositivo de visualización con teclado programable 4289 – Interfaz de memoria estándar para MCS-4/40 4308 – ROM de 8192 bits (1024 × 8) con puertos de E/S de 4 bits 4316 – ROM estática de 16384 bits (2048 × 8) 4702 – EPROM de 2048 bits (256 × 8) 4801 – Cristal generador de reloj de 5,185 MHz para 4004/4201A o 4040/4201A Intel C4040 Introducido en 1974 por Intel La velocidad del reloj era de 740 kHz (igual que el microprocesador 4004) 3.000 transistores Las funciones de interrupción estaban disponibles Tamaño de memoria programable: 8 KB (8192 B) 640 bytes de memoria de datos DIP de 24 pines

El8 bitsprocesadores Intel D8008

8008 Introducido el 1 de abril de 1972 Frecuencia de reloj 500 kHz (8008-1: 800 kHz) 0,05 MILÍMETROS POR SEGUNDO PULGADA Ancho de bus: 8 bits (dirección/datos multiplexados debido a pines limitados) Mejora de la carga lógica PMOS 3.500 transistores a 10 μm Memoria direccionable 16 KB Típico de los primeros microordenadores de 8 bits, terminales tontas, calculadoras generales y máquinas embotelladoras. Desarrollado en conjunto con 4004 Originalmente pensado para su uso en la microcomputadora Datapoint 2200 Implementación de gran volumen en el microordenador Texas Instruments 742 en más de 3.000 concesionarios Ford Intel D8080

8080 Introducido el 1 de abril de 1974 Frecuencia de reloj 2 MHz (muy raro 8080B: 3 MHz) 0,29 MILÍMETROS POR SEGUNDO PULGADA [5] Ancho del bus de datos: 8 bits, bus de direcciones: 16 bits Mejora de la carga lógica NMOS 4.500 transistores de 6 μm Lenguaje ensamblador compatible con versiones anteriores del modelo 8008Memoria direccionable 64 KB (64 × 1024 B) Hasta 10 veces el rendimiento del 8008 Se utiliza, por ejemplo, en el Altair 8800 , controlador de semáforo y misil de crucero. Se requieren seis chips de soporte frente a los 20 del 8008 Intel D8085A Intel P8085 (variante de plástico)

8085

Microcontroladores Son circuitos integrados con CPU, RAM, ROM (o PROM o EPROM), puertos de E/S, temporizadores e interrupciones.

Intel P8048H Familia MCS-48 :

Intel 8020: microcontrolador de 8 bits de un solo componente, 1 KB de ROM, 64 bytes de RAM, 13 puertos de E/S Intel 8021: microcontrolador de 8 bits de un solo componente, 1 KB de ROM, 64 bytes de RAM, 21 puertos de E/S Intel 8022: microcontrolador de 8 bits y un solo componente con convertidor A/D integrado Intel 8035: microcontrolador de 8 bits y un solo componente, 64 bytes de RAM Intel 8039: microcontrolador de 8 bits y un solo componente, 128 bytes de RAM Intel 8040: microcontrolador de 8 bits y un solo componente, 256 bytes de RAM Intel 8048: microcontrolador de 8 bits de un solo componente, 1 KB de ROM, 64 bytes de RAM, 27 puertos de E/S, 0,73 MIPS a 11 MHz Intel 8049: microcontrolador de un solo componente de 8 bits, 2 KB de ROM, 128 bytes de RAM, 27 puertos de E/S, Intel 8050: microcontrolador de 8 bits de un solo componente, 4 KB de ROM, 256 bytes de RAM, 27 puertos de E/S, Intel 8748: microcontrolador de 8 bits de un solo componente, EPROM de 1 KB, RAM de 64 bytes, 27 puertos de E/S, Intel 8749 – Microcontrolador de 8 bits de un solo componente, EPROM de 2 KB, RAM de 128 bytes, 27 puertos de E/S, Intel 87P50: microcontrolador de 8 bits de un solo componente, zócalo de ROM externo (2758/2716/2732), RAM de 256 bytes, 27 puertos de E/S Intel 8648: microcontrolador de 8 bits de un solo componente, EPROM OTP de 1 KB, RAM de 64 bytes, 27 puertos de E/S Intel 8041: microcontrolador esclavo de 8 bits con interfaz periférica universal, 1 KB de ROM y 64 bytes de RAM Intel 8041AH: microcontrolador esclavo de 8 bits con interfaz periférica universal, 1 KB de ROM y 128 bytes de RAM Intel 8641 – Microcontrolador esclavo de 8 bits con interfaz periférica universal ? Intel 8741: microcontrolador esclavo de 8 bits con interfaz periférica universal, EPROM de 1 KB y RAM de 64 bytes Intel 8741AH: microcontrolador esclavo de 8 bits con interfaz periférica universal, EPROM de 1 KB y RAM de 128 bytes Intel 8042: microcontrolador esclavo de 8 bits con interfaz periférica universal, 2 KB de ROM y 256 bytes de RAM Intel 8742: microcontrolador esclavo de 8 bits con interfaz periférica universal, EPROM de 2 KB y RAM de 128 bytes Intel 8742AH: microcontrolador esclavo de 8 bits con interfaz periférica universal, EPROM OTP de 2 KB, RAM de 256 bytes Intel 8243: Expansor de entrada y salida. Versión PLCC de 28 pines disponible en el primer trimestre de 1986. [7] Intel 8244: dispositivo de visualización de gráficos de uso general (ASIC NTSC/SECAM) Intel 8245 – Dispositivo de visualización de gráficos de propósito general (ASIC PAL) [8] Intel P8051 Familia MCS-51 :

8031 – Microcontrolador orientado al control de 8 bits 8032 – Microcontrolador orientado al control de 8 bits 8044 – Microcontrolador de 8 bits de alto rendimiento 8344 – Microcontrolador de 8 bits de alto rendimiento 8744 – Microcontrolador de 8 bits de alto rendimiento 8051 – Microcontrolador orientado al control de 8 bits 8052 – Microcontrolador orientado al control de 8 bits 8054 – Microcontrolador orientado al control de 8 bits 8058 – Microcontrolador orientado al control de 8 bits 8351 – Microcontrolador orientado al control de 8 bits 8352 – Microcontrolador orientado al control de 8 bits 8354 – Microcontrolador orientado al control de 8 bits 8358 – Microcontrolador orientado al control de 8 bits 8751 – Microcontrolador orientado al control de 8 bits 8752 – Microcontrolador orientado al control de 8 bits 8754 – Microcontrolador orientado al control de 8 bits 8758 – Microcontrolador orientado al control de 8 bits Familia MCS-151 :

80151 – Microcontrolador orientado al control de 8 bits y alto rendimiento 83151 – Microcontrolador orientado al control de 8 bits y alto rendimiento 87151 – Microcontrolador orientado al control de 8 bits y alto rendimiento 80152 – Microcontrolador orientado al control de 8 bits y alto rendimiento 83152 – Microcontrolador orientado al control de 8 bits y alto rendimiento Familia MCS-251 :

80251 – Microcontrolador de 8/16/32 bits 80252 – Microcontrolador de 8/16/32 bits 80452 – Microcontrolador de 8/16/32 bits 83251 – Microcontrolador de 8/16/32 bits 87251 – Microcontrolador de 8/16/32 bits 87253 – Microcontrolador de 8/16/32 bits 8061 – Microcontrolador de 16 bits (padre de la familia MCS-96 sin ROM con A/D, la mayoría vendido a Ford) 8094 – Microcontrolador de 16 bits (48 pines sin ROM y sin A/D) 8095 – Microcontrolador de 16 bits (48 pines sin ROM y con A/D) 8096 – Microcontrolador de 16 bits (68 pines sin ROM y sin A/D) 8097 – Microcontrolador de 16 bits (68 pines sin ROM y con A/D) 8394 – Microcontrolador de 16 bits (48 pines con ROM sin A/D) 8395 – Microcontrolador de 16 bits (48 pines con ROM y A/D) 8396 – Microcontrolador de 16 bits (68 pines con ROM sin A/D) 8397 – Microcontrolador de 16 bits (68 pines con ROM y A/D) 8794 – Microcontrolador de 16 bits (48 pines con EROM sin A/D) 8795 – Microcontrolador de 16 bits (48 pines con EROM y A/D) 8796 – Microcontrolador de 16 bits (68 pines con EROM sin A/D) 8797 – Microcontrolador de 16 bits (68 pines con EROM y A/D) 8098 – Microcontrolador de 16 bits 8398 – Microcontrolador de 16 bits 8798 – Microcontrolador de 16 bits 80196 – Microcontrolador de 16 bits 83196 – Microcontrolador de 16 bits 87196 – Microcontrolador de 16 bits 80296 – Microcontrolador de 16 bits

El procesador de rebanadas de bits

Familia 3000 Intel D3001 Intel D3002 Intel C3003 Estos componentes de fragmentación de bits, introducidos en el tercer trimestre de 1974, utilizaban transistores Schottky bipolares . Cada componente implementaba dos bits de una función de procesador ; los paquetes podían interconectarse para construir un procesador con cualquier longitud de palabra deseada.

Miembros de la familia 3000:

3001 – Unidad de microcontrol 3002 – Segmento de unidad lógica aritmética de 2 bits [9] 3003 – Generador de acarreo anticipado 3205 – Decodificador binario de alto rendimiento 1 de 8 3207 – Desplazador y controlador de nivel bipolar a MOS cuádruple 3208 – Amplificador y pestillo Hex Sense para memorias MOS 3210 – Cambiador de nivel TTL a MOS y controlador de reloj de alto voltaje 3211 – Cambiador de nivel de ECL a MOS y controlador de reloj de alto voltaje 3212 – Buffer de bloqueo multimodo 3214 – Unidad de control de interrupciones 3216 – Controlador de bus bidireccional inversor paralelo 3222 – Controlador de actualización para DRAM NMOS 4K (4096 B) 3226 – Controlador de bus bidireccional inversor paralelo 3232 – Multiplexor de direcciones y contador de actualización para DRAM de 4K 3242 – Multiplexor de direcciones y contador de actualización para DRAM de 16 K (16 × 1024 B) 3245 – Desplazador y controlador de nivel TTL a MOS bipolar cuádruple para 4K 3246 – Desplazador y controlador de nivel ECL a MOS bipolar cuádruple para 4K 3404 – Latch de 6 bits de alto rendimiento 3408 – Amplificador y pestillo Hex Sense para memorias MOS 3505 – Procesador de próxima generación Ancho de bus 2 n bits de datos/dirección (dependiendo del número n de porciones utilizadas)

El16 bitsProcesadores: familia MCS-86 Intel D8086

8086 Introducido el 8 de junio de 1978 Frecuencias de reloj:5 MHz, 0,33 MIPS [6] 8 MHz, 0,66 MIP/S 10 MHz, 0,75 MIPS La memoria se divide en bancos pares e impares. Accede a ambos bancos simultáneamente para leer 16 bits de datos en un ciclo de reloj. Ancho del bus de datos: 16 bits, bus de direcciones: 20 bits 29.000 transistores a 3 μm Memoria direccionable 1 megabyte (1024 2 B) Hasta 10 veces el rendimiento del 8080 Se utilizó por primera vez en las computadoras compatibles con IBM PC Compaq Deskpro. Más tarde se utilizó en computadoras portátiles y en los modelos 25 y 30 de IBM PS/2 . También se utilizó en el AT&T PC6300 / Olivetti M24 , un popular modelo compatible con IBM PC (anterior a la línea IBM PS/2) Se utilizaron registros de segmento para acceder a más de 64 KB de datos a la vez, lo que muchos programadores denunciaron que dificultaba excesivamente su trabajo. [ cita requerida La primera CPU x86 Posteriormente se le cambió el nombre a iAPX 86 [10] Intel D8088

8088 Introducido el 1 de junio de 1979 Frecuencias de reloj:4,77 MHz, 0,33 MIPS 8 MHz, 0,66 MIPS [6] Arquitectura interna de 16 bits Ancho del bus de datos externo: 8 bits, bus de direcciones: 20 bits 29.000 transistores a 3 μm Memoria direccionable 1 megabyte Idéntico al 8086 excepto por su bus externo de 8 bits (de ahí un 8 en lugar de un 6 al final); unidad de ejecución (EU) idéntica, unidad de interfaz de bus (BIU) diferente [10] Utilizado en IBM PC y PC-XT y compatibles Posteriormente se le cambió el nombre a iAPX 88 [10] Intel C80186 de 6 MHz Introducido en 1982 Frecuencias de reloj 55.000 transistores Incluía dos temporizadores, un controlador DMA y un controlador de interrupciones en el chip además del procesador (estos estaban en direcciones fijas que diferían de las del IBM PC, aunque lo usaban varios proveedores de PC compatibles, como la empresa australiana Cleveland) Se agregaron algunos códigos de operación y excepciones al diseño 8086, conjunto de instrucciones idéntico al 8086 y 8088Atado, entrar, salir DENTRO, FUERA IMUL imm, PUSH imm, PUSHA, POPA RCL/RCR/ROL/ROR/SHL/SHR/SAL/SAR reg, inm El cálculo de direcciones y las operaciones de cambio son más rápidas que en 8086 Se utiliza principalmente en aplicaciones integradas: controladores, sistemas de puntos de venta, terminales y similares. Se utiliza en varias computadoras DOS no compatibles con PC, incluidas RM Nimbus , Tandy 2000 y el servidor CP/M 86 Televideo PM16 Posteriormente renombrado como iAPX 186 Una versión del 80186 con un bus de datos externo de 8 bits Posteriormente se le cambió el nombre a iAPX 188. Intel C80286 de 6 MHz Introducido el 1 de febrero de 1982 Frecuencias de reloj:6 MHz, 0,9 MIPS 8 MHz, 10 MHz, 1,5 MIPS 12,5 MHz, 2,66 MIPS Disponibles 16 MHz, 20 MHz y 25 MHz. Ancho del bus de datos: 16 bits, bus de direcciones: 24 bits Incluye hardware de protección de memoria para soportar sistemas operativos multitarea con espacio de direcciones por proceso. 134.000 transistores de 1,5 μm Memoria direccionable 16 MB Se agregaron funciones de modo protegido al 8086 con esencialmente el mismo conjunto de instrucciones 3–6 veces el rendimiento del 8086 Ampliamente utilizado en IBM PC AT y clones AT contemporáneos.

32 bitsProcesadores: los microprocesadores no x86 Presentado el 1 de enero de 1981 como el primer microprocesador de 32 bits de Intel. CPU multichip Arquitectura de objetos/capacidades Primitivos del sistema operativo microcodificados Un espacio de dirección virtual de un terabyte Soporte de hardware para tolerancia a fallos Procesador general de datos (GDP) de dos chips, compuesto por 43201 y 43202 43203 El procesador de interfaz (IP) se conecta al subsistema de E/S La unidad de interfaz de bus (BIU) 43204 simplifica la construcción de sistemas multiprocesador 43205 Unidad de control de memoria (MCU) Rutas de bases de datos internas de la unidad de arquitectura y ejecución: 32 bits Frecuencias de reloj: Introducido el 5 de abril de 1988 Arquitectura de 32 bits similar a RISC Se utiliza predominantemente en sistemas integrados. Desarrollado a partir del procesador de capacidad desarrollado para la empresa conjunta BiiN con Siemens Muchas variantes identificadas por sufijos de dos letras Introducido el 23 de agosto de 2000 Microprocesador RISC de 32 bits basado en la arquitectura ARM Muchas variantes, como los procesadores de aplicaciones PXA2xx, los procesadores de E/S IOP3xx y los procesadores de red IXP2xxx e IXP4xx

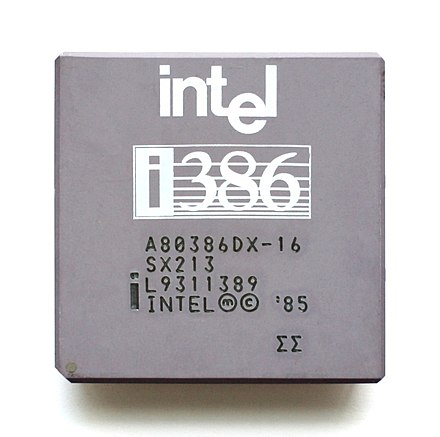

32 bitsProcesadores: la gama 80386 Intel 80386DX Intel 80386DX con procesador matemático Intel 387 Introducido el 17 de octubre de 1985 Frecuencias de reloj:16 MHz, 5 MIPS 20 MHz, 6 a 7 MIPS, introducido el 16 de febrero de 1987 25 MHz, 7,5 MIPS, introducido el 4 de abril de 1988 33 MHz, 9,9 MIPS (9,4 SPECint92 en Compaq/i 16 KB L2), presentado el 10 de abril de 1989 Ancho del bus de datos: 32 bits, bus de direcciones: 32 bits 275.000 transistores a 1 μm Memoria direccionable 4 GB (4 × 1024 3 B) Memoria virtual 64 TB (64 × 1024 4 B) [11] [12] Primer chip x86 que maneja conjuntos de datos de 32 bits Se modificó y amplió la compatibilidad con la protección de memoria, que incluía memoria virtual paginada y modo virtual-86, características que Xenix y Unix necesitaban en ese momento . Esta capacidad de memoria impulsó el desarrollo y la disponibilidad de OS/2 y es un requisito fundamental para los sistemas operativos modernos como Linux , Windows y macOS. Compaq lo utilizó por primera vez en el Deskpro 386. Se utiliza en computadoras de escritorio. A diferencia de la convención de nombres DX de los chips 486, no tenía un coprocesador matemático. Posteriormente renombrado Intel386 DX Introducido el 16 de junio de 1988 Frecuencias de reloj:16 MHz, 2,5 MIPS 20 MHz, 3,1 MIPS, introducido el 25 de enero de 1989 25 MHz, 3,9 MIPS, introducido el 25 de enero de 1989 33 MHz, 5,1 MIPS, introducido el 26 de octubre de 1992 Arquitectura interna de 32 bits Ancho del bus de datos externo: 16 bits Ancho del bus de dirección externa: 24 bits 275.000 transistores a 1 μm Memoria direccionable 16 MB Memoria virtual 64 TB [11] Los buses más estrechos permiten un procesamiento de 32 bits de bajo costo Se utiliza en computadoras portátiles y de escritorio de nivel básico. Sin coprocesador matemático Ningún software comercial utilizó el modo protegido o el almacenamiento virtual durante muchos años Posteriormente renombrado Intel386 SX El Intel i376 es una versión integrada del i386SX. Introducido el 16 de enero de 1989; descontinuado el 15 de junio de 2001 Variante del 386SX destinada a sistemas integrados Sin "modo real", se inicia directamente en "modo protegido" Reemplazado por el mucho más exitoso 80386EX de 1994 Introducido el 15 de octubre de 1990 Frecuencias de reloj:20 MHz, 4,21 MIPS 25 MHz, 5,3 MIPS, introducido el 30 de septiembre de 1991 Arquitectura interna de 32 bits Ancho de bus externo: 16 bits 855.000 transistores a 1 μm Memoria direccionable 4 GB Memoria virtual 64 TB [11] Primer chip fabricado específicamente para ordenadores portátiles debido al bajo consumo de energía del chip. Altamente integrado, incluye controladores de caché, bus y memoria. Intel 80386EX Introducido en agosto de 1994 Variante del 80386SX destinada a sistemas integrados Núcleo estático (es decir, puede funcionar tan lentamente (y, por lo tanto, con tanta eficiencia energética) como se desee) hasta detenerse por completo Periféricos en chip: Significativamente más exitoso que el 80376 Se utiliza a bordo de varios satélites y microsatélites en órbita. Utilizado en el proyecto FlightLinux de la NASA

Procesadores de 32 bits: la gama 80486 Intel 80486DX 33 MHz Introducido el 10 de abril de 1989 Frecuencias de reloj:25 MHz, 20 MIPS (16,8 SPECint92, 7,40 SPECfp92) 33 MHz, 27 MIPS (22,4 SPECint92 en Micronics M4P 128 KB L2), presentado el 7 de mayo de 1990 50 MHz, 41 MIPS (33,4 SPECint92, 14,5 SPECfp92 en Compaq/50L 256 KB L2), presentado el 24 de junio de 1991 Ancho de bus: 32 bits 1,2 millones de transistores a 1 μm; los 50 MHz estaban a 0,8 μm Memoria direccionable 4 GB Memoria virtual 64 TB [11] Caché de nivel 1 de 8 KB en el chipCoprocesador matemático en chip Rendimiento 50x del 8088 Oficialmente llamado Intel486 DX Se utiliza en informática de escritorio y servidores. Familia 4 modelo 1 Intel 80486SX 33 MHz Introducido el 22 de abril de 1991 Frecuencias de reloj:16 MHz, 13 MIPS 20 MHz, 16,5 MIPS, introducido el 16 de septiembre de 1991 25 MHz, 20 MIPS (12 SPECint92), introducido el 16 de septiembre de 1991 33 MHz, 27 MIPS (15,86 SPECint92), introducido el 21 de septiembre de 1992 Ancho de bus: 32 bits 1,185 millones de transistores de 1 μm y 900.000 de 0,8 μm Memoria direccionable 4 GB Memoria virtual 64 TB [11] Idéntico en diseño al 486DX pero sin coprocesador matemático. La primera versión fue un 80486DX con coprocesador matemático deshabilitado en el chip y una configuración de pines diferente. Si el usuario necesitaba capacidades de coprocesador matemático, debía agregar 487SX, que en realidad era un 486DX con una configuración de pines diferente para evitar que el usuario instalara un 486DX en lugar de un 487SX, por lo que con esta configuración 486SX+487SX tenías 2 CPU idénticas con solo 1 efectivamente encendida Oficialmente llamado Intel486 SX Se utiliza en computadoras de escritorio de bajo costo con CPU 486, así como también ampliamente en computadoras móviles de bajo costo. Actualizable con el procesador Intel OverDrive Familia 4 modelo 2 Intel 80486DX2 de 66 MHz Introducido el 3 de marzo de 1992 Funciona al doble de velocidad que el bus externo (FSB) Zócalo 3 Frecuencias de reloj:40 MHz 50 MHz, 41 MIPS 66 MHz, 54 MIP/S Oficialmente llamado Intel486 DX2 Familia 4 modelo 3 Intel 80486SL Introducido el 9 de noviembre de 1992 Frecuencias de reloj:20 MHz, 15,4 MIPS 25 MHz, 19 MIPS 33 MHz, 25 MIPS Ancho de bus: 32 bits 1,4 millones de transistores de 0,8 μm Memoria direccionable 4 GB Memoria virtual 64 TB Oficialmente llamado Intel486 SL Se utiliza en ordenadores portátiles. Familia 4 modelo 4 Intel 80486DX4 100 MHz Introducido el 7 de marzo de 1994 Frecuencias de reloj:75 MHz, 53 MIPS (41,3 SPECint92, 20,1 SPECfp92 en Micronics M4P 256 KB L2) 100 MHz, 70,7 MIPS (54,59 SPECint92, 26,91 SPECfp92 en Micronics M4P 256 KB L2) 1,6 millones de transistores de 0,6 μm Ancho de bus: 32 bits Memoria direccionable 4 GB Memoria virtual 64 TB Paquete PGA de 168 pines para socket 3 , o paquete de 208 ftP cuadrados Oficialmente llamado Intel486 DX4 Se utiliza en computadoras de escritorio de nivel básico de alto rendimiento y portátiles económicos. Familia 4 modelo 8

Procesadores de 32 bits:P5microarquitectura Intel Pentium P5 (A80501) 60 MHz, sin GoldCap Intel Pentium P5 (A80501) 66 MHz, con GoldCap Introducido el 22 de marzo de 1993 Ancho de bus: 64 bits Frecuencia de reloj del bus del sistema: 60 o 66 MHz Bus de direcciones: 32 bits Memoria direccionable 4 GB Memoria virtual 64 TB Arquitectura superescalar Funciona con 3,3 voltios (excepto la primera generación "P5") Utilizado en computadoras de escritorio 8 KB de caché de instrucciones 8 KB de caché de datos Tecnología de proceso P5 – 0,8 μmIntroducido el 22 de marzo de 1993 3,1 millones de transistores El único Pentium que funciona con 5 voltios Paquete PGA de 273 pines para socket 4 Dimensiones del paquete 2,16 pulgadas × 2,16 pulgadas Familia 5 modelo 1 Variantes60 MHz, 100 MIPS (70,4 SPECint92, 55,1 SPECfp92 en Xpress 256 KB L2) 66 MHz, 112 MIPS (77,9 SPECint92, 63,6 SPECfp92 en Xpress 256 KB L2) P54 – Tecnología de proceso de 0,6 μm Paquete PGA de 296/320 pines para socket 5 3,2 millones de transistores Variantes75 MHz, 126,5 MIPS (2,31 SPECint95, 2,02 SPECfp95 en Gateway P5 256K L2)Introducido el 10 de octubre de 1994 90, 100 MHz, 149,8 y 166,3 MIPS respectivamente (2,74 SPECint95, 2,39 SPECfp95 en Gateway P5 256K L2 y 3,30 SPECint95, 2,59 SPECfp95 en Xpress 1ML2 respectivamente)Introducido el 7 de marzo de 1994 P54CQS – Tecnología de proceso de 0,35 μm Paquete PGA de 296/320 pines para socket 5 3,2 millones de transistores Variantes120 MHz, 203 MIPS (3,72 SPECint95, 2,81 SPECfp95 en Xpress 1 MB L2)Introducido el 27 de marzo de 1995 Intel Pentium P54 133 MHz Tecnología de proceso de 0,35 μm 3,3 millones de transistores Tamaño de matriz de 90 mm 2 Familia 5 modelo 2 Variantes Paquete PGA de 296/320 pines para socket 5 133 MHz, 218,9 MIPS (4,14 SPECint95, 3,12 SPECfp95 en Xpress 1 MB L2)Introducido el 12 de junio de 1995 150, 166 MHz, 230 y 247 MIPS respectivamenteIntroducido el 4 de enero de 1996 Paquete PGA de 296/321 pines para socket 7 200 MHz, 270 MIPS (5,47 SPECint95, 3,68 SPECfp95)Introducido el 10 de junio de 1996 Intel Pentium P55C 166 MHz Tecnología de proceso P55C – 0,35 μmIntroducido el 8 de enero de 1997 Compatibilidad con Intel MMX (conjunto de instrucciones) Paquete PGA (matriz de cuadrícula de pines) de 296/321 pines para socket 7 Caché de instrucciones L1 de 16 KB Caché de datos de 16 KB 4,5 millones de transistores Frecuencia de reloj del bus del sistema: 66 MHz El P55C básico es el modelo 4 de la familia 5, los móviles son los modelos 7 y 8 de la familia 5 Variantes166, 200 MHz introducido el 8 de enero de 1997 233 MHz introducido el 2 de junio de 1997 133 MHz (móvil) 166, 266 MHz (móvil) introducido el 12 de enero de 1998 200, 233 MHz (móvil) introducido el 8 de septiembre de 1997 300 MHz (móvil) introducido el 7 de enero de 1999

32 bitsprocesadores:P6/Pentium Mmicroarquitectura Intel Pentium Pro 200 MHz Introducido el 1 de noviembre de 1995 Módulo multichip (2 matrices) Precursor del Pentium II y III Se utiliza principalmente en sistemas de servidor. Paquete de procesador Socket 8 (387 pines; Dual SPGA)5,5 millones de transistores Familia 6 modelo 1 Tecnología de proceso de 0,6 μm 16 KB de caché L1 Caché L2 integrada de 256 KBFrecuencia de reloj del bus del sistema de 60 MHz Variantes Tecnología de proceso de 0,35 μm (dos matrices, una CPU de 0,35 μm con caché L2 de 0,6 μm)5,5 millones de transistores Caché L2 integrada de 512 KB o 256 KB Frecuencia de reloj del bus del sistema de 60 o 66 MHz Variantes150 MHz (velocidad de reloj de bus de 60 MHz, caché de 256 KB y 0,6 μm) introducido el 1 de noviembre de 1995 166 MHz (frecuencia de reloj de bus de 66 MHz, caché de 0,35 μm y 512 KB) introducido el 1 de noviembre de 1995 180 MHz (velocidad de reloj de bus de 60 MHz, caché de 256 KB y 0,6 μm) introducido el 1 de noviembre de 1995 200 MHz (velocidad de reloj de bus de 66 MHz, caché de 256 KB y 0,6 μm) introducido el 1 de noviembre de 1995 200 MHz (velocidad de reloj de bus de 66 MHz, caché de 0,35 μm de 512 KB) introducido el 1 de noviembre de 1995 200 MHz (frecuencia de reloj de bus de 66 MHz, 1 MB de caché de 0,35 μm) introducido el 18 de agosto de 1997 Introducido el 7 de mayo de 1997 Pentium Pro con MMX y rendimiento mejorado de 16 bits Paquete de procesador de ranura 1 (SEC) de 242 pinesPines de identificación de voltaje 7,5 millones de transistores 32 KB de caché L1 512 KB 1 ⁄ 2 El Pentium II móvil de rendimiento mejorado (nombre en código Dixon) tenía una caché L2 de 256 KB de velocidad completa. Klamath – Tecnología de proceso de 0,35 μm (233, 266, 300 MHz)Frecuencia de reloj del bus del sistema de 66 MHz Familia 6 modelo 3 Variantes233, 266, 300 MHz introducido el 7 de mayo de 1997 Deschutes – Tecnología de proceso de 0,25 μm (333, 350, 400, 450 MHz)Introducido el 26 de enero de 1998 Frecuencia de reloj del bus del sistema de 66 MHz ( variante de 333 MHz ), frecuencia de reloj del bus del sistema de 100 MHz para todos los modelos posteriores Familia 6 modelo 5 Variantes333 MHz introducido el 26 de enero de 1998 350, 400 MHz introducido el 15 de abril de 1998 450 MHz introducido el 24 de agosto de 1998 233, 266 MHz (móvil) introducido el 2 de abril de 1998 Procesador Pentium II Overdrive de 333 MHz para Socket 8 Presentado el 10 de agosto de 1998 300 MHz (móvil) introducido el 9 de septiembre de 1998 333 MHz (móvil) introducido el 25 de enero de 1999 Covington – Tecnología de proceso de 0,25 μm Introducido el 15 de abril de 1998 Ranura 1 de 242 pines SEPP (paquete de procesador de borde único)7,5 millones de transistores Frecuencia de reloj del bus del sistema de 66 MHz Ranura 1 32 KB de caché L1 Sin caché L2 Variantes266 MHz introducido el 15 de abril de 1998 300 MHz introducido el 9 de junio de 1998 Mendocino – Tecnología de proceso de 0,25 μm Introducido el 24 de agosto de 1998 Ranura 1 de 242 pines SEPP (paquete de procesador de borde único), paquete PPGA Socket 370 19 millones de transistores Frecuencia de reloj del bus del sistema de 66 MHz Ranura 1, zócalo 370 32 KB de caché L1 128 KB de caché integrada Familia 6 modelo 6 Variantes300, 333 MHz introducido el 24 de agosto de 1998 366, 400 MHz introducido el 4 de enero de 1999 433 MHz introducido el 22 de marzo de 1999 466 MHz 500 MHz introducido el 2 de agosto de 1999 533 MHz introducido el 4 de enero de 2000 266 MHz (móvil) 300 MHz (móvil) 333 MHz (móvil) introducido el 5 de abril de 1999 366 MHz (móvil) 400 MHz (móvil) 433 MHz (móvil) 450 MHz (móvil) introducido el 14 de febrero de 2000 466 MHz (móvil) 500 MHz (móvil) introducido el 14 de febrero de 2000 Pentium II Xeon (entrada cronológica)

Introducido el 29 de junio de 1998 Katmai – Tecnología de proceso de 0,25 μm Introducido el 26 de febrero de 1999 PII mejorado (es decir, núcleo basado en P6) que ahora incluye extensiones Streaming SIMD (SSE) 9,5 millones de transistores 512 KB (512 × 1024 B) 1 ⁄ 2 Paquete de procesador SECC2 (cartucho de contacto de borde único 2) con ranura 1 de 242 pines Frecuencia de reloj del bus del sistema: 100 MHz, 133 MHz (modelos B) Ranura 1 Familia 6 modelo 7 Variantes450, 500 MHz introducido el 26 de febrero de 1999 550 MHz introducido el 17 de mayo de 1999 La frecuencia de 600 MHz se introdujo el 2 de agosto de 1999 Se introdujeron los modelos 533 y 600 MHz (frecuencia de reloj de bus de 133 MHz) el 27 de septiembre de 1999 Mina de cobre : tecnología de proceso de 0,18 μm Introducido el 25 de octubre de 1999 28,1 millones de transistores 256 KB (512 × 1024 B) Caché L2 de transferencia avanzada (integrada) Paquete de procesador SECC2 (cartucho de contacto de borde único 2) con ranura 1 de 242 pines, paquete FC-PGA (matriz de cuadrícula de pines de chip invertido) de 370 pines Frecuencia de reloj del bus del sistema: 100 MHz (modelos E), 133 MHz (modelos EB) Ranura 1, zócalo 370 Familia 6 modelo 8 Variantes500 MHz (frecuencia de reloj de bus de 100 MHz) 533 MHz 550 MHz (frecuencia de reloj de bus de 100 MHz) 600 MHz 600 MHz (frecuencia de reloj de bus de 100 MHz) 650 MHz (frecuencia de reloj de bus de 100 MHz) introducido el 25 de octubre de 1999 La frecuencia de 667 MHz se introdujo el 25 de octubre de 1999 700 MHz (frecuencia de reloj de bus de 100 MHz) introducido el 25 de octubre de 1999 La frecuencia de 733 MHz se introdujo el 25 de octubre de 1999 750, 800 MHz (frecuencia de reloj de bus de 100 MHz) introducido el 20 de diciembre de 1999 850 MHz (frecuencia de reloj de bus de 100 MHz) introducido el 20 de marzo de 2000 La frecuencia de 866 MHz se introdujo el 20 de marzo de 2000 La frecuencia de 933 MHz se introdujo el 24 de mayo de 2000 1000 MHz introducido el 8 de marzo de 2000 (no ampliamente disponible en el momento del lanzamiento) 1100 MHz 1133 MHz (primera versión retirada del mercado, relanzada posteriormente) 400, 450, 500 MHz (móvil) introducido el 25 de octubre de 1999 600, 650 MHz (móvil) introducido el 18 de enero de 2000 700 MHz (móvil) introducido el 24 de abril de 2000 750 MHz (móvil) introducido el 19 de junio de 2000 800, 850 MHz (móvil) introducido el 25 de septiembre de 2000 900, 1000 MHz (móvil) introducido el 19 de marzo de 2001 Tualatin – Tecnología de proceso de 0,13 μm Introducido en julio de 2001 28,1 millones de transistores 32 KB (32 × 1024 B) caché L1 Caché L2 de transferencia avanzada de 256 KB o 512 KB (integrada) Paquete FC-PGA2 (matriz de cuadrícula de pines con chip invertido) de 370 pines Frecuencia de reloj del bus del sistema de 133 MHz Zócalo 370 Familia 6 modelo 11 Variantes1133 MHz (256 KB L2) 1133 MHz (512 KB L2) 1200 MHz 1266 MHz (512 KB L2) 1333 MHz 1400 MHz (512 KB L2)

Pentium IIXeóny Pentium III Xeon Información personal XeonVariantes400 MHz introducido el 29 de junio de 1998 450 MHz (caché L2 de 512 KB) introducido el 6 de octubre de 1998 450 MHz (caché L2 de 1 MB y 2 MB) introducido el 5 de enero de 1999 PIII XeonIntroducido el 25 de octubre de 1999 9,5 millones de transistores a 0,25 μm o 28 millones a 0,18 μm La caché L2 es de 256 KB, 1 MB o 2 MB de caché de transferencia avanzada (integrada) El estilo del paquete del procesador es cartucho de contacto de borde único (SECC2) o SC330 Frecuencia de reloj del bus del sistema: 133 MHz (caché L2 de 256 KB) o 100 MHz (caché L2 de 1 a 2 MB) Ancho del bus del sistema: 64 bits Memoria direccionable: 64 GB Se utiliza en servidores y estaciones de trabajo bidireccionales (256 KB L2) o servidores de 4 y 8 vías (1–2 MB L2) Familia 6 modelo 10 Variantes500 MHz ( proceso de 0,25 μm ) introducido el 17 de marzo de 1999 550 MHz (proceso de 0,25 μm) introducido el 23 de agosto de 1999 600 MHz ( proceso de 0,18 μm , caché L2 de 256 KB) introducido el 25 de octubre de 1999 667 MHz (proceso de 0,18 μm, caché L2 de 256 KB) introducido el 25 de octubre de 1999 733 MHz (proceso de 0,18 μm, caché L2 de 256 KB) introducido el 25 de octubre de 1999 800 MHz (proceso de 0,18 μm, caché L2 de 256 KB) introducido el 12 de enero de 2000 866 MHz (proceso de 0,18 μm, caché L2 de 256 KB) introducido el 10 de abril de 2000 933 MHz (proceso de 0,18 μm, caché L2 de 256 KB) 1000 MHz (proceso de 0,18 μm, caché L2 de 256 KB) introducido el 22 de agosto de 2000 700 MHz (proceso de 0,18 μm, caché L2 de 1 a 2 MB) introducido el 22 de mayo de 2000 Celeron (Basado en Pentium III Coppermine)Tecnología de proceso de Coppermine-128, 0,18 μmIntroducido en marzo de 2000 Extensiones SIMD de transmisión continua (SSE)Paquete de procesador Socket 370 , FC-PGA 28,1 millones de transistores Frecuencia de reloj del bus del sistema de 66 MHz, frecuencia de reloj del bus del sistema de 100 MHz a partir del 3 de enero de 2001 32 KB de caché L1 128 KB de caché L2 de transferencia avanzada Familia 6 modelo 8 Variantes533 MHz 566 MHz 600 MHz 633, 667, 700 MHz introducidos el 26 de junio de 2000 733, 766 MHz introducido el 13 de noviembre de 2000 La frecuencia de 800 MHz se introdujo el 3 de enero de 2001 La frecuencia de 850 MHz se introdujo el 9 de abril de 2001 La frecuencia de 900 MHz se introdujo el 2 de julio de 2001 950, 1000, 1100 MHz introducidos el 31 de agosto de 2001 550 MHz (móvil) 600, 650 MHz (móvil) introducido el 19 de junio de 2000 700 MHz (móvil) introducido el 25 de septiembre de 2000 750 MHz (móvil) introducido el 19 de marzo de 2001 800 MHz (móvil) 850 MHz (móvil) introducido el 2 de julio de 2001 600 MHz (móvil LV) 500 MHz (ULV Mobile) introducido el 30 de enero de 2001 600 MHz (móvil ULV) XScale (entrada cronológica – arquitectura no x86)

Introducido el 23 de agosto de 2000 Pentium 4 (no 4EE, 4E, 4F), Itanium, Xeon basado en P4, Itanium 2 (entradas cronológicas)

Introducido abril de 2000 – julio de 2002

Pentium III basado en Tualatin Tualatin – Tecnología de proceso de 0,13 μm 32 KB de caché L1 512 KB de caché L2 de transferencia avanzada Frecuencia de reloj del bus del sistema de 133 MHz Zócalo 370 Variantes1,0 GHz 1,13 GHz 1,26 GHz 1,4 GHz Celeron (Basado en Pentium III Tualatin)Tualatin Celeron: tecnología de proceso de 0,13 μm 32 KB de caché L1 256 KB de caché L2 de transferencia avanzada Frecuencia de reloj del bus del sistema de 100 MHz Zócalo 370 Familia 6 modelo 11 Variantes1,0 GHz 1,1 GHz 1,2 GHz 1,3 GHz 1,4 GHz Tecnología de proceso Banias 0,13 μm Introducido en marzo de 2003 64 KB de caché L1 1 MB de caché L2 (integrada) Basado en el núcleo Pentium III, con instrucciones SSE2 SIMD y una canalización más profunda 77 millones de transistores Paquete de procesador Micro-FCPGA , Micro-FCBGA El corazón del sistema móvil Intel Centrino Bus de sistema de estilo NetBurst de 400 MHz Familia 6 modelo 9 Variantes900 MHz (voltaje ultra bajo) 1,0 GHz (voltaje ultrabajo) 1,1 GHz (bajo voltaje) 1,2 GHz (bajo voltaje) 1,3 GHz 1,4 GHz 1,5 GHz 1,6 GHz 1,7 GHz Tecnología de proceso Dothan de 0,09 μm ( 90 nm )Introducido en mayo de 2004 2 MB de caché L2 140 millones de transistores Unidad de precarga de datos revisada Bus de sistema de estilo NetBurst de 400 MHz Potencia térmica total de 21 WFamilia 6 modelo 13 Variantes1,00 GHz (Pentium M 723) (voltaje ultrabajo, TDP de 5 W) 1,10 GHz (Pentium M 733) (voltaje ultrabajo, TDP de 5 W) 1,20 GHz (Pentium M 753) (voltaje ultrabajo, TDP de 5 W) 1,30 GHz (Pentium M 718) (bajo voltaje, TDP de 10 W) 1,40 GHz (Pentium M 738) (bajo voltaje, TDP de 10 W) 1,50 GHz (Pentium M 758) (bajo voltaje, TDP de 10 W) 1,60 GHz (Pentium M 778) (bajo voltaje, TDP de 10 W) 1,40 GHz (Pentium M 710) 1,50 GHz (Pentium M 715) 1,60 GHz (Pentium M 725) 1,70 GHz (Pentium M 735) 1,80 GHz (Pentium M 745) 2,00 GHz (Pentium M 755) 2,10 GHz (Pentium M 765) Dothan 533 0,09 μm ( 90 nm ) Introducido en el primer trimestre de 2005 Igual que Dothan excepto con un bus de sistema estilo NetBurst de 533 MHz y TDP de 27 W Variantes1,60 GHz (Pentium M 730) 1,73 GHz (Pentium M 740) 1,86 GHz (Pentium M 750) 2,00 GHz (Pentium M 760) 2,13 GHz (Pentium M 770) 2,26 GHz (Pentium M 780) Tecnología de proceso Stealey de 0,09 μm ( 90 nm )Introducido en el segundo trimestre de 2007 512 KB L2, 3 W TDP Variantes600 MHz (A100) 800 MHz (A110) Banias -512 0,13 μm Introducido en marzo de 2003 64 KB de caché L1 Caché L2 de 512 KB (integrada) Instrucciones SIMD SSE2 Sin tecnología SpeedStep , no forma parte del paquete ' Centrino ' Familia 6 modelo 9 Variantes310, 1,20 GHz 320, 1,30 GHz 330, 1,40 GHz 340, 1,50 GHz Dothan -1024 de 90 nm 64 KB de caché L1 1 MB de caché L2 (integrada) Instrucciones SIMD SSE2 Sin tecnología SpeedStep , no forma parte del paquete ' Centrino ' Variantes350, 1,30 GHz 350 J, 1,30 GHz, con bit de desactivación de ejecución 360, 1,40 GHz 360J, 1,40 GHz, con bit de desactivación de ejecución 370, 1,50 GHz, con bit de desactivación de ejecuciónFamilia 6, Modelo 13, Paso 8 [13] 380, 1,60 GHz, con bit de desactivación de ejecución 390, 1,70 GHz, con bit de desactivación de ejecución Yonah 65 nm 64 KB de caché L1 1 MB de caché L2 (integrada) Instrucciones SIMD SSE3 , bus frontal de 533 MHz, bit de desactivación de ejecuciónSin tecnología SpeedStep , no forma parte del paquete ' Centrino ' Variantes410, 1,46 GHz 420, 1,60 GHz, 423, 1,06 GHz (voltaje ultrabajo) 430, 1,73 GHz 440, 1,86 GHz 443, 1,20 GHz (voltaje ultrabajo) 450, 2,00 GHz Yonah de 65 nm ) Introducido en enero de 2006 Bus frontal de 533/667 MHz2 MB (compartido en Duo) caché L2 Instrucciones SIMD SSE3 31 W TDP (versiones T) Familia 6, modelo 14 Variantes:Intel Core Duo T2700 2,33 GHz Intel Core Duo T2600 2,16 GHz Intel Core Duo T2500 de 2 GHz Intel Core Duo T2450 de 2 GHz Intel Core Duo T2400 1,83 GHz Intel Core Duo T2300 1,66 GHz Intel Core Duo T2050 1,6 GHz Intel Core Duo T2300e 1,66 GHz Intel Core Duo T2080 1,73 GHz Intel Core Duo L2500 1,83 GHz (bajo voltaje, 15 W TDP ) Intel Core Duo L2400 1,66 GHz (bajo voltaje, 15 W TDP) Intel Core Duo L2300 1,5 GHz (bajo voltaje, 15 W TDP) Intel Core Duo U2500 1,2 GHz (voltaje ultrabajo, TDP de 9 W) Intel Core Solo T1350 1,86 GHz (FSB 533) Intel Core Solo T1300 1,66 GHz Intel Core Solo T1200 1,5 GHz [14]

Doble núcleoXeónVuelta al cole Sossaman de 65 nm ) Introducido en marzo de 2006 Basado en el núcleo Yonah , con instrucciones SSE3 SIMD Bus frontal de 667 MHz2 MB de caché L2 compartida Variantes

Procesadores de 32 bits:Explosión de redmicroarquitectura Tecnología de proceso de 0,18 μm (1,40 y 1,50 GHz)Introducido el 20 de noviembre de 2000 La caché L2 era una caché de transferencia avanzada de 256 KB (integrada) El estilo del paquete del procesador era PGA423, PGA478 System bus clock rate 400 MHz SSE2 SIMD Extensions 42 million transistors Used in desktops and entry-level workstations 0.18 μm process technology (1.7 GHz)Introduced April 23, 2001 See the 1.4 and 1.5 chips for details 0.18 μm process technology (1.6 and 1.8 GHz)Introduced July 2, 2001 See 1.4 and 1.5 chips for details Core voltage is 1.15 volts in Maximum Performance Mode; 1.05 volts in battery optimized mode Power <1 watt in battery optimized mode Used in full-size and then light mobile PCs 0.18 μm process technology Willamette (1.9 and 2.0 GHz)Introduced August 27, 2001 See 1.4 and 1.5 chips for details Family 15 model 1 Pentium 4 (2 GHz, 2.20 GHz)Introduced January 7, 2002 Pentium 4 (2.4 GHz) 0.13 μm process technology Northwood A (1.7, 1.8, 1.9, 2, 2.2, 2.4, 2.5, 2.6, 2.8 (OEM), 3.0 (OEM) GHz)Improved branch prediction and other microcodes tweaks 512 KB integrated L2 cache 55 million transistors 400 MHz system bus Family 15 model 2 0.13 μm process technology Northwood B (2.26, 2.4, 2.53, 2.66, 2.8, 3.06 GHz) 0.13 μm process technology Northwood C (2.4, 2.6, 2.8, 3.0, 3.2, 3.4 GHz)800 MHz system bus (all versions include Hyper-Threading) 6500 to 10,000 MIPS Itanium (chronological entry – new non-x86 architecture)

Official designation now Xeon; i.e. not "Pentium 4 Xeon" Xeon 1.4, 1.5, 1.7 GHzIntroduced May 21, 2001 L2 cache was 256 KB Advanced Transfer cache (integrated) Processor package Organic Land Grid Array 603 (OLGA 603) System bus clock rate 400 MHz SSE2 SIMD Extensions Used in high-performance and mid-range dual processor enabled workstations Xeon 2.0 GHz and up to 3.6 GHzIntroduced September 25, 2001 Itanium 2 (chronological entry – new non-x86 architecture)

Introduced July 2002 See main entry

Mobile Pentium 4-M 0.13 μm process technology 55 million transistors 512 KB L2 cache BUS a 400 MHz Supports up to 1 GB of DDR 266 MHz memory Supports ACPI 2.0 and APM 1.2 System Power Management 1.3–1.2 V (SpeedStep ) Power: 1.2 GHz 20.8 W, 1.6 GHz 30 W, 2.6 GHz 35 W Sleep power 5 W (1.2 V) Deeper sleep power 2.9 W (1.0 V)1.40 GHz – 23 April 2002 1.50 GHz – 23 April 2002 1.60 GHz – 4 March 2002 1.70 GHz – 4 March 2002 1.80 GHz – 23 April 2002 1.90 GHz – 24 June 2002 2.00 GHz – 24 June 2002 2.20 GHz – 16 September 2002 2.40 GHz – 14 January 2003 2.50 GHz – 16 April 2003 2.60 GHz – 11 June 2003 Introduced September 2003 "Extreme Edition" Built from the Xeon's "Gallatin" core, but with 2 MB cache

Pentium 4E Introduced February 2004 Built on 0.09 μm (90 nm ) process technology Prescott (2.4 A, 2.8, 2.8 A, 3.0, 3.2, 3.4, 3.6, 3.8 ) 1 MB L2 cache 533 MHz system bus (2.4A and 2.8A only) 800 MHz system bus (all other models) 125 million transistors in 1 MB models 169 million transistors in 2 MB models Hyper-Threading support is only available on CPUs using the 800 MHz system bus.The processor's integer instruction pipeline has been increased from 20 stages to 31 stages, which theoretically allows for even greater bandwidth 7500 to 11,000 MIPS LGA 775 versions are in the 5xx series (32-bit) and 5x 1 series (with Intel 64)The 6xx series has 2 MB L2 cache and Intel 64

64-bit processors: IA-64 Code name Merced Family 7 Released May 29, 2001 733 MHz and 800 MHz 2 MB cache All recalled and replaced by Itanium 2 Family 0x1F Released July 2002 900 MHz – 1.6 GHz McKinley 900 MHz 1.5 MB cache, Model 0x0 McKinley 1 GHz, 3 MB cache, Model 0x0 Deerfield 1 GHz, 1.5 MB cache, Model 0x1 Madison 1.3 GHz, 3 MB cache, Model 0x1 Madison 1.4 GHz, 4 MB cache, Model 0x1 Madison 1.5 GHz, 6 MB cache, Model 0x1 Madison 1.67 GHz, 9 MB cache, Model 0x1 Hondo 1.4 GHz, 4 MB cache, dual-core MCM, Model 0x1

64-bit processors: Intel 64 – NetBurst microarchitecture Intel Extended Memory 64 Technology Mostly compatible with AMD's AMD64 architecture Introduced Spring 2004, with the Pentium 4F (D0 and later P4 steppings)

Pentium 4F Prescott-2M built on 0.09 μm (90 nm ) process technology2.8–3.8 GHz (model numbers 6x 0) Introduced February 20, 2005 Same features as Prescott with the addition of: Cedar Mill built on 0.065 μm (65 nm ) process technology3.0–3.6 GHz (model numbers 6x 1) Introduced January 16, 2006 Die shrink of Prescott-2M Same features as Prescott-2M Family 15 Model 4 Dual-core microprocessorNo Hyper-Threading 800 (4×200) MHz front-side bus LGA 775 (Socket T)Smithfield (Pentium D) – 90 nm process technology (2.66–3.2 GHz)Introduced May 26, 2005 2.66–3.2 GHz (model numbers 805–840) 230 million transistors 1 MB × 2 (non-shared, 2 MB total) L2 cache Cache coherency between cores requires communication over the FSB Performance increase of 60% over similarly clocked Prescott 2.66 GHz (533 MHz FSB) Pentium D 805 introduced December 2005 Contains 2× Prescott dies in one package Family 15 Model 4 Presler 65 nm process technology (2.8–3.6 GHz)Introduced January 16, 2006 2.8–3.6 GHz (model numbers 915–960) 376 million transistors 2× 2 MB (non-shared, 4 MB total) L2 cache Contains 2× Cedar Mill dies in one package Variants Dual-core microprocessor Enabled Hyper-Threading 800 (4×200) MHz front-side bus Smithfield (Pentium Extreme Edition) – 90 nm process technology (3.2 GHz)VariantsPentium 840 EE – 3.20 GHz (2 × 1 MB L2) Presler (Pentium Extreme Edition) – 65 nm process technology (3.46, 3.73)2 MB × 2 (non-shared, 4 MB total) L2 cache Variants

Nocona Irwindale Cranford Introduced April 2005 MP version of Nocona Potomac Introduced April 2005 Cranford with 8 MB of L3 cache Paxville DP (2.8 GHz)Introduced October 10, 2005 Dual-core version of Irwindale, with 4 MB of L2 cache (2 MB per core) 2.8 GHz 800 MT/s front-side bus Paxville MP – 90 nm process (2.67 – 3.0 GHz)Introduced November 1, 2005 Dual-core Xeon 7000 series MP-capable version of Paxville DP 2 MB of L2 cache (1 MB per core) or 4 MB of L2 (2 MB per core) 667 MT/s FSB or 800 MT/s FSB Dempsey – 65 nm process (2.67–3.73 GHz)Introduced May 23, 2006 Dual-core Xeon 5000 series MP version of Presler 667 MT/s or 1066 MT/s FSB 4 MB of L2 cache (2 MB per core) LGA 771 (Socket J).Tulsa – 65 nm process (2.5–3.4 GHz)Introduced August 29, 2006 Dual-core Xeon 7100-series Improved version of Paxville MP 667 MT/s or 800 MT/s FSB

64-bit processors: Intel 64 – Core microarchitecture

Woodcrest 65 nm process technologyServer and Workstation CPU (SMP support for dual CPU system) Introduced June 26, 2006 Intel VT-x , multiple OS supportEIST (Enhanced Intel SpeedStep Technology) in 5140, 5148LV, 5150, 5160 Execute Disable Bit TXT, enhanced security hardware extensions SSSE3 SIMD instructionsiAMT2 (Intel Active Management Technology), remotely manage computers VariantsXeon 5160, 3.00 GHz (4 MB L2, 1333 MHz FSB, 80 W) Xeon 5150, 2.66 GHz (4 MB L2, 1333 MHz FSB, 65 W) Xeon 5140, 2.33 GHz (4 MB L2, 1333 MHz FSB, 65 W) Xeon 5130, 2.00 GHz (4 MB L2, 1333 MHz FSB, 65 W) Xeon 5120, 1.86 GHz (4 MB L2, 1066 MHz FSB, 65 W) Xeon 5110, 1.60 GHz (4 MB L2, 1066 MHz FSB, 65 W) Xeon 5148LV, 2.33 GHz (4 MB L2, 1333 MHz FSB, 40 W) (low voltage edition) Clovertown 65 nm process technologyServer and Workstation CPU (SMP support for dual CPU system) Introduced December 13, 2006 Quad-core Intel VT-x , multiple OS supportEIST (Enhanced Intel SpeedStep Technology) in E5365, L5335 Execute Disable Bit TXT, enhanced security hardware extensions SSSE3 SIMD instructionsiAMT2 (Intel Active Management Technology), remotely manage computers VariantsXeon X5355, 2.66 GHz (2×4 MB L2, 1333 MHz FSB, 105 W) Xeon E5345, 2.33 GHz (2×4 MB L2, 1333 MHz FSB, 80 W) Xeon E5335, 2.00 GHz (2×4 MB L2, 1333 MHz FSB, 80 W) Xeon E5320, 1.86 GHz (2×4 MB L2, 1066 MHz FSB, 65 W) Xeon E5310, 1.60 GHz (2×4 MB L2, 1066 MHz FSB, 65 W) Xeon L5320, 1.86 GHz (2×4 MB L2, 1066 MHz FSB, 50 W) (low voltage edition) Conroe 65 nm process technologyDesktop CPU (SMP support restricted to 2 CPUs) Two cores on one die Introduced July 27, 2006 SSSE3 SIMD instructions291 million transistors 64 KB of L1 cache per core (32+32 KB 8-way) Intel VT-x , multiple OS supportTXT, enhanced security hardware extensions Execute Disable Bit EIST (Enhanced Intel SpeedStep Technology) iAMT2 (Intel Active Management Technology), remotely manage computers Intel Management Engine introducedLGA 775 VariantsCore 2 Duo E6850, 3.00 GHz (4 MB L2, 1333 MHz FSB) Core 2 Duo E6800, 2.93 GHz (4 MB L2, 1066 MHz FSB) Core 2 Duo E6750, 2.67 GHz (4 MB L2, 1333 MHz FSB, 65 W) Core 2 Duo E6700, 2.67 GHz (4 MB L2, 1066 MHz FSB) Core 2 Duo E6600, 2.40 GHz (4 MB L2, 1066 MHz FSB, 65 W) Core 2 Duo E6550, 2.33 GHz (4 MB L2, 1333 MHz FSB) Core 2 Duo E6420, 2.13 GHz (4 MB L2, 1066 MHz FSB) Core 2 Duo E6400, 2.13 GHz (2 MB L2, 1066 MHz FSB) Core 2 Duo E6320, 1.86 GHz (4 MB L2, 1066 MHz FSB) Family 6, Model 15, Stepping 6 Core 2 Duo E6300, 1.86 GHz (2 MB L2, 1066 MHz FSB) Conroe XE 65 nm process technologyDesktop Extreme Edition CPU (SMP support restricted to 2 CPUs) Introduced July 27, 2006 Same features as Conroe LGA 775 VariantsCore 2 Extreme X6800 – 2.93 GHz (4 MB L2, 1066 MHz FSB) Allendale 65 nm process technologyDesktop CPU (SMP support restricted to 2 CPUs) Two CPUs on one die Introduced January 21, 2007 SSSE3 SIMD instructions167 million transistors TXT, enhanced security hardware extensions Execute Disable Bit EIST (Enhanced Intel SpeedStep Technology) iAMT2 (Intel Active Management Technology), remotely manage computers LGA 775 VariantsCore 2 Duo E4700, 2.60 GHz (2 MB L2, 800 MHz FSB) Core 2 Duo E4600, 2.40 GHz (2 MB L2, 800 MHz FSB) Core 2 Duo E4500, 2.20 GHz (2 MB L2, 800 MHz FSB) Core 2 Duo E4400, 2.00 GHz (2 MB L2, 800 MHz FSB) Core 2 Duo E4300, 1.80 GHz (2 MB L2, 800 MHz FSB) Family 6, Model 15, Stepping 2 Merom 65 nm process technologyMobile CPU (SMP support restricted to 2 CPUs) Introduced July 27, 2006 Family 6, Model 15 Same features as Conroe Socket M / Socket P / 479-ball Micro-FCBGAVariantsCore 2 Extreme X7900 2.80 GHz (4 MB L2, 800 MHz FSB) Core 2 Extreme X7800 2.60 GHz (4 MB L2, 800 MHz FSB) Core 2 Duo T7800, 2.60 GHz (4 MB L2, 800 MHz FSB) (Santa Rosa platform ) Core 2 Duo T7700, 2.40 GHz (4 MB L2, 800 MHz FSB) Core 2 Duo T7600, 2.33 GHz (4 MB L2, 667 MHz FSB) Core 2 Duo T7500, 2.20 GHz (4 MB L2, 800 MHz FSB) Core 2 Duo T7400, 2.16 GHz (4 MB L2, 667 MHz FSB) Core 2 Duo T7300, 2.00 GHz (4 MB L2, 800 MHz FSB) Core 2 Duo T7250, 2.00 GHz (2 MB L2, 800 MHz FSB) Core 2 Duo T7200, 2.00 GHz (4 MB L2, 667 MHz FSB) Core 2 Duo T7100, 1.80 GHz (2 MB L2, 800 MHz FSB) Core 2 Duo T5600, 1.83 GHz (2 MB L2, 667 MHz FSB) Family 6, Model 15, Stepping 6 Core 2 Duo T5550, 1.83 GHz (2 MB L2, 667 MHz FSB, no VT) Core 2 Duo T5500, 1.66 GHz (2 MB L2, 667 MHz FSB, no VT) Core 2 Duo T5470, 1.60 GHz (2 MB L2, 800 MHz FSB, no VT) Family 6, Model 15, Stepping 13 Core 2 Duo T5450, 1.66 GHz (2 MB L2, 667 MHz FSB, no VT) Core 2 Duo T5300, 1.73 GHz (2 MB L2, 533 MHz FSB, no VT) Core 2 Duo T5270, 1.40 GHz (2 MB L2, 800 MHz FSB, no VT) Core 2 Duo T5250, 1.50 GHz (2 MB L2, 667 MHz FSB, no VT) Core 2 Duo T5200, 1.60 GHz (2 MB L2, 533 MHz FSB, no VT) Core 2 Duo L7700, 1.80 GHz (4 MB L2, 800 MHz FSB) (low voltage) Family 6, Model 15, Stepping 11 Core 2 Duo L7500, 1.60 GHz (4 MB L2, 800 MHz FSB) (low voltage) Core 2 Duo L7400, 1.50 GHz (4 MB L2, 667 MHz FSB) (low voltage) Core 2 Duo L7300, 1.40 GHz (4 MB L2, 800 MHz FSB) (low voltage) Core 2 Duo L7200, 1.33 GHz (4 MB L2, 667 MHz FSB) (low voltage) Core 2 Duo U7700, 1.33 GHz (2 MB L2, 533 MHz FSB) (ultra low voltage) Core 2 Duo U7600, 1.20 GHz (2 MB L2, 533 MHz FSB) (ultra low voltage) Core 2 Duo U7500, 1.06 GHz (2 MB L2, 533 MHz FSB) (ultra low voltage) Core 2 Duo U7100, 1.20 GHz (4 MB L2, 800 MHz FSB) (ultra low voltage) Family 6, Model 15, Stepping 11 Core 2 Solo U2100, 1.06 GHz (1 MB L2, 533 MHz FSB) (ultra low voltage) Core 2 Solo U2200, 1.20 GHz (1 MB L2, 533 MHz FSB) (ultra low voltage) Kentsfield 65 nm process technologyTwo dual-core CPU dies in one package Desktop CPU quad-core (SMP support restricted to 4 CPUs) Introduced December 13, 2006 Same features as Conroe but with 4 CPU cores 586 million transistors LGA 775 Family 6, Model 15, Stepping 11 VariantsCore 2 Extreme QX6850, 3 GHz (2×4 MB L2 cache, 1333 MHz FSB) Core 2 Extreme QX6800, 2.93 GHz (2×4 MB L2 cache, 1066 MHz FSB) (April 9, 2007) Core 2 Extreme QX6700, 2.66 GHz (2×4 MB L2 cache, 1066 MHz FSB) (November 14, 2006) Core 2 Quad Q6700, 2.66 GHz (2×4 MB L2 cache, 1066 MHz FSB) (July 22, 2007) Core 2 Quad Q6600, 2.40 GHz (2×4 MB L2 cache, 1066 MHz FSB) (January 7, 2007) Wolfdale 45 nm process technologyDie shrink of Conroe Same features as Conroe with the addition of:50% more cache, 6 MB as opposed to 4 MB Intel Trusted Execution Technology SSE4 SIMD instructions 410 million transistors VariantsCore 2 Duo E8600, 3.33 GHz (6 MB L2, 1333 MHz FSB) Core 2 Duo E8500, 3.16 GHz (6 MB L2, 1333 MHz FSB) Core 2 Duo E8435, 3.07 GHz (6 MB L2, 1066 MHz FSB) Core 2 Duo E8400, 3.00 GHz (6 MB L2, 1333 MHz FSB) Core 2 Duo E8335, 2.93 GHz (6 MB L2, 1066 MHz FSB) Core 2 Duo E8300, 2.83 GHz (6 MB L2, 1333 MHz FSB) Core 2 Duo E8235, 2.80 GHz (6 MB L2, 1066 MHz FSB) Core 2 Duo E8200, 2.66 GHz (6 MB L2, 1333 MHz FSB) Core 2 Duo E8135, 2.66 GHz (6 MB L2, 1066 MHz FSB) Core 2 Duo E8190, 2.66 GHz (6 MB L2, 1333 MHz FSB, no TXT, no VT) Wolfdale-3M 45 nm process technologyIntel Trusted Execution Technology VariantsCore 2 Duo E7600, 3.06 GHz (3 MB L2, 1066 MHz FSB) Core 2 Duo E7500, 2.93 GHz (3 MB L2, 1066 MHz FSB) Core 2 Duo E7400, 2.80 GHz (3 MB L2, 1066 MHz FSB) Core 2 Duo E7300, 2.66 GHz (3 MB L2, 1066 MHz FSB) Core 2 Duo E7200, 2.53 GHz (3 MB L2, 1066 MHz FSB) Yorkfield 45 nm process technologyQuad-core CPU Die shrink of Kentsfield Contains 2× Wolfdale dual-core dies in one package Same features as Wolfdale 820 million transistors VariantsCore 2 Extreme QX9770, 3.20 GHz (2×6 MB L2, 1600 MHz FSB) Core 2 Extreme QX9650, 3.00 GHz (2×6 MB L2, 1333 MHz FSB) Core 2 Quad Q9705, 3.16 GHz (2×3 MB L2, 1333 MHz FSB) Core 2 Quad Q9700, 3.16 GHz (2×3 MB L2, 1333 MHz FSB) Core 2 Quad Q9650, 3 GHz (2×6 MB L2, 1333 MHz FSB) Core 2 Quad Q9550, 2.83 GHz (2×6 MB L2, 1333 MHz FSB, 95 W TDP) Core 2 Quad Q9550s, 2.83 GHz (2×6 MB L2, 1333 MHz FSB, 65 W TDP) Core 2 Quad Q9450, 2.66 GHz (2×6 MB L2, 1333 MHz FSB, 95 W TDP) Core 2 Quad Q9505, 2.83 GHz (2×3 MB L2, 1333 MHz FSB, 95 W TDP) Core 2 Quad Q9505s, 2.83 GHz (2×3 MB L2, 1333 MHz FSB, 65 W TDP) Core 2 Quad Q9500, 2.83 GHz (2×3 MB L2, 1333 MHz FSB, 95 W TDP, no TXT) Core 2 Quad Q9400, 2.66 GHz (2×3 MB L2, 1333 MHz FSB, 95 W TDP) Core 2 Quad Q9400s, 2.66 GHz (2×3 MB L2, 1333 MHz FSB, 65 W TDP) Core 2 Quad Q9300, 2.50 GHz (2×3 MB L2, 1333 MHz FSB, 95 W TDP) Core 2 Quad Q8400, 2.66 GHz (2×2 MB L2, 1333 MHz FSB, 95 W TDP) Core 2 Quad Q8400s, 2.66 GHz (2×2 MB L2, 1333 MHz FSB, 65 W TDP) Core 2 Quad Q8300, 2.50 GHz (2×2 MB L2, 1333 MHz FSB, 95 W TDP) Core 2 Quad Q8300s, 2.50 GHz (2×2 MB L2, 1333 MHz FSB, 65 W TDP) Core 2 Quad Q8200, 2.33 GHz (2×2 MB L2, 1333 MHz FSB, 95 W TDP) Core 2 Quad Q8200s, 2.33 GHz (2×2 MB L2, 1333 MHz FSB, 65 W TDP) Core 2 Quad Q7600, 2.70 GHz (2×1 MB L2, 800 MHz FSB, no SSE4) (no Q7600 listed here) Intel Core2 Quad Mobile processor family – 45 nm process technologyQuad-core CPU VariantsCore 2 Quad Q9100, 2.26 GHz (2×6 MB L2, 1066 MHz FSB, 45 W TDP) Core 2 Quad Q9000, 2.00 GHz (2×3 MB L2, 1066 MHz FSB, 45 W TDP) Allendale 65 nm process technologyDesktop CPU (SMP support restricted to 2 CPUs) Two cores on one die Introduced January 21, 2007 SSSE3 SIMD instructions167 million transistors TXT, enhanced security hardware extensions Execute Disable Bit EIST (Enhanced Intel SpeedStep Technology) VariantsIntel Pentium E2220, 2.40 GHz (1 MB L2, 800 MHz FSB) Intel Pentium E2200, 2.20 GHz (1 MB L2, 800 MHz FSB) Intel Pentium E2180, 2.00 GHz (1 MB L2, 800 MHz FSB) Intel Pentium E2160, 1.80 GHz (1 MB L2, 800 MHz FSB) Intel Pentium E2140, 1.60 GHz (1 MB L2, 800 MHz FSB) Wolfdale-3M 45 nm process technologyIntel Pentium E6800, 3.33 GHz (2 MB L2,1066 MHz FSB) Intel Pentium E6700, 3.20 GHz (2 MB L2,1066 MHz FSB) Intel Pentium E6600, 3.06 GHz (2 MB L2,1066 MHz FSB) Intel Pentium E6500, 2.93 GHz (2 MB L2,1066 MHz FSB) Intel Pentium E6300, 2.80 GHz (2 MB L2,1066 MHz FSB) Intel Pentium E5800, 3.20 GHz (2 MB L2, 800 MHz FSB) Intel Pentium E5700, 3.00 GHz (2 MB L2, 800 MHz FSB) Intel Pentium E5500, 2.80 GHz (2 MB L2, 800 MHz FSB) Intel Pentium E5400, 2.70 GHz (2 MB L2, 800 MHz FSB) Intel Pentium E5300, 2.60 GHz (2 MB L2, 800 MHz FSB) Intel Pentium E5200, 2.50 GHz (2 MB L2, 800 MHz FSB) Intel Pentium E2210, 2.20 GHz (1 MB L2, 800 MHz FSB) Celeron (64-bit Core microarchitecture)Allendale 65 nm process technologyVariantsIntel Celeron E1600, 2.40 GHz (512 KB L2, 800 MHz FSB) Intel Celeron E1500, 2.20 GHz (512 KB L2, 800 MHz FSB) Intel Celeron E1400, 2.00 GHz (512 KB L2, 800 MHz FSB) Intel Celeron E1200, 1.60 GHz (512 KB L2, 800 MHz FSB) Wolfdale-3M 45 nm process technologyVariantsIntel Celeron E3500, 2.70 GHz (1 MB L2, 800 MHz FSB) Intel Celeron E3400, 2.60 GHz (1 MB L2, 800 MHz FSB) Intel Celeron E3300, 2.50 GHz (1 MB L2, 800 MHz FSB) Intel Celeron E3200, 2.40 GHz (1 MB L2, 800 MHz FSB) Conroe-L 65 nm process technologyVariantsIntel Celeron 450, 2.20 GHz (512 KB L2, 800 MHz FSB) Intel Celeron 440, 2.00 GHz (512 KB L2, 800 MHz FSB) Intel Celeron 430, 1.80 GHz (512 KB L2, 800 MHz FSB) Intel Celeron 420, 1.60 GHz (512 KB L2, 800 MHz FSB) Intel Celeron 220, 1.20 GHz (512 KB L2, 533 MHz FSB) Conroe-CL 65 nm process technologyLGA 771 package VariantsIntel Celeron 445, 1.87 GHz (512 KB L2, 1066 MHz FSB) Merom-L 65 nm process technology64 KB L1 cache 1 MB L2 cache (integrated) SSE3 SIMD instructions, 533 MHz/667 MHz front-side bus, execute-disable bit, 64-bit No SpeedStep technology, is not part of the 'Centrino ' package Variants520, 1.60 GHz 530, 1.73 GHz 540, 1.86 GHz 550, 2.00 GHz 560, 2.13 GHz 570, 2.26 GHz 667 MHz FSB575, 2.00 GHz 585, 2.16 GHz

64-bit processors: Intel 64 – Nehalem microarchitecture Clarkdale 32 nm process technology (manufacturing 7 Jan 2010)2 physical cores/2 threads 32+32 KB L1 cache 256 KB L2 cache 3 MB L3 cache Introduced January 2010 Socket 1156 LGA 2-channel DDR3 Integrated HD GPU VariantsG6950, 2.8 GHz (no Hyper-Threading )[15] G6960, 2.933 GHz (no Hyper-Threading) Clarkdale 32 nm process technology2 physical cores/4 threads 32+32 KB L1 cache 256 KB L2 cache 4 MB L3 cache Introduced on January 7, 2010 Socket 1156 LGA 2-channel DDR3 Integrated HD GPU Variants530, 2.93 GHz Hyper-Threading 540, 3.06 GHz Hyper-Threading 550, 3.2 GHz Hyper-Threading 560, 3.33 GHz Hyper-Threading Lynnfield 45 nm process technology4 physical cores/4 threads 32+32 KB L1 cache 256 KB L2 cache 8 MB L3 cache Introduced September 8, 2009 Family 6 Model E (Ext. Model 1E) Socket 1156 LGA2-channel DDR3 Variants750S, 2.40 GHz/3.20 GHz Turbo Boost 750, 2.66 GHz/3.20 GHz Turbo Boost 760, 2.80 GHz/3.33 GHz Turbo Boost Clarkdale 32 nm process technology2 physical cores/4 threads 32+32 KB L1 cache 256 KB L2 cache 4 MB L3 cache Introduced January, 2010 Socket 1156 LGA2-channel DDR3 Integrated HD GPU AES Support Variants650/655K, 3.2 GHz Hyper-Threading Turbo Boost 660/661, 3.33 GHz Hyper-Threading Turbo Boost 670, 3.46 GHz Hyper-Threading Turbo Boost 680, 3.60 GHz Hyper-Threading Turbo Boost Bloomfield 45 nm process technology4 physical cores/8 threads 256 KB L2 cache 8 MB L3 cache Front-side bus replaced with QuickPath up to 6.4 GT/sHyper-Threading is again included. This had previously been removed at the introduction of Core line781 million transistors Intel Turbo Boost Technology TDP 130 W Introduced November 17, 2008 Socket 1366 LGA 3-channel DDR3 Variants975 (extreme edition), 3.33 GHz/3.60 GHz Turbo Boost 965 (extreme edition), 3.20 GHz/3.46 GHz Turbo Boost 960, 3.20 GHz/3.46 GHz Turbo Boost 950, 3.06 GHz/3.33 GHz Turbo Boost 940, 2.93 GHz/3.20 GHz Turbo Boost 930, 2.80 GHz/3.06 GHz Turbo Boost 920, 2.66 GHz/2.93 GHz Turbo Boost Lynnfield 45 nm process technology4 physical cores/8 threads 32+32 KB L1 cache 256 KB L2 cache 8 MB L3 cache No QuickPath , instead compatible with slower DMI interface Hyper-Threading is includedIntroduced September 8, 2009 Socket 1156 LGA 2-channel DDR3 Variants880, 3.06 GHz/3.73 GHz Turbo Boost (TDP 95 W) 870/875K, 2.93 GHz/3.60 GHz Turbo Boost (TDP 95 W) 870S, 2.67 GHz/3.60 GHz Turbo Boost (TDP 82 W) 860, 2.80 GHz/3.46 GHz Turbo Boost (TDP 95 W) 860S, 2.53 GHz/3.46 GHz Turbo Boost (TDP 82 W) Westmere

Gulftown 32 nm process technology6 physical cores 256 KB L2 cache 12 MB L3 cache Front-side bus replaced with QuickPath up to 6.4 GT/sHyper-Threading is includedIntel Turbo Boost Technology Socket 1366 LGATDP 130 W Introduced 16 March 2010 Variants990X Extreme Edition, 3.46 GHz/3.73 GHz Turbo Boost 980X Extreme Edition, 3.33 GHz/3.60 GHz Turbo Boost 970, 3.20 GHz/3.46 GHz Turbo Boost Clarksfield – Intel Core i7 Mobile processor family – 45 nm process technology4 physical cores Hyper-Threading is includedIntel Turbo Boost Technology Variants940XM Extreme Edition, 2.13 GHz/3.33 GHz Turbo Boost (8 MB L3, TDP 55 W) 920XM Extreme Edition, 2.00 GHz/3.20 GHz Turbo Boost (8 MB L3, TDP 55 W) 840QM, 1.86 GHz/3.20 GHz Turbo Boost (8 MB L3, TDP 45 W) 820QM, 1.73 GHz/3.06 GHz Turbo Boost (8 MB L3, TDP 45 W) 740QM, 1.73 GHz/2.93 GHz Turbo Boost (6 MB L3, TDP 45 W) 720QM, 1.60 GHz/2.80 GHz Turbo Boost (6 MB L3, TDP 45 W)

Gainestown 45 nm process technologySame processor dies as Bloomfield 256 KB L2 cache 8 MB L3 cache, 4 MB may be disabled QuickPath up to 6.4 GT/sHyper-Threading is included in some models781 million transistors Introduced March 29, 2009 VariantsW5590, X5570, X5560, X5550, E5540, E5530, L5530, E5520, L5520, L5518, 4 cores, 8 MB L3 cache, HT E5506, L5506, E5504, 4 cores, 4 MB L3 cache, no HT L5508, E5502, E5502, 2 cores, 4 MB L3 cache, no HT

64-bit processors: Intel 64 – Sandy Bridge / Ivy Bridge microarchitecture Celeron (Sandy Bridge/Ivy Bridge microarchitecture)Sandy Bridge 32 nm process technology2 physical cores/2 threads (500 series), 1 physical core/1 thread (model G440) or 1 physical core/2 threads (models G460 & G465) 2 MB L3 cache (500 series), 1 MB (model G440) or 1.5 MB (models G460 & G465) Introduced 3rd quarter, 2011 Socket 1155 LGA2-channel DDR3-1066 400 series has max TDP of 35 W 500-series variants ending in 'T' have a peak TDP of 35 W; others, 65 W Integrated GPUAll variants have peak GPU turbo frequencies of 1 GHz Variants in the 400 series have GPUs running at a base frequency of 650 MHz Variants in the 500 series ending in 'T' have GPUs running at a base frequency of 650 MHz; others at 850 MHz All variants have 6 GPU execution units VariantsG440, 1.6 GHz G460, 1.8 GHz G465, 1.9 GHz G470, 2.0 GHz G530T, 2.0 GHz G540T, 2.1 GHz G550T, 2.2 GHz G530, 2.4 GHz G540, 2.5 GHz G550, 2.6 GHz G555, 2.7 GHz Pentium (Sandy Bridge/Ivy Bridge microarchitecture)Sandy Bridge 32 nm process technology2 physical cores/2 threads 3 MB L3 cache 624 million transistors Introduced May, 2011 Socket 1155 LGA2-channel DDR3-1333 (800 series) or DDR3-1066 (600 series) Variants ending in 'T' have a peak TDP of 35 W, others 65 W Integrated GPU (HD 2000 )All variants have peak GPU turbo frequencies of 1.1 GHz Variants ending in 'T' have GPUs running at a base frequency of 650 MHz; others at 850 MHz All variants have 6 GPU execution units VariantsG620T, 2.2 GHz G630T, 2.3 GHz G640T, 2.4 GHz G645T, 2.5 GHz G860T, 2.6 GHz G620, 2.6 GHz G622, 2.6 GHz G630, 2.7 GHz G632, 2.7 GHz G640, 2.8 GHz G840, 2.8 GHz G645, 2.9 GHz G850, 2.9 GHz G860, 3.0 GHz G870, 3.1 GHz Ivy Bridge 22 nm tri-gate transistor process technology2 physical cores/2 threads 32+32 KB (per core) L1 cache 256 KB (per core) L2 cache 3 MB L3 cache Introduced September, 2012 Socket 1155 LGA2-channel DDR3-1333 for G2000 series 2-channel DDR3-1600 for G2100 series All variants have GPU base frequencies of 650 MHz and peak GPU turbo frequencies of 1.05 GHz Variants ending in 'T' have a peak TDP of 35 W; others, TDP of 55 W VariantsG2020T, 2.5 GHz G2030T, 2.6 GHz G2100T, 2.6 GHz G2120T, 2.7 GHz G2010, 2.8 GHz G2020, 2.9 GHz G2030, 3.0 GHz G2120, 3.1 GHz G2130, 3.2 GHz G2140, 3.3 GHz Sandy Bridge 32 nm process technology2 physical cores/4 threads 32+32 KB (per core) L1 cache 256 KB (per core) L2 cache 3 MB L3 cache 624 million transistors Introduced January, 2011 Socket 1155 LGA2-channel DDR3-1333 Variants ending in 'T' have a peak TDP of 35 W, others 65 W Integrated GPUAll variants have peak GPU turbo frequencies of 1.1 GHz Variants ending in 'T' have GPUs running at a base frequency of 650 MHz; others at 850 MHz Variants ending in '5' have Intel HD Graphics 3000 (12 execution units); others have Intel HD Graphics 2000 (6 execution units) Variantsi3-2100T, 2.5 GHz i3-2120T, 2.6 GHz i3-2100, 3.1 GHz i3-2102, 3.1 GHz i3-2105, 3.1 GHz i3-2120, 3.3 GHz i3-2125, 3.3 GHz i3-2130, 3.4 GHz Ivy Bridge 22 nm tri-gate transistor process technology2 physical cores/4 threads 32+32 KB (per core) L1 cache 256 KB (per core) L2 cache 3 MB L3 cache Introduced September, 2012 Socket 1155 LGA2-channel DDR3-1600 Variants ending in '5' have Intel HD Graphics 4000; others have Intel HD Graphics 2500 All variants have GPU base frequencies of 650 MHz and peak GPU turbo frequencies of 1.05 GHz TDP 55 W Variantsi3-3220T, 2.8 GHz i3-3240T, 2.9 GHz i3-3210, 3.2 GHz i3-3220, 3.3 GHz i3-3225, 3.3 GHz i3-3240, 3.4 GHz i3-3250, 3.5 GHz Sandy Bridge 32 nm process technology4 physical cores/4 threads (except for i5-2390T which has 2 physical cores/4 threads) 32+32 KB (per core) L1 cache 256 KB (per core) L2 cache 6 MB L3 cache (except for i5-2390T which has 3 MB) 995 million transistors Introduced January, 2011 Socket 1155 LGA2-channel DDR3-1333 Variants ending in 'S' have a peak TDP of 65 W; others, 95 W except where noted Variants ending in 'K' have unlocked multipliers; others cannot be overclocked Integrated GPUi5-2500T has a peak GPU turbo frequency of 1.25 GHz, others 1.1 GHz Variants ending in 'T' have GPUs running at a base frequency of 650 MHz; others at 850 MHz Variants ending in '5' or 'K' have Intel HD Graphics 3000 (12 execution units), except i5-2550K which has no GPU; others have Intel HD Graphics 2000 (6 execution units) Variants ending in 'P' and the i5-2550K have no GPU Variantsi5-2390T, 2.7 GHz/3.5 GHz Turbo Boost (35 W max. TDP) i5-2500T, 2.3 GHz/3.3 GHz Turbo Boost (45 W max. TDP) i5-2400S, 2.5 GHz/3.3 GHz Turbo Boost i5-2405S, 2.5 GHz/3.3 GHz Turbo Boost i5-2500S, 2.7 GHz/3.7 GHz Turbo Boost i5-2300, 2.8 GHz/3.1 GHz Turbo Boost i5-2310, 2.9 GHz/3.2 GHz Turbo Boost i5-2320, 3.0 GHz/3.3 GHz Turbo Boost i5-2380P, 3.1 GHz/3.4 GHz Turbo Boost i5-2400, 3.1 GHz/3.4 GHz Turbo Boost i5-2450P, 3.2 GHz/3.5 GHz Turbo Boost i5-2500, 3.3 GHz/3.7 GHz Turbo Boost i5-2500K, 3.3 GHz/3.7 GHz Turbo Boost i5-2550K, 3.4 GHz/3.8 GHz Turbo Boost Ivy Bridge 22 nm Tri-gate transistor process technology4 physical cores/4 threads (except for i5-3470T which has 2 physical cores/4 threads) 32+32 KB (per core) L1 cache 256 KB (per core) L2 cache 6 MB L3 cache (except for i5-3470T which has 3 MB) Introduced April, 2012 Socket 1155 LGA2-channel DDR3-1600 Variants ending in 'S' have a peak TDP of 65 W, Variants ending in 'T' have a peak TDP of 35 or 45 W (see variants); others, 77 W except where noted Variants ending in 'K' have unlocked multipliers; others cannot be overclocked Variants ending in 'P' have no integrated GPU; others have Intel HD Graphics 2500 or Intel HD Graphics 4000 (i5-3475S and i5-3570K only) Variantsi5-3470T, 2.9 GHz/3.6 GHz max Turbo Boost (35 W TDP) i5-3570T, 2.3 GHz/3.3 GHz max Turbo Boost (45 W TDP) i5-3330S, 2.7 GHz/3.2 GHz max Turbo Boost i5-3450S, 2.8 GHz/3.5 GHz max Turbo Boost i5-3470S, 2.9 GHz/3.6 GHz max Turbo Boost i5-3475S, 2.9 GHz/3.6 GHz max Turbo Boost i5-3550S, 3.0 GHz/3.7 GHz max Turbo Boost i5-3570S, 3.1 GHz/3.8 GHz max Turbo Boost i5-3330, 3.0 GHz/3.2 GHz max Turbo Boost i5-3350P, 3.1 GHz/3.3 GHz max Turbo Boost (69 W TDP) i5-3450, 3.1 GHz/3.5 GHz max Turbo Boost i5-3470, 3.2 GHz/3.6 GHz max Turbo Boost i5-3550, 3.3 GHz/3.7 GHz max Turbo Boost i5-3570, 3.4 GHz/3.8 GHz max Turbo Boost i5-3570K, 3.4 GHz/3.8 GHz max Turbo Boost Sandy Bridge 32 nm process technology4 physical cores/8 threads 32+32 KB (per core) L1 cache 256 KB (per core) L2 cache 8 MB L3 cache 995 million transistors Introduced January, 2011 Socket 1155 LGA2-channel DDR3-1333 Variants ending in 'S' have a peak TDP of 65 W, others – 95 W Variants ending in 'K' have unlocked multipliers; others cannot be overclocked Integrated GPUAll variants have base GPU frequencies of 850 MHz and peak GPU turbo frequencies of 1.35 GHz Variants ending in 'K' have Intel HD Graphics 3000 (12 execution units); others have Intel HD Graphics 2000 (6 execution units) Variantsi7-2600S, 2.8 GHz/3.8 GHz Turbo Boost i7-2600, 3.4 GHz/3.8 GHz Turbo Boost i7-2600K, 3.4 GHz/3.8 GHz Turbo Boost i7-2700K, 3.5 GHz/3.9 GHz Turbo Boost Sandy Bridge-E 32 nm process technologyUp to 6 physical cores/12 threads depending on model number 32+32 KB (per core) L1 cache 256 KB (per core) L2 cache Up to 20 MB L3 cache depending on model number 2.27 billion transistors Introduced November, 2011 Socket 2011 LGA4-channel DDR3-1600 All variants have a peak TDP of 130 W No integrated GPU Variants (all marketed under "Intel Core X-series processors")[16] i7-3820, 3.6 GHz/3.8 GHz Turbo Boost, 4 cores, 10 MB L3 cache i7-3930K, 3.2 GHz/3.8 GHz Turbo Boost, 6 cores, 12 MB L3 cache i7-3960X, 3.3 GHz/3.9 GHz Turbo Boost, 6 cores, 15 MB L3 cache i7-3970X, 3.5 GHz/4.0 GHz Turbo Boost, 6 cores, 15 MB L3 cache Ivy Bridge 22 nm Tri-gate transistor process technology4 physical cores/8 threads 32+32 KB (per core) L1 cache 256 KB (per core) L2 cache 8 MB L3 cache Introduced April, 2012 Socket 1155 LGA2-channel DDR3-1600 Variants ending in 'S' have a peak TDP of 65 W, variants ending in 'T' have a peak TDP of 45 W, others – 77 W Variants ending in 'K' have unlocked multipliers; others cannot be overclocked Integrated GPU Intel HD Graphics 4000 Variantsi7-3770T – 2.5 GHz/3.7 GHz Turbo Boost i7-3770S – 3.1 GHz/3.9 GHz Turbo Boost i7-3770 – 3.4 GHz/3.9 GHz Turbo Boost i7-3770K – 3.5 GHz/3.9 GHz Turbo Boost

64-bit processors: Intel 64 – Haswell microarchitecture Haswell

64-bit processors: Intel 64 – Broadwell microarchitecture Broadwell Broadwell 4 physical cores/4 threads 4 MB L3 cache Introduced Q2'15 Socket 1150 LGA2-channel DDR3L-1333/1600 Integrated GPU Variantsi5-5575R – 2.80 GHz/3.30 GHz Turbo Boost i5-5675C – 3.10 GHz/3.60 GHz Turbo Boost i5-5675R – 3.10 GHz/3.60 GHz Turbo Boost Core i7 (5th generation, Including Core-X Series)Broadwell 4 physical cores/8 threads 6 MB L3 cache Introduced Q2'15 Socket 1150 LGA2-channel DDR3L-1333/1600 Integrated GPU Variantsi7-5775C – 3.30 GHz/3.70 GHz Turbo Boost i7-5775R – 3.30 GHz/3.80 GHz Turbo Boost Broadwell-E 6–10 physical cores/12–20 threads 15–25 MB L3 cache Introduced Q2'16 Socket 2011-v3 LGA4-channel DDR4-2133/2400 No Integrated GPU Variants (all marketed under "Intel Core X-series processors")[16] i7-6800K – 3.40 GHz/3.60 GHz Turbo Boost/3.80 GHz Turbo Boost Max Technology 3.0 Frequency 15 MB L3 cache i7-6850K – 3.60 GHz/3.80 GHz Turbo Boost/4.00 GHz Turbo Boost Max Technology 3.0 Frequency 15 MB L3 cache i7-6900K – 3.20 GHz/3.70 GHz Turbo Boost/4.00 GHz Turbo Boost Max Technology 3.0 Frequency 20 MB L3 cache i7-6950X – 3.00 GHz/3.50 GHz Turbo Boost/4.00 GHz Turbo Boost Max Technology 3.0 Frequency 25 MB L3 cache

Other Broadwell CPUs Not listed (yet) are several Broadwell-based CPU models:[17]

Server and workstation CPUssingle-CPU: Pentium D15nn, Xeon D-15nn, Xeon E3-12nn v4, Xeon E5-16nn v4 dual-CPU: Xeon E5-26nn v4 quad-CPU: Xeon E5-46nn v4, Xeon E7-48nn v4 octo-CPU: Xeon E7-88nn v4 Embedded CPUsCore i7-57nnEQ, Core i7-58nnEQ Mobile CPUsCeleron 32nnU, Celeron 37nnU Pentium 38nnU Core M-5Ynn Core i3-50nnU Core i5-5nnnU Core i7-55nnU, Core i7-56nnU, Core i7-57nnHQ, Core i7-59nnHQ Note: this list does not say that all processors that match these patterns are Broadwell-based or fit into this scheme. The model numbers may have suffixes that are not shown here.

64-bit processors: Intel 64 – Skylake microarchitecture Skylake 14 nm process technology2 physical cores/4 threads 3–4 MB L3 cache Introduced Q3'15 Socket 1151 LGA2-channel DDR3L-1333/1600, DDR4-1866/2133 Integrated GPU Intel HD Graphics 530 (only i3-6098P have HD Graphics 510) Variantsi3-6098P – 3.60 GHz i3-6100T – 3.20 GHz i3-6100 – 3.70 GHz i3-6300T – 3.30 GHz i3-6300 – 3.80 GHz i3-6320 – 3.90 GHz Skylake 4 physical cores/4 threads 6 MB L3 cache Introduced Q3'15 Socket 1151 LGA2-channel DDR3L-1333/1600, DDR4-1866/2133 Integrated GPU Intel HD Graphics 530 Variantsi5-6300HQ – 2.30/3.20 GHz Turbo Boost i5-6400T – 2.20 GHz/2.80 GHz Turbo Boost i5-6400 – 2.70 GHz/3.30 GHz Turbo Boost i5-6440hq i5-6500T – 2.50 GHz/3.10 GHz Turbo Boost i5-6500 – 3.20 GHz/3.60 GHz Turbo Boost i5-6600T – 2.70 GHz/3.50 GHz Turbo Boost i5-6600 – 3.30 GHz/3.90 GHz Turbo Boost i5-6600K – 3.50 GHz/3.90 GHz Turbo Boost Skylake 4 physical cores/8 threads 8 MB L3 cache Introduced Q3'15 Socket 1151 LGA2-channel DDR3L-1333/1600, DDR4-1866/2133 Integrated GPU Intel HD Graphics 530 Variantsi7-6700T – 2.80 GHz/3.60 GHz Turbo Boost i7-6700 – 3.40 GHz/4.00 GHz Turbo Boost i7-6700K – 4.00 GHz/4.20 GHz Turbo Boost

Other Skylake processors Many Skylake-based processors are not yet listed in this section: mobile i3/i5/i7 processors (U, H, and M suffixes), embedded i3/i5/i7 processors (E suffix), certain i7-67nn/i7-68nn/i7-69nn.[18] Skylake-based "Core X-series" processors (certain i7-78nn and i9-79nn models) can be found under current models.

64-bit processors: Intel 64 (7th generation) – Kaby Lake microarchitecture

64-bit processors: Intel 64 (8th and 9th generation) – Coffee Lake microarchitecture

64-bit processors: Intel 64 – Cannon Lake microarchitecture

64-bit processors: Intel 64 (10th generation) – Ice Lake microarchitecture

64-bit processors: Intel 64 (10th generation) – Comet Lake microarchitecture

64-bit processors: Intel 64 (11th generation) – Tiger Lake microarchitecture

64-bit processors: Intel 64 (12th generation) – Alder Lake microarchitecture

64-bit processors: Intel 64 (13th generation) – Raptor Lake microarchitecture

Intel Tera-Scale

Intel 805xx product codes Intel discontinued the use of part numbers such as 80486 in the marketing of mainstream x86-architecture processors with the introduction of the Pentium brand in 1993. However, numerical codes, in the 805xx range, continued to be assigned to these processors for internal and part numbering uses. The following is a list of such product codes in numerical order:

Intel 806xx product codes

Intel 807xx product codes

See also

Notes ^ a b Price is Recommended Customer Price (RCP) at launch. RCP is the trade price that processors are sold by Intel to retailers and OEMs. Actual MSRP for consumers is higher. ^ The 4004's original goal was to equal the clock rate of the IBM 1620 Model I (1 MHz); this was not quite met.

References ^ Bonshor, Gavin. "Intel Announces 14th Gen Core Series For Desktop: Core i9-14900K, Core i7-14700K and Core i5-14600K". www.anandtech.com . Archived from the original on October 17, 2023. Retrieved 2023-10-17 . ^ "Intel Launches Intel Core 14th Gen Desktop Processors for Enthusiasts". Intel . Archived from the original on October 17, 2023. Retrieved 2023-10-17 . ^ "Intel Releases 14th Gen Core HX "Raptor Lake Refresh" Mobile Processors". TechPowerUP. 8 January 2024. ^ a b c "Intel Unveils Full Intel Core X-series Processor Family Specs". Intel Newsroom . Archived from the original on 2017-08-07. Retrieved 2017-08-07 . ^ "Intel Processors". Archived from the original on 2012-04-24. Retrieved 2013-01-28 . ^ a b c "Intel Microprocessor Quick Reference Guide – Product Family". Archived from the original on 2010-03-04. Retrieved 2010-01-08 . ^ Ashborn, Jim; "Advanced Packaging: A Little Goes A Long Way", Intel Corporation, Solutions, January/February 1986, Page 2 ^ "Product: 8245" (PDF) . console5.com . Archived (PDF) from the original on Jul 9, 2021. Retrieved 22 December 2021 . ^ HAYES, JOHN.P (1978). Computer Architecture and Organization . McGraw-Hill International Book Company. p. 201. ISBN 0-07-027363-4 ^ a b c Intel IAPX 86,88 User's Manual, August 1981, Intel order number 210201-001 ^ a b c d e Badri Ram (1 September 2001). Adv Microprocessors Interfacing. Tata McGraw-Hill Education. pp. 208–. ISBN 978-0-07-043448-6 ^ Rant, Jon; "Extending the Legacy of Leadership: The 80386 Arrives", Intel Corporation, Special 32-Bit Issue Solutions, November/December 1985, page 2 ^ Intel Processor Spec Finder for Celeron M Archived November 3, 2009, at the Wayback Machine ^ Not listed as an official model by Intel but used by Apple in their Intel-based Mac Mini , released March 2006 Archived March 20, 2009, at the Wayback Machine ^ "Intel Pentium Processor G6950 (3M Cache, 2.80 GHz) with SPEC Code(s) SLBMS". Ark.intel.com. 2010-07-13. Archived from the original on 2011-03-09. Retrieved 2010-07-29 . ^ a b "Intel Core X-series Processors in Intel's database on ark.intel.com". Archived from the original on 2017-12-08. Retrieved 2018-03-31 . ^ "Broadwell CPUs on ark.intel.com". Archived from the original on 2018-03-31. Retrieved 2018-03-31 . ^ "ark: Skylake". Archived from the original on 2018-03-31. Retrieved 2018-03-31 .

External links Intel Museum: History of the Microprocessor Intel Processors information