La memoria flash es un medio de almacenamiento de memoria de computadora electrónico no volátil que se puede borrar y reprogramar eléctricamente. Los dos tipos principales de memoria flash, flash NOR y flash NAND , se denominan así por las puertas lógicas NOR y NAND . Ambos utilizan el mismo diseño de celda, que consiste en MOSFET de puerta flotante . Se diferencian a nivel de circuito dependiendo de si el estado de la línea de bits o las líneas de palabras se eleva o se reduce: en flash NAND, la relación entre la línea de bits y las líneas de palabras se asemeja a una puerta NAND; en flash NOR, se asemeja a una puerta NOR.

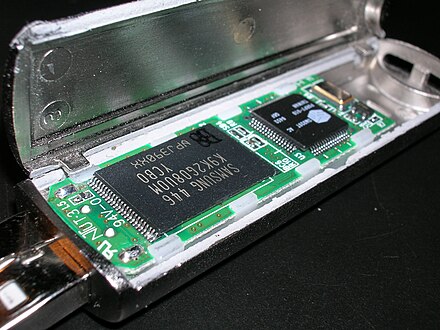

La memoria flash, un tipo de memoria de compuerta flotante , fue inventada por Fujio Masuoka en Toshiba en 1980 y se basa en la tecnología EEPROM . Toshiba comenzó a comercializar memoria flash en 1987. [1] Las EPROM debían borrarse por completo antes de poder reescribirse. Sin embargo, la memoria flash NAND se puede borrar, escribir y leer en bloques (o páginas), que generalmente son mucho más pequeños que el dispositivo completo. La memoria flash NOR permite escribir una sola palabra de máquina (en una ubicación borrada) o leerla de forma independiente. Un dispositivo de memoria flash generalmente consta de uno o más chips de memoria flash (cada uno de los cuales contiene muchas celdas de memoria flash), junto con un chip controlador de memoria flash independiente.

El tipo NAND se encuentra principalmente en tarjetas de memoria , unidades flash USB , unidades de estado sólido (las producidas desde 2009), teléfonos con funciones especiales , teléfonos inteligentes y productos similares, para el almacenamiento general y la transferencia de datos. La memoria flash NAND o NOR también se utiliza a menudo para almacenar datos de configuración en productos digitales, una tarea que antes era posible gracias a la EEPROM o la RAM estática alimentada por batería . Una desventaja clave de la memoria flash es que solo puede soportar una cantidad relativamente pequeña de ciclos de escritura en un bloque específico. [2]

La memoria flash NOR es conocida por sus capacidades de acceso aleatorio directo, lo que la hace apta para ejecutar código directamente. Su arquitectura permite el acceso a bytes individuales, lo que facilita velocidades de lectura más rápidas en comparación con la memoria flash NAND. La memoria flash NAND funciona con una arquitectura diferente, que se basa en un enfoque de acceso en serie. Esto hace que NAND sea adecuada para el almacenamiento de datos de alta densidad, pero menos eficiente para tareas de acceso aleatorio. La memoria flash NAND se utiliza a menudo en escenarios en los que es crucial contar con un almacenamiento rentable y de alta capacidad, como en unidades USB, tarjetas de memoria y unidades de estado sólido ( SSD ).

El principal factor diferenciador radica en sus casos de uso y estructuras internas. La memoria flash NOR es óptima para aplicaciones que requieren un acceso rápido a bytes individuales, como en sistemas integrados para la ejecución de programas. La memoria flash NAND, por otro lado, destaca en escenarios que exigen un almacenamiento rentable y de alta capacidad con acceso secuencial a los datos.

La memoria flash [3] se utiliza en ordenadores , PDA , reproductores de audio digitales , cámaras digitales , teléfonos móviles , sintetizadores , videojuegos , instrumentación científica , robótica industrial y electrónica médica . La memoria flash tiene un tiempo de acceso de lectura rápido , pero no es tan rápido como la RAM o ROM estática. En dispositivos portátiles, se prefiere utilizar memoria flash debido a su resistencia a los golpes mecánicos, ya que las unidades mecánicas son más propensas a sufrir daños mecánicos. [4]

Debido a que los ciclos de borrado son lentos, los grandes tamaños de bloque utilizados en el borrado de memoria flash le otorgan una ventaja de velocidad significativa sobre la EEPROM no flash al escribir grandes cantidades de datos. A partir de 2019, [update]la memoria flash cuesta mucho menos que la EEPROM programable por bytes y se había convertido en el tipo de memoria dominante dondequiera que un sistema requiriera una cantidad significativa de almacenamiento de estado sólido no volátil . Sin embargo, las EEPROM todavía se utilizan en aplicaciones que requieren solo pequeñas cantidades de almacenamiento, por ejemplo, en implementaciones SPD en módulos de memoria de computadora. [5] [6]

Los paquetes de memoria flash pueden utilizar apilamiento de matrices con vías a través de silicio y varias docenas de capas de celdas NAND TLC 3D (por matriz) simultáneamente para lograr capacidades de hasta 1 tebibyte por paquete utilizando 16 matrices apiladas y un controlador flash integrado como una matriz separada dentro del paquete. [7] [8] [9] [10]

Los orígenes de la memoria flash se remontan al desarrollo del MOSFET de compuerta flotante (FGMOS) , también conocido como transistor de compuerta flotante. [11] [12] El MOSFET original se inventó en Bell Labs entre 1955 y 1960, después de que Frosch y Derick descubrieran la pasivación de la superficie y usaran su descubrimiento para crear los primeros transistores planares. [13] [14] [15] [16] [17] [18] Dawon Kahng desarrolló una variación, el MOSFET de compuerta flotante, con el ingeniero taiwanés-estadounidense Simon Min Sze en Bell Labs en 1967. [19] Propusieron que podría usarse como celdas de memoria de compuerta flotante para almacenar una forma de memoria de solo lectura programable ( PROM ) que es a la vez no volátil y reprogramable. [19]

Los primeros tipos de memoria de puerta flotante incluyeron EPROM (PROM borrable) y EEPROM (PROM borrable eléctricamente) en la década de 1970. [19] Sin embargo, las primeras memorias de puerta flotante requerían que los ingenieros construyeran una celda de memoria para cada bit de datos, lo que resultó ser engorroso, [20] lento, [21] y costoso, restringiendo la memoria de puerta flotante a aplicaciones de nicho en la década de 1970, como equipos militares y los primeros teléfonos móviles experimentales . [11]

La EEPROM moderna basada en el túnel de Fowler-Nordheim para borrar datos fue inventada por Bernward y patentada por Siemens en 1974. [22] Y desarrollada aún más entre 1976 y 1978 por Eliyahou Harari en Hughes Aircraft Company y George Perlegos y otros en Intel. [23] [24] Esto llevó a la invención de la memoria flash por parte de Masuoka en Toshiba en 1980. [20] [25] [26] La mejora entre EEPROM y flash es que flash se programa en bloques mientras que EEPROM se programa en bytes. Según Toshiba, el nombre "flash" fue sugerido por el colega de Masuoka, Shōji Ariizumi, porque el proceso de borrado de los contenidos de la memoria le recordaba al flash de una cámara . [27] Masuoka y sus colegas presentaron la invención de la memoria flash NOR en 1984, [28] [29] y luego la memoria flash NAND en la Reunión Internacional de Dispositivos Electrónicos (IEDM) del IEEE de 1987 celebrada en San Francisco. [30]

Toshiba lanzó comercialmente la memoria flash NAND en 1987. [1] [19] Intel Corporation introdujo el primer chip flash comercial de tipo NOR en 1988. [31] La memoria flash basada en NOR tiene tiempos de borrado y escritura largos, pero proporciona buses de datos y direcciones completos , lo que permite un acceso aleatorio a cualquier ubicación de memoria . Esto la convierte en un reemplazo adecuado para los chips de memoria de solo lectura (ROM) más antiguos, que se utilizan para almacenar código de programa que rara vez necesita actualizarse, como el BIOS de una computadora o el firmware de los decodificadores . Su resistencia puede ser desde tan solo 100 ciclos de borrado para una memoria flash en chip, [32] hasta los más típicos 10 000 o 100 000 ciclos de borrado, hasta 1 000 000 de ciclos de borrado. [33] La memoria flash basada en NOR fue la base de los primeros medios extraíbles basados en flash; CompactFlash se basó originalmente en ella, aunque las tarjetas posteriores se trasladaron a la memoria flash NAND menos costosa.

La memoria flash NAND tiene tiempos de borrado y escritura reducidos y requiere menos área de chip por celda, lo que permite una mayor densidad de almacenamiento y un menor costo por bit que la memoria flash NOR. Sin embargo, la interfaz de E/S de la memoria flash NAND no proporciona un bus de direcciones externo de acceso aleatorio. En cambio, los datos deben leerse en función de bloques, con tamaños de bloque típicos de cientos a miles de bits. Esto hace que la memoria flash NAND no sea adecuada como reemplazo directo de la ROM de programa, ya que la mayoría de los microprocesadores y microcontroladores requieren acceso aleatorio a nivel de bytes. En este sentido, la memoria flash NAND es similar a otros dispositivos de almacenamiento de datos secundarios , como discos duros y medios ópticos , y por lo tanto es muy adecuada para su uso en dispositivos de almacenamiento masivo, como tarjetas de memoria y unidades de estado sólido (SSD). Por ejemplo, las SSD almacenan datos utilizando múltiples chips de memoria flash NAND.

El primer formato de tarjeta de memoria extraíble basado en NAND fue SmartMedia , lanzado en 1995. Le siguieron muchos otros, entre ellos MultiMediaCard , Secure Digital , Memory Stick y xD-Picture Card .

Una nueva generación de formatos de tarjetas de memoria, entre los que se incluyen RS-MMC , miniSD y microSD , se caracterizan por tener factores de forma extremadamente pequeños. Por ejemplo, la tarjeta microSD tiene una superficie de poco más de 1,5 cm2 y un grosor de menos de 1 mm.

La memoria flash NAND ha alcanzado niveles significativos de densidad de memoria como resultado de varias tecnologías importantes que se comercializaron entre fines de la década de 2000 y principios de la década de 2010. [34]

La memoria flash NOR fue el tipo de memoria Flash más común vendido hasta 2005, cuando la memoria flash NAND superó a la memoria flash NOR en ventas. [35]

La tecnología de celdas multinivel (MLC) almacena más de un bit en cada celda de memoria . NEC demostró la tecnología de celdas multinivel (MLC) en 1998, con un chip de memoria flash de 80 Mb que almacenaba 2 bits por celda. [36] STMicroelectronics también demostró MLC en 2000, con un chip de memoria flash NOR de 64 MB . [37] En 2009, Toshiba y SanDisk introdujeron chips flash NAND con tecnología QLC que almacenaban 4 bits por celda y tenían una capacidad de 64 Gbit. [38] [39] Samsung Electronics introdujo la tecnología de celdas de triple nivel (TLC) que almacenaban 3 bits por celda, y comenzó a producir en masa chips NAND con tecnología TLC en 2010. [40]

La tecnología de flash de trampa de carga (CTF) reemplaza la compuerta flotante de polisilicio, que está intercalada entre un óxido de compuerta de bloqueo por encima y un óxido de tunelización por debajo, con una capa de nitruro de silicio eléctricamente aislante; la capa de nitruro de silicio atrapa electrones. En teoría, la CTF es menos propensa a la fuga de electrones, lo que proporciona una mejor retención de datos. [41] [42] [43] [44] [45] [46]

Debido a que el CTF reemplaza el polisilicio con un nitruro eléctricamente aislante, permite celdas más pequeñas y una mayor resistencia (menor degradación o desgaste). Sin embargo, los electrones pueden quedar atrapados y acumularse en el nitruro, lo que lleva a la degradación. La fuga se agrava a altas temperaturas ya que los electrones se excitan más con el aumento de las temperaturas. Sin embargo, la tecnología CTF todavía utiliza un óxido de túnel y una capa de bloqueo que son los puntos débiles de la tecnología, ya que aún pueden dañarse de las formas habituales (el óxido de túnel puede degradarse debido a campos eléctricos extremadamente altos y la capa de bloqueo debido a la inyección de agujero caliente en el ánodo (AHHI). [47] [48]

La degradación o el desgaste de los óxidos es la razón por la que la memoria flash tiene una resistencia limitada y la retención de datos disminuye (aumenta el potencial de pérdida de datos) a medida que aumenta la degradación, ya que los óxidos pierden sus características de aislamiento eléctrico a medida que se degradan. Los óxidos deben aislar contra los electrones para evitar que se filtren, lo que provocaría la pérdida de datos.

En 1991, investigadores de NEC, incluidos N. Kodama, K. Oyama e Hiroki Shirai, describieron un tipo de memoria flash con un método de trampa de carga. [49] En 1998, Boaz Eitan de Saifun Semiconductors (posteriormente adquirida por Spansion ) patentó una tecnología de memoria flash llamada NROM que aprovechó una capa de captura de carga para reemplazar la compuerta flotante convencional utilizada en los diseños de memoria flash convencionales. [50] En 2000, un equipo de investigación de Advanced Micro Devices (AMD) dirigido por Richard M. Fastow, el ingeniero egipcio Khaled Z. Ahmed y el ingeniero jordano Sameer Haddad (que más tarde se unió a Spansion) demostró un mecanismo de captura de carga para celdas de memoria flash NOR. [51] CTF fue comercializado posteriormente por AMD y Fujitsu en 2002. [52] La tecnología 3D V-NAND (NAND vertical) apila celdas de memoria flash NAND verticalmente dentro de un chip utilizando tecnología flash de trampa de carga 3D (CTP). La tecnología 3D V-NAND fue anunciada por primera vez por Toshiba en 2007, [53] y el primer dispositivo, con 24 capas, fue comercializado por primera vez por Samsung Electronics en 2013. [54] [55]

La tecnología de circuito integrado 3D (3D IC) apila chips de circuitos integrados (IC) verticalmente en un único paquete de chip IC 3D. [34] Toshiba introdujo la tecnología IC 3D en la memoria flash NAND en abril de 2007, cuando presentó un chip de memoria flash NAND integrado compatible con eMMC de 16 GB (número de producto THGAM0G7D8DBAI6, a menudo abreviado THGAM en los sitios web de los consumidores), que se fabricó con ocho chips flash NAND de 2 GB apilados. [56] En septiembre de 2007, Hynix Semiconductor (ahora SK Hynix ) introdujo la tecnología IC 3D de 24 capas, con un chip de memoria flash de 16 GB que se fabricó con 24 chips flash NAND apilados mediante un proceso de unión de obleas. [57] Toshiba también utilizó un IC 3D de ocho capas para su chip flash THGBM de 32 GB en 2008. [58] En 2010, Toshiba utilizó un IC 3D de 16 capas para su chip flash THGBM2 de 128 GB, que se fabricó con 16 chips apilados de 8 GB. [59] En la década de 2010, los IC 3D comenzaron a usarse comercialmente de forma generalizada para la memoria flash NAND en dispositivos móviles . [34]

En 2016, Micron e Intel introdujeron una tecnología conocida como CMOS Under the Array/CMOS Under Array (CUA), Core over Periphery (COP), Periphery Under Cell (PUA) o Xtacking, [60] en la que el circuito de control para la memoria flash se coloca debajo o encima de la matriz de celdas de memoria flash. Esto ha permitido un aumento en la cantidad de planos o secciones que tiene un chip de memoria flash, aumentando de 2 planos a 4, sin aumentar el área dedicada a los circuitos de control o periféricos. Esto aumenta la cantidad de operaciones de E/S por chip o matriz flash, pero también presenta desafíos al construir capacitores para bombas de carga utilizadas para escribir en la memoria flash. [61] [62] [63] Algunas matrices flash tienen hasta 6 planos. [64]

A partir de agosto de 2017, están disponibles tarjetas microSD con una capacidad de hasta 400 GB (400 mil millones de bytes). [65] [66] El mismo año, Samsung combinó el apilamiento de chips IC 3D con sus tecnologías 3D V-NAND y TLC para fabricar su chip de memoria flash KLUFG8R1EM de 512 GB con ocho chips V-NAND de 64 capas apilados. [8] En 2019, Samsung produjo un chip flash de 1024 GB , con ocho chips V-NAND de 96 capas apilados y con tecnología QLC. [67] [68]

La memoria flash almacena información en una matriz de celdas de memoria hechas de transistores de compuerta flotante . En los dispositivos de celda de un solo nivel (SLC), cada celda almacena solo un bit de información. Los dispositivos de celda de múltiples niveles (MLC), incluidos los dispositivos de celda de triple nivel (TLC), pueden almacenar más de un bit por celda.

La puerta flotante puede ser conductora (normalmente polisilicio en la mayoría de los tipos de memoria flash) o no conductora (como en la memoria flash SONOS ). [69]

En la memoria flash, cada celda de memoria se parece a un transistor de efecto de campo de metal-óxido-semiconductor (MOSFET) estándar, excepto que el transistor tiene dos compuertas en lugar de una. Las celdas pueden verse como un interruptor eléctrico en el que la corriente fluye entre dos terminales (fuente y drenaje) y está controlada por una compuerta flotante (FG) y una compuerta de control (CG). La CG es similar a la compuerta en otros transistores MOS, pero debajo de esta, está la FG aislada por completo por una capa de óxido. La FG se interpone entre la CG y el canal MOSFET. Debido a que la FG está aislada eléctricamente por su capa aislante, los electrones colocados sobre ella quedan atrapados. Cuando la FG se carga con electrones, esta carga apantalla el campo eléctrico de la CG, aumentando así el voltaje umbral (V T ) de la celda. Esto significa que el V T de la celda se puede cambiar entre el voltaje umbral de FG sin carga (V T1 ) y el voltaje umbral de FG con mayor carga (V T2 ) cambiando la carga de FG. Para leer un valor de la celda, se aplica un voltaje intermedio (V I ) entre V T1 y V T2 al CG. Si el canal conduce en V I , el FG debe estar descargado (si estuviera cargado, no habría conducción porque V I es menor que V T2 ). Si el canal no conduce en V I , indica que el FG está cargado. El valor binario de la celda se detecta determinando si hay corriente fluyendo a través del transistor cuando se afirma V I en el CG. En un dispositivo de celda de varios niveles, que almacena más de un bit por celda, se detecta la cantidad de flujo de corriente (en lugar de simplemente su presencia o ausencia), para determinar con mayor precisión el nivel de carga en el FG.

Los MOSFET de compuerta flotante se denominan así porque hay una capa de óxido de túnel eléctricamente aislante entre la compuerta flotante y el silicio, por lo que la compuerta "flota" sobre el silicio. El óxido mantiene los electrones confinados en la compuerta flotante. La degradación o el desgaste (y la resistencia limitada de la memoria Flash de compuerta flotante) se producen debido al campo eléctrico extremadamente alto (10 millones de voltios por centímetro) que experimenta el óxido. Esas densidades de voltaje tan altas pueden romper los enlaces atómicos con el tiempo en el óxido relativamente delgado, degradando gradualmente sus propiedades de aislamiento eléctrico y permitiendo que los electrones queden atrapados y pasen libremente (fugas) desde la compuerta flotante hacia el óxido, lo que aumenta la probabilidad de pérdida de datos, ya que los electrones (cuya cantidad se utiliza para representar diferentes niveles de carga, cada uno asignado a una combinación diferente de bits en la memoria Flash MLC) normalmente están en la compuerta flotante. Por eso la retención de datos disminuye y el riesgo de pérdida de datos aumenta con el aumento de la degradación. [70] [71] [45] [72] [73] El óxido de silicio en una celda se degrada con cada operación de borrado. La degradación aumenta la cantidad de carga negativa en la celda con el tiempo debido a los electrones atrapados en el óxido y anula parte del voltaje de la compuerta de control; esto con el tiempo también hace que el borrado de la celda sea más lento, por lo que para mantener el rendimiento y la confiabilidad del chip NAND, la celda debe retirarse del uso. La resistencia también disminuye con el número de bits en una celda. Con más bits en una celda, el número de estados posibles (cada uno representado por un nivel de voltaje diferente) en una celda aumenta y es más sensible a los voltajes utilizados para la programación. Los voltajes se pueden ajustar para compensar la degradación del óxido de silicio y, a medida que aumenta el número de bits, también aumenta el número de estados posibles y, por lo tanto, la celda es menos tolerante a los ajustes a los voltajes de programación, porque hay menos espacio entre los niveles de voltaje que definen cada estado en una celda. [74]

El proceso de mover electrones desde la compuerta de control hacia la compuerta flotante se denomina efecto túnel de Fowler-Nordheim y cambia fundamentalmente las características de la celda al aumentar el voltaje umbral del MOSFET. Esto, a su vez, cambia la corriente de drenaje-fuente que fluye a través del transistor para un voltaje de compuerta determinado, que finalmente se utiliza para codificar un valor binario. El efecto túnel de Fowler-Nordheim es reversible, por lo que se pueden agregar o quitar electrones de la compuerta flotante, procesos tradicionalmente conocidos como escritura y borrado. [75]

A pesar de la necesidad de voltajes de programación y borrado relativamente altos, prácticamente todos los chips flash actuales requieren solo un único voltaje de suministro y producen los altos voltajes que se requieren utilizando bombas de carga en el chip .

Más de la mitad de la energía que utiliza un chip flash NAND de 1,8 V se pierde en la propia bomba de carga. Dado que los convertidores elevadores son inherentemente más eficientes que las bombas de carga, los investigadores que desarrollan SSD de bajo consumo han propuesto volver a los voltajes de suministro duales Vcc/Vpp utilizados en todos los primeros chips flash, impulsando el alto voltaje Vpp para todos los chips flash en un SSD con un único convertidor elevador externo compartido. [76] [77] [78] [79] [80] [81] [82] [83]

En naves espaciales y otros entornos de alta radiación, la bomba de carga en el chip es la primera parte del chip flash que falla, aunque las memorias flash seguirán funcionando (en modo de solo lectura) a niveles de radiación mucho más altos. [84]

En la memoria flash NOR, cada celda tiene un extremo conectado directamente a tierra y el otro extremo conectado directamente a una línea de bits. Esta disposición se denomina "memoria flash NOR" porque actúa como una compuerta NOR: cuando una de las líneas de palabras (conectadas al CG de la celda) se eleva, el transistor de almacenamiento correspondiente actúa para bajar la línea de bits de salida. La memoria flash NOR sigue siendo la tecnología preferida para aplicaciones integradas que requieren un dispositivo de memoria no volátil discreto. [ cita requerida ] Las bajas latencias de lectura características de los dispositivos NOR permiten tanto la ejecución directa de código como el almacenamiento de datos en un único producto de memoria. [85]

Una celda flash NOR de un solo nivel en su estado predeterminado es lógicamente equivalente a un valor binario "1", porque la corriente fluirá a través del canal bajo la aplicación de un voltaje apropiado a la compuerta de control, de modo que el voltaje de la línea de bits se reduzca. Una celda flash NOR se puede programar o configurar con un valor binario "0" mediante el siguiente procedimiento:

Para borrar una celda flash NOR (restableciéndola al estado "1"), se aplica un voltaje grande de polaridad opuesta entre el CG y el terminal de fuente, extrayendo los electrones del FG a través del efecto túnel de Fowler-Nordheim (efecto túnel FN). [86] Esto se conoce como borrado de fuente de compuerta negativa. Las memorias NOR más nuevas pueden borrar usando el borrado de canal de compuerta negativa, que polariza la línea de palabra en un bloque de celda de memoria NOR y el pozo P del bloque de celda de memoria para permitir que se realice el efecto túnel FN, borrando el bloque de celda. Las memorias más antiguas usaban el borrado de fuente, en el que se aplicaba un voltaje alto a la fuente y luego los electrones del FG se movían a la fuente. [87] [88] Los chips de memoria flash NOR modernos se dividen en segmentos de borrado (a menudo llamados bloques o sectores). La operación de borrado solo se puede realizar en base a bloques; todas las celdas en un segmento de borrado deben borrarse juntas. [89] Sin embargo, la programación de celdas NOR generalmente se puede realizar un byte o palabra a la vez.

La memoria flash NAND también utiliza transistores de compuerta flotante , pero están conectados de una manera similar a una compuerta NAND : varios transistores están conectados en serie y la línea de bits se baja solo si todas las líneas de palabras se suben (por encima del VT de los transistores ) . Estos grupos se conectan luego a través de algunos transistores adicionales a una matriz de líneas de bits de estilo NOR de la misma manera que los transistores individuales están vinculados en la memoria flash NOR.

En comparación con la memoria flash NOR, la sustitución de transistores individuales por grupos enlazados en serie añade un nivel adicional de direccionamiento. Mientras que la memoria flash NOR puede direccionar la memoria por página y luego por palabra, la memoria flash NAND puede direccionarla por página, palabra y bit. El direccionamiento a nivel de bit es adecuado para aplicaciones de serie de bits (como la emulación de disco duro), que acceden solo a un bit a la vez. Las aplicaciones de ejecución en el lugar , por otro lado, requieren que se acceda a cada bit de una palabra simultáneamente. Esto requiere direccionamiento a nivel de palabra. En cualquier caso, tanto los modos de direccionamiento de bits como de palabras son posibles con la memoria flash NOR o NAND.

Para leer los datos, primero se selecciona el grupo deseado (de la misma manera que se selecciona un solo transistor de una matriz NOR). A continuación, la mayoría de las líneas de palabras se elevan por encima de V T2 , mientras que una de ellas se eleva hasta V I . El grupo en serie conducirá (y bajará la línea de bits) si el bit seleccionado no se ha programado.

A pesar de los transistores adicionales, la reducción de los cables de tierra y las líneas de bits permite un diseño más denso y una mayor capacidad de almacenamiento por chip. (Los cables de tierra y las líneas de bits son en realidad mucho más anchos que las líneas en los diagramas). Además, normalmente se permite que la memoria flash NAND contenga una cierta cantidad de fallas (se espera que la memoria flash NOR, como se usa para una ROM BIOS , esté libre de fallas). Los fabricantes intentan maximizar la cantidad de almacenamiento utilizable reduciendo el tamaño de los transistores o celdas, sin embargo, la industria puede evitar esto y lograr mayores densidades de almacenamiento por chip utilizando NAND 3D, que apila celdas una sobre otra.

Las celdas flash NAND se leen analizando su respuesta a varios voltajes. [72]

La memoria flash NAND utiliza la inyección de túnel para escribir y la liberación de túnel para borrar. La memoria flash NAND constituye el núcleo de los dispositivos de almacenamiento USB extraíbles conocidos como unidades flash USB , así como de la mayoría de los formatos de tarjetas de memoria y unidades de estado sólido disponibles en la actualidad.

La estructura jerárquica de la memoria flash NAND comienza en el nivel de celdas, que establece cadenas, luego páginas, bloques, planos y, por último, una matriz. Una cadena es una serie de celdas NAND conectadas en la que la fuente de una celda está conectada al drenaje de la siguiente. Según la tecnología NAND, una cadena consta normalmente de entre 32 y 128 celdas NAND. Las cadenas se organizan en páginas que, a su vez, se organizan en bloques en los que cada cadena está conectada a una línea separada denominada línea de bits. Todas las celdas con la misma posición en la cadena están conectadas a través de las puertas de control mediante una línea de palabras. Un plano contiene una cierta cantidad de bloques que están conectados a través de la misma línea de bits. Una matriz flash consta de uno o más planos y de los circuitos periféricos necesarios para realizar todas las operaciones de lectura, escritura y borrado.

La arquitectura de la memoria flash NAND permite leer y programar (escribir) datos en páginas, normalmente de entre 4 KiB y 16 KiB de tamaño, pero solo se pueden borrar a nivel de bloques enteros que constan de varias páginas. Cuando se borra un bloque, todas las celdas se establecen lógicamente en 1. Los datos solo se pueden programar en una sola pasada en una página de un bloque que se borró. El proceso de programación establece una o más celdas de 1 a 0. Cualquier celda que se haya establecido en 0 mediante programación solo se puede restablecer a 1 borrando todo el bloque. Esto significa que antes de poder programar nuevos datos en una página que ya contiene datos, el contenido actual de la página más los nuevos datos se deben copiar en una nueva página borrada. Si hay una página borrada adecuada disponible, los datos se pueden escribir en ella inmediatamente. Si no hay ninguna página borrada disponible, se debe borrar un bloque antes de copiar los datos a una página de ese bloque. La página antigua se marca entonces como no válida y está disponible para borrar y reutilizar. [90] Esto es diferente de la vista LBA del sistema operativo , por ejemplo, si el sistema operativo escribe 1100 0011 en el dispositivo de almacenamiento flash (como SSD ), los datos realmente escritos en la memoria flash pueden ser 0011 1100.

La memoria NAND vertical (V-NAND) o 3D NAND apila las celdas de memoria verticalmente y utiliza una arquitectura flash de trampa de carga . Las capas verticales permiten densidades de bits de área más grandes sin requerir celdas individuales más pequeñas. [91] También se vende bajo la marca comercial BiCS Flash , que es una marca comercial de Kioxia Corporation (anteriormente Toshiba Memory Corporation). La 3D NAND fue anunciada por primera vez por Toshiba en 2007. [53] La V-NAND fue fabricada comercialmente por primera vez por Samsung Electronics en 2013. [54] [55] [92] [93]

La memoria V-NAND utiliza una geometría flash de trampa de carga (que fue introducida comercialmente en 2002 por AMD y Fujitsu ) [52] que almacena la carga en una película de nitruro de silicio incrustada . Dicha película es más robusta contra defectos puntuales y se puede hacer más gruesa para contener una mayor cantidad de electrones. La memoria V-NAND envuelve una celda de trampa de carga plana en una forma cilíndrica. [91] A partir de 2020, las memorias flash 3D NAND de Micron e Intel utilizan en cambio puertas flotantes, sin embargo, las memorias 3D NAND de 128 capas y superiores de Micron utilizan una estructura de trampa de carga convencional, debido a la disolución de la asociación entre Micron e Intel. La memoria flash 3D NAND con trampa de carga es más delgada que la NAND 3D con puerta flotante. En la NAND 3D con puerta flotante, las celdas de memoria están completamente separadas entre sí, mientras que en la NAND 3D con trampa de carga, los grupos verticales de celdas de memoria comparten el mismo material de nitruro de silicio. [94]

Una celda de memoria individual está formada por una capa plana de polisilicio que contiene un orificio lleno de múltiples cilindros verticales concéntricos. La superficie de polisilicio del orificio actúa como electrodo de compuerta. El cilindro de dióxido de silicio más externo actúa como dieléctrico de compuerta, envolviendo un cilindro de nitruro de silicio que almacena carga, que a su vez envuelve un cilindro de dióxido de silicio como dieléctrico de túnel que rodea una varilla central de polisilicio conductor que actúa como canal conductor. [91]

Las celdas de memoria en diferentes capas verticales no interfieren entre sí, ya que las cargas no pueden moverse verticalmente a través del medio de almacenamiento de nitruro de silicio, y los campos eléctricos asociados con las puertas están estrechamente confinados dentro de cada capa. La colección vertical es eléctricamente idéntica a los grupos enlazados en serie en los que se configura la memoria flash NAND convencional. [91] También existe el apilamiento en cadena, que construye varias matrices o "enchufes" de memoria NAND 3D [95] por separado, pero apiladas juntas para crear un producto con un mayor número de capas NAND 3D en una sola matriz. A menudo, se apilan dos o 3 matrices. La desalineación entre los enchufes es del orden de 30 a 10 nm. [61] [96] [97]

El crecimiento de un grupo de celdas V-NAND comienza con una pila alterna de capas conductoras (dopadas) de polisilicio y capas aislantes de dióxido de silicio. [91]

El siguiente paso es formar un agujero cilíndrico a través de estas capas. En la práctica, un chip V-NAND de 128 Gbit con 24 capas de celdas de memoria requiere alrededor de 2.900 millones de agujeros de este tipo. A continuación, la superficie interior del agujero recibe múltiples capas, primero dióxido de silicio, luego nitruro de silicio y luego una segunda capa de dióxido de silicio. Por último, el agujero se rellena con polisilicio conductor (dopado). [91]

A partir de 2013, [update]la arquitectura flash V-NAND permite operaciones de lectura y escritura dos veces más rápidas que la NAND convencional y puede durar hasta 10 veces más, mientras consume un 50 por ciento menos de energía. Ofrecen una densidad de bits física comparable utilizando litografía de 10 nm, pero pueden ser capaces de aumentar la densidad de bits hasta en dos órdenes de magnitud, dado el uso de V-NAND de hasta varios cientos de capas. [91] A partir de 2020, Samsung está desarrollando chips V-NAND con 160 capas. [98] A medida que aumenta el número de capas, la capacidad y la resistencia de la memoria flash pueden aumentar.

El costo de la oblea de una NAND 3D es comparable con el de una memoria flash NAND plana de menor escala (32 nm o menos). [99] Sin embargo, con el escalamiento de la NAND plana que se detiene en 16 nm, la reducción del costo por bit puede continuar con la NAND 3D comenzando con 16 capas. Sin embargo, debido a la pared lateral no vertical del orificio grabado a través de las capas, incluso una ligera desviación conduce a un costo mínimo de bit, es decir, una regla de diseño equivalente mínima (o densidad máxima), para una cantidad dada de capas; este número de capas de costo mínimo de bit disminuye para un diámetro de orificio menor. [100]

Una limitación de la memoria flash es que sólo se puede borrar un bloque a la vez. Esto generalmente establece todos los bits del bloque en 1. A partir de un bloque recién borrado, se puede programar cualquier ubicación dentro de ese bloque. Sin embargo, una vez que un bit se ha establecido en 0, sólo borrando el bloque entero se puede volver a cambiar a 1. En otras palabras, la memoria flash (específicamente la memoria flash NOR) ofrece operaciones de lectura y programación de acceso aleatorio, pero no ofrece operaciones de reescritura o borrado de acceso aleatorio arbitrario. Sin embargo, se puede reescribir una ubicación siempre que los bits 0 del nuevo valor sean un superconjunto de los valores sobrescritos. Por ejemplo, un valor de nibble puede borrarse a 1111, y luego escribirse como 1110. Las escrituras sucesivas a ese nibble pueden cambiarlo a 1010, luego a 0010 y finalmente a 0000. Básicamente, el borrado establece todos los bits en 1, y la programación solo puede borrar bits a 0. [101] Algunos sistemas de archivos diseñados para dispositivos flash hacen uso de esta capacidad de reescritura, por ejemplo YAFFS1 , para representar metadatos del sector. Otros sistemas de archivos flash, como YAFFS2 , nunca hacen uso de esta capacidad de "reescritura"; realizan mucho trabajo adicional para cumplir con una "regla de escritura única".

Aunque las estructuras de datos en la memoria flash no se pueden actualizar de forma completamente general, esto permite "eliminar" los miembros marcándolos como no válidos. Es posible que sea necesario modificar esta técnica para dispositivos de celdas de varios niveles , donde una celda de memoria contiene más de un bit.

Los dispositivos flash comunes, como las unidades flash USB y las tarjetas de memoria, proporcionan solo una interfaz a nivel de bloque, o capa de traducción flash (FTL), que escribe en una celda diferente cada vez para nivelar el dispositivo. Esto evita la escritura incremental dentro de un bloque; sin embargo, ayuda a que el dispositivo no se desgaste prematuramente debido a patrones de escritura intensivos.

Los datos almacenados en las celdas flash se pierden constantemente debido a la pérdida de electrones [ se necesita una definición ] . La tasa de pérdida aumenta exponencialmente a medida que aumenta la temperatura absoluta . Por ejemplo: para una flash NOR de 45 nm, a las 1000 horas, la pérdida de voltaje umbral (Vt) a 25 °C es aproximadamente la mitad que a 90 °C. [102]

Otra limitación es que la memoria flash tiene un número finito de ciclos de borrado de programas (normalmente escritos como ciclos P/E). [103] [104] Micron Technology y Sun Microsystems anunciaron un chip de memoria flash SLC NAND con capacidad para 1.000.000 de ciclos P/E el 17 de diciembre de 2008. [105]

El conteo de ciclos garantizado puede aplicarse solo al bloque cero (como es el caso de los dispositivos NAND TSOP ) o a todos los bloques (como en NOR). Este efecto se mitiga en algunos firmware de chip o controladores de sistemas de archivos contando las escrituras y reasignando dinámicamente los bloques para distribuir las operaciones de escritura entre sectores; esta técnica se llama nivelación de desgaste . Otro enfoque es realizar la verificación de escritura y reasignar los sectores de repuesto en caso de falla de escritura, una técnica llamada administración de bloques defectuosos (BBM). Para dispositivos de consumo portátiles, estas técnicas de administración del desgaste generalmente extienden la vida útil de la memoria flash más allá de la vida útil del dispositivo en sí, y cierta pérdida de datos puede ser aceptable en estas aplicaciones. Sin embargo, para el almacenamiento de datos de alta confiabilidad, no es aconsejable usar memoria flash que tendría que pasar por una gran cantidad de ciclos de programación. Esta limitación también existe para aplicaciones de "solo lectura" como clientes ligeros y enrutadores , que se programan solo una vez o como máximo unas pocas veces durante su vida útil, debido a la perturbación de lectura (ver a continuación).

En diciembre de 2012, los ingenieros taiwaneses de Macronix revelaron su intención de anunciar en la reunión de dispositivos electrónicos internacionales IEEE de 2012 que habían descubierto cómo mejorar los ciclos de lectura/escritura de almacenamiento flash NAND de 10.000 a 100 millones de ciclos utilizando un proceso de "autocuración" que utilizaba un chip flash con "calentadores integrados que podían recocer pequeños grupos de celdas de memoria". [106] El recocido térmico integrado debía reemplazar el ciclo de borrado habitual por un proceso local de alta temperatura que no solo borraba la carga almacenada, sino que también reparaba la tensión inducida por electrones en el chip, lo que daba como resultado ciclos de escritura de al menos 100 millones. [107] El resultado era un chip que podía borrarse y reescribirse una y otra vez, incluso cuando teóricamente debería averiarse. Sin embargo, por muy prometedor que pudiera haber sido el avance de Macronix para la industria móvil, no había planes para lanzar un producto comercial con esta capacidad en un futuro próximo. [108]

El método utilizado para leer la memoria flash NAND puede provocar que las celdas cercanas en el mismo bloque de memoria cambien con el tiempo (se programen). Esto se conoce como alteración de lectura. El número umbral de lecturas se encuentra generalmente en los cientos de miles de lecturas entre las operaciones de borrado intermedias. Si se lee continuamente desde una celda, esa celda no fallará, sino que una de las celdas circundantes lo hará en una lectura posterior. Para evitar el problema de alteración de lectura, el controlador flash generalmente contará el número total de lecturas de un bloque desde el último borrado. Cuando el recuento excede un límite objetivo, el bloque afectado se copia a un nuevo bloque, se borra y luego se libera al grupo de bloques. El bloque original queda como nuevo después del borrado. Sin embargo, si el controlador flash no interviene a tiempo, se producirá un error de alteración de lectura con posible pérdida de datos si los errores son demasiado numerosos para corregirlos con un código de corrección de errores . [109] [110] [111]

La mayoría de los circuitos integrados flash vienen en encapsulados de matriz de rejilla de bolas (BGA), e incluso los que no lo tienen suelen montarse en una PCB junto a otros encapsulados BGA. Después del ensamblaje de la PCB , las placas con encapsulados BGA suelen someterse a rayos X para ver si las bolas están haciendo las conexiones adecuadas con el pad adecuado o si es necesario volver a trabajar en el BGA . Estos rayos X pueden borrar bits programados en un chip flash (convertir bits "0" programados en bits "1" borrados). Los bits borrados (bits "1") no se ven afectados por los rayos X. [112] [113]

Algunos fabricantes están fabricando ahora dispositivos de memoria SD [114] y USB [115] a prueba de rayos X.

La interfaz de bajo nivel para chips de memoria flash difiere de la de otros tipos de memoria como DRAM , ROM y EEPROM , que admiten alterabilidad de bits (tanto de cero a uno como de uno a cero) y acceso aleatorio a través de buses de direcciones accesibles externamente .

La memoria NOR tiene un bus de direcciones externo para lectura y programación. En la memoria NOR, la lectura y la programación son de acceso aleatorio, y el desbloqueo y el borrado se realizan por bloques. En la memoria NAND, la lectura y la programación se realizan por páginas, y el desbloqueo y el borrado se realizan por bloques.

La lectura desde una memoria flash NOR es similar a la lectura desde una memoria de acceso aleatorio, siempre que la dirección y el bus de datos estén correctamente asignados. Debido a esto, la mayoría de los microprocesadores pueden usar la memoria flash NOR como memoria de ejecución en el lugar (XIP), [116] lo que significa que los programas almacenados en la memoria flash NOR se pueden ejecutar directamente desde la memoria flash NOR sin necesidad de ser copiados primero en la RAM. La memoria flash NOR se puede programar de manera similar a la lectura mediante acceso aleatorio. La programación cambia los bits de un uno lógico a un cero. Los bits que ya son cero se dejan sin cambios. El borrado debe realizarse un bloque a la vez y restablece todos los bits del bloque borrado a uno. Los tamaños de bloque típicos son 64, 128 o 256 KiB .

La gestión de bloques defectuosos es una característica relativamente nueva en los chips NOR. En los dispositivos NOR más antiguos que no admiten la gestión de bloques defectuosos, el software o el controlador del dispositivo que controla el chip de memoria debe corregir los bloques que se desgastan o el dispositivo dejará de funcionar de manera confiable.

Los comandos específicos que se utilizan para bloquear, desbloquear, programar o borrar las memorias NOR difieren según el fabricante. Para evitar la necesidad de un software de controlador exclusivo para cada dispositivo fabricado, los comandos especiales de Interfaz de memoria flash común (CFI) permiten que el dispositivo se identifique a sí mismo y a sus parámetros operativos críticos.

Además de su uso como ROM de acceso aleatorio, la memoria flash NOR también se puede utilizar como dispositivo de almacenamiento, aprovechando la programación de acceso aleatorio. Algunos dispositivos ofrecen la funcionalidad de lectura y escritura, de modo que el código continúa ejecutándose incluso mientras se realiza un programa o una operación de borrado en segundo plano. Para escrituras de datos secuenciales, los chips flash NOR suelen tener velocidades de escritura lentas, en comparación con las memorias flash NAND.

La memoria flash NOR típica no necesita un código de corrección de errores . [117]

La arquitectura flash NAND fue introducida por Toshiba en 1989. [118] Se accede a estas memorias de forma muy similar a los dispositivos de bloque , como los discos duros. Cada bloque consta de varias páginas. Las páginas suelen tener un tamaño de 512, [119] 2048 o 4096 bytes. Asociados a cada página hay unos pocos bytes (normalmente 1/32 del tamaño de los datos) que se pueden utilizar para el almacenamiento de una suma de comprobación del código de corrección de errores (ECC) .

Los tamaños de bloque típicos incluyen:

Las memorias flash NAND modernas pueden tener un tamaño de bloque de borrado de entre 1 MiB y 128 MiB. Mientras que la lectura y la programación se realizan en base a páginas, el borrado solo se puede realizar en base a bloques. [122] Debido a que cambiar una celda de 0 a 1 necesita borrar el bloque completo, no solo modificar algunas páginas, modificar los datos de un bloque puede requerir un proceso de lectura-borrado-escritura, y los nuevos datos en realidad se mueven a otro bloque. Además, en un SSD NVM Express Zoned Namespaces, generalmente se usa el tamaño del bloque flash como el tamaño de la zona.

Los dispositivos NAND también requieren la gestión de bloques defectuosos por parte del software del controlador del dispositivo o de un chip controlador independiente. Algunas tarjetas SD, por ejemplo, incluyen circuitos de controlador para realizar la gestión de bloques defectuosos y la nivelación del desgaste . Cuando un software de alto nivel accede a un bloque lógico, el controlador o el controlador del dispositivo lo asigna a un bloque físico. Se pueden reservar varios bloques en el chip flash para almacenar tablas de asignación para tratar los bloques defectuosos, o el sistema puede simplemente verificar cada bloque al encenderse para crear un mapa de bloques defectuosos en la RAM. La capacidad de memoria general se reduce gradualmente a medida que se marcan más bloques como defectuosos.

La NAND se basa en el ECC para compensar los bits que pueden fallar espontáneamente durante el funcionamiento normal del dispositivo. Un ECC típico corregirá un error de un bit en cada 2048 bits (256 bytes) utilizando 22 bits de ECC, o un error de un bit en cada 4096 bits (512 bytes) utilizando 24 bits de ECC. [123] Si el ECC no puede corregir el error durante la lectura, aún puede detectar el error. Al realizar operaciones de borrado o programación, el dispositivo puede detectar bloques que no se pueden programar o borrar y marcarlos como defectuosos. Luego, los datos se escriben en un bloque diferente, que está en buen estado, y se actualiza el mapa de bloques defectuosos.

Los códigos Hamming son los códigos ECC más utilizados para las memorias flash NAND SLC. Los códigos Reed–Solomon y los códigos BCH (códigos Bose–Chaudhuri–Hocquenghem) son los códigos ECC más utilizados para las memorias flash NAND MLC. Algunos chips flash NAND MLC generan internamente los códigos de corrección de errores BCH adecuados. [117]

La mayoría de los dispositivos NAND se envían de fábrica con algunos bloques defectuosos. Estos suelen marcarse según una estrategia específica de marcado de bloques defectuosos. Al permitir algunos bloques defectuosos, los fabricantes logran rendimientos mucho mayores de los que serían posibles si se tuviera que verificar que todos los bloques están en buenas condiciones. Esto reduce significativamente los costos de la memoria flash NAND y solo disminuye ligeramente la capacidad de almacenamiento de las piezas.

Al ejecutar software desde memorias NAND, se suelen utilizar estrategias de memoria virtual : primero se deben paginar o copiar los contenidos de la memoria en la RAM asignada a la memoria y ejecutarlos allí (lo que da lugar a la combinación habitual de NAND + RAM). Una unidad de gestión de memoria (MMU) en el sistema resulta útil, pero esto también se puede lograr con superposiciones . Por este motivo, algunos sistemas utilizarán una combinación de memorias NOR y NAND, donde una memoria NOR más pequeña se utiliza como ROM de software y una memoria NAND más grande se particiona con un sistema de archivos para su uso como área de almacenamiento de datos no volátil.

La NAND sacrifica las ventajas de acceso aleatorio y ejecución en el lugar de la NOR. La NAND es más adecuada para sistemas que requieren almacenamiento de datos de alta capacidad. Ofrece densidades más altas, mayores capacidades y menor costo. Tiene borrados más rápidos, escrituras secuenciales y lecturas secuenciales.

Un grupo llamado Open NAND Flash Interface Working Group (ONFI) ha desarrollado una interfaz de bajo nivel estandarizada para chips NAND flash. Esto permite la interoperabilidad entre dispositivos NAND compatibles de diferentes proveedores. La versión 1.0 de la especificación ONFI [124] se publicó el 28 de diciembre de 2006. Especifica:

El grupo ONFI cuenta con el apoyo de los principales fabricantes de memoria flash NAND, incluidos Hynix , Intel , Micron Technology y Numonyx , así como de los principales fabricantes de dispositivos que incorporan chips flash NAND. [125]

Dos importantes fabricantes de dispositivos flash, Toshiba y Samsung , han optado por utilizar una interfaz de su propio diseño conocida como Toggle Mode (y ahora Toggle). Esta interfaz no es compatible pin a pin con la especificación ONFI. El resultado es que un producto diseñado para los dispositivos de un proveedor puede no ser capaz de utilizar los dispositivos de otro proveedor. [126]

Un grupo de proveedores, entre ellos Intel , Dell y Microsoft , formó un grupo de trabajo de interfaz de controlador de host de memoria no volátil (NVMHCI). [127] El objetivo del grupo es proporcionar interfaces de programación de hardware y software estándar para subsistemas de memoria no volátil, incluido el dispositivo de "caché flash" conectado al bus PCI Express .

Las memorias flash NOR y NAND se diferencian en dos aspectos importantes:

Las memorias flash NOR [134] y NAND obtienen sus nombres de la estructura de las interconexiones entre las celdas de memoria. [135] En las memorias flash NOR, las celdas están conectadas en paralelo a las líneas de bits, lo que permite que las celdas se lean y programen individualmente. [136] La conexión en paralelo de las celdas se asemeja a la conexión en paralelo de los transistores en una compuerta NOR CMOS. [137] En las memorias flash NAND, las celdas están conectadas en serie, [136] asemejándose a una compuerta NAND CMOS. Las conexiones en serie consumen menos espacio que las paralelas, lo que reduce el costo de las memorias flash NAND. [136] Por sí solas, no impiden que las celdas NAND se lean y programen individualmente. [ cita requerida ]

Cada celda flash NOR es más grande que una celda flash NAND – 10 F 2 vs 4 F 2 – [ vago ] incluso cuando se utiliza exactamente la misma fabricación de dispositivo semiconductor y por lo tanto cada transistor, contacto, etc. es exactamente del mismo tamaño – porque las celdas flash NOR requieren un contacto metálico separado para cada celda. [138] [139]

Debido a la conexión en serie y la eliminación de los contactos de línea de palabra, una gran red de celdas de memoria flash NAND ocupará quizás solo el 60% del área de las celdas NOR equivalentes [140] (asumiendo la misma resolución de proceso CMOS , por ejemplo, 130 nm , 90 nm o 65 nm). Los diseñadores de flash NAND se dieron cuenta de que el área de un chip NAND, y por lo tanto el costo, podría reducirse aún más eliminando la dirección externa y los circuitos del bus de datos. En cambio, los dispositivos externos podrían comunicarse con flash NAND a través de registros de datos y comandos de acceso secuencial, que recuperarían y emitirían internamente los datos necesarios. Esta elección de diseño hizo imposible el acceso aleatorio a la memoria flash NAND, pero el objetivo de la memoria flash NAND era reemplazar los discos duros mecánicos , no reemplazar las ROM.

Los primeros teléfonos GSM y muchos teléfonos con funciones básicas tenían memoria flash NOR, desde la cual se podían ejecutar instrucciones del procesador directamente en una arquitectura de ejecución en el lugar y permitía tiempos de arranque cortos. Con los teléfonos inteligentes, se adoptó la memoria flash NAND, ya que tiene mayores capacidades de almacenamiento y menores costos, pero causa tiempos de arranque más largos porque las instrucciones no se pueden ejecutar directamente desde ella y deben copiarse primero a la memoria RAM antes de la ejecución. [141]

La resistencia de escritura de las memorias flash NOR de puerta flotante SLC es normalmente igual o mayor que la de las memorias flash NAND, mientras que las memorias flash NOR y NAND de MLC tienen capacidades de resistencia similares. Se proporcionan ejemplos de clasificaciones de ciclos de resistencia que figuran en las hojas de datos de las memorias flash NAND y NOR, así como en los dispositivos de almacenamiento que utilizan memoria flash. [143]

Sin embargo, mediante la aplicación de ciertos algoritmos y paradigmas de diseño, como la nivelación del desgaste y el sobreaprovisionamiento de memoria , la resistencia de un sistema de almacenamiento se puede ajustar para satisfacer requisitos específicos. [174]

Para calcular la longevidad de la memoria flash NAND, se debe tener en cuenta el tamaño del chip de memoria, el tipo de memoria (p. ej., SLC/MLC/TLC) y el patrón de uso. La memoria NAND industrial y la memoria NAND para servidores tienen demanda debido a su capacidad, mayor resistencia y confiabilidad en entornos sensibles.

A medida que aumenta el número de bits por celda, el rendimiento y la vida útil de la memoria flash NAND pueden degradarse, lo que aumenta los tiempos de lectura aleatoria a 100 μs para TLC NAND, que es 4 veces el tiempo requerido en SLC NAND y el doble del tiempo requerido en MLC NAND para lecturas aleatorias. [74]

Debido a las características particulares de la memoria flash, se utiliza mejor con un controlador para realizar la nivelación del desgaste y la corrección de errores o con sistemas de archivos flash diseñados específicamente, que distribuyen las escrituras en el medio y se ocupan de los largos tiempos de borrado de los bloques flash NOR. El concepto básico detrás de los sistemas de archivos flash es el siguiente: cuando se debe actualizar el almacenamiento flash, el sistema de archivos escribirá una nueva copia de los datos modificados en un bloque nuevo, reasignará los punteros de archivo y luego borrará el bloque antiguo más tarde cuando tenga tiempo.

En la práctica, los sistemas de archivos flash se utilizan únicamente para dispositivos de tecnología de memoria (MTD), que son memorias flash integradas que no tienen un controlador. Las tarjetas de memoria flash extraíbles , los SSD, los chips eMMC / eUFS y las unidades flash USB tienen controladores integrados para realizar la nivelación del desgaste y la corrección de errores, por lo que el uso de un sistema de archivos flash específico puede no aportar ningún beneficio.

A menudo se colocan en serie o se apilan chips múltiples para lograr capacidades mayores [175] para su uso en dispositivos electrónicos de consumo, como reproductores multimedia o GPS . El escalamiento (aumento) de la capacidad de los chips flash solía seguir la ley de Moore porque se fabrican con muchas de las mismas técnicas y equipos de circuitos integrados . Desde la introducción de NAND 3D, el escalamiento ya no está necesariamente asociado con la ley de Moore, ya que ya no se utilizan transistores (celdas) cada vez más pequeños.

Los dispositivos de almacenamiento flash para el consumidor normalmente se anuncian con tamaños utilizables expresados como una pequeña potencia entera de dos (2, 4, 8, etc.) y una designación convencional de megabytes (MB) o gigabytes (GB); p. ej., 512 MB, 8 GB. Esto incluye los SSD comercializados como reemplazos de discos duros, de acuerdo con los discos duros tradicionales , que utilizan prefijos decimales . [176] Por lo tanto, un SSD marcado como "64 GB " tiene al menos 64 × 1000 3 bytes (64 GB). La mayoría de los usuarios tendrán ligeramente menos capacidad que esta disponible para sus archivos, debido al espacio ocupado por los metadatos del sistema de archivos y porque algunos sistemas operativos informan la capacidad de los SSD utilizando prefijos binarios que son algo más grandes que los prefijos convencionales.

Los chips de memoria flash que se encuentran en su interior tienen un tamaño que se expresa en múltiplos binarios estrictos, pero la capacidad total real de los chips no se puede utilizar en la interfaz de la unidad. Es considerablemente mayor que la capacidad anunciada para permitir la distribución de escrituras ( nivelación de desgaste ), el ahorro, los códigos de corrección de errores y otros metadatos que necesita el firmware interno del dispositivo.

En 2005, Toshiba y SanDisk desarrollaron un chip flash NAND capaz de almacenar 1 GB de datos utilizando tecnología de celdas multinivel (MLC), capaz de almacenar dos bits de datos por celda. En septiembre de 2005, Samsung Electronics anunció que había desarrollado el primer chip de 2 GB del mundo. [177]

En marzo de 2006, Samsung anunció discos duros flash con una capacidad de 4 GB, esencialmente el mismo orden de magnitud que los discos duros de portátiles más pequeños, y en septiembre de 2006, Samsung anunció un chip de 8 GB producido utilizando un proceso de fabricación de 40 nm. [178] En enero de 2008, SanDisk anunció la disponibilidad de sus tarjetas MicroSDHC de 16 GB y SDHC Plus de 32 GB. [179] [180]

Las unidades flash más recientes (a partir de 2012) tienen capacidades mucho mayores, con capacidad para 64, 128 y 256 GB. [181]

Un desarrollo conjunto de Intel y Micron permitirá la producción de memorias flash NAND de 32 capas de 3,5 terabytes (TB [ aclaración necesaria ] ) y SSD de tamaño estándar de 10 TB. El dispositivo incluye 5 paquetes de 16 matrices TLC de 48 GB, utilizando un diseño de celda de compuerta flotante. [182]

Los chips Flash continúan fabricándose con capacidades inferiores o cercanas a 1 MB (por ejemplo, para BIOS-ROM y aplicaciones integradas).

En julio de 2016, Samsung anunció el Samsung 850 EVO de 4 TB [ aclaración necesaria ] que utiliza su TLC 3D V-NAND de 48 capas y 256 Gbit. [183] En agosto de 2016, Samsung anunció un SSD SAS de 2,5 pulgadas y 32 TB basado en su TLC 3D V-NAND de 64 capas y 512 Gbit. Además, Samsung espera presentar SSD con hasta 100 TB de almacenamiento para 2020. [184]

Los dispositivos de memoria flash suelen ser mucho más rápidos en lectura que en escritura. [185] El rendimiento también depende de la calidad de los controladores de almacenamiento, que se vuelven más críticos cuando los dispositivos están parcialmente llenos. [ vago ] [185] Incluso cuando el único cambio en la fabricación es la reducción de la matriz, la ausencia de un controlador apropiado puede resultar en velocidades degradadas. [186]

La memoria flash serial es una memoria flash pequeña y de bajo consumo que proporciona solo acceso serial a los datos; en lugar de direccionar bytes individuales, el usuario lee o escribe grandes grupos contiguos de bytes en el espacio de direcciones en serie. El bus de interfaz periférica serial (SPI) es un protocolo típico para acceder al dispositivo. Cuando se incorpora a un sistema integrado , la memoria flash serial requiere menos cables en la PCB que las memorias flash paralelas, ya que transmite y recibe datos un bit a la vez. Esto puede permitir una reducción en el espacio de la placa, el consumo de energía y el costo total del sistema.

Hay varias razones por las que un dispositivo en serie, con menos pines externos que un dispositivo paralelo, puede reducir significativamente el costo general:

Existen dos tipos principales de memoria flash SPI. El primer tipo se caracteriza por tener bloques pequeños y un búfer de bloque SRAM interno que permite leer un bloque completo en el búfer, modificarlo parcialmente y luego volver a escribirlo (por ejemplo, la memoria flash Atmel AT45 DataFlash o la memoria flash NOR Page Erase de Micron Technology ). El segundo tipo tiene sectores más grandes; los sectores más pequeños que se encuentran normalmente en este tipo de memoria flash SPI son de 4 kB, pero pueden llegar a ser de 64 kB. Dado que este tipo de memoria flash SPI carece de un búfer SRAM interno, se debe leer y modificar el bloque completo antes de volver a escribirlo, lo que hace que su gestión sea lenta. Sin embargo, el segundo tipo es más económico que el primero y, por lo tanto, es una buena opción cuando la aplicación es el seguimiento de código.

Los dos tipos no son fácilmente intercambiables, ya que no tienen el mismo pinout y los conjuntos de comandos son incompatibles.

La mayoría de los FPGA se basan en celdas de configuración SRAM y requieren un dispositivo de configuración externo, a menudo un chip flash serial, para recargar el flujo de bits de configuración en cada ciclo de energía. [187]

Con la creciente velocidad de las CPU modernas, los dispositivos flash paralelos suelen ser mucho más lentos que el bus de memoria del ordenador al que están conectados. Por el contrario, la SRAM moderna ofrece tiempos de acceso inferiores a 10 ns , mientras que la SDRAM DDR2 ofrece tiempos de acceso inferiores a 20 ns. Debido a esto, a menudo es deseable copiar el código almacenado en la flash en la RAM; es decir, el código se copia de la flash a la RAM antes de la ejecución, de modo que la CPU pueda acceder a él a toda velocidad. El firmware del dispositivo se puede almacenar en un chip flash en serie y luego copiar en SDRAM o SRAM cuando se enciende el dispositivo. [188] El uso de un dispositivo flash en serie externo en lugar de flash en chip elimina la necesidad de un compromiso significativo del proceso (un proceso de fabricación que es bueno para la lógica de alta velocidad generalmente no es bueno para flash y viceversa). Una vez que se decide leer el firmware como un gran bloque, es común agregar compresión para permitir que se use un chip flash más pequeño. Desde 2005, muchos dispositivos usan flash NOR en serie para desaprobar el flash NOR paralelo para el almacenamiento de firmware. Las aplicaciones típicas de la memoria flash NOR en serie incluyen el almacenamiento de firmware para discos duros , BIOS , ROM opcionales de tarjetas de expansión , módems DSL , etc.

Una aplicación más reciente de la memoria flash es como reemplazo de los discos duros . La memoria flash no tiene las limitaciones mecánicas ni las latencias de los discos duros, por lo que una unidad de estado sólido (SSD) resulta atractiva si se tienen en cuenta la velocidad, el ruido, el consumo de energía y la fiabilidad. Las unidades flash están ganando terreno como dispositivos de almacenamiento secundario en dispositivos móviles; también se utilizan como sustitutos de los discos duros en ordenadores de sobremesa de alto rendimiento y algunos servidores con arquitecturas RAID y SAN .

Aún quedan algunos aspectos de los SSD basados en flash que los hacen poco atractivos. El costo por gigabyte de la memoria flash sigue siendo significativamente más alto que el de los discos duros. [189] Además, la memoria flash tiene un número finito de ciclos P/E ( programa/borrado ), pero esto parece estar actualmente bajo control ya que las garantías de los SSD basados en flash se están acercando a las de los discos duros actuales. [190] Además, los archivos eliminados en los SSD pueden permanecer durante un período de tiempo indefinido antes de ser sobrescritos por datos nuevos; las técnicas de borrado o destrucción o el software que funcionan bien en las unidades de disco duro magnético no tienen efecto en los SSD, lo que compromete la seguridad y el examen forense. Sin embargo, debido al llamado comando TRIM empleado por la mayoría de las unidades de estado sólido, que marca las direcciones de bloque lógico ocupadas por el archivo eliminado como no utilizadas para habilitar la recolección de basura , el software de recuperación de datos no puede restaurar los archivos eliminados de dichas unidades.

Para bases de datos relacionales u otros sistemas que requieren transacciones ACID , incluso una cantidad modesta de almacenamiento flash puede ofrecer grandes mejoras de velocidad en comparación con conjuntos de unidades de disco. [191]

En mayo de 2006, Samsung Electronics anunció dos PC basados en memoria flash, el Q1-SSD y el Q30-SSD, que se esperaba que estuvieran disponibles en junio de 2006, ambos usaban SSD de 32 GB y al menos inicialmente estaban disponibles sólo en Corea del Sur . [192] El lanzamiento del Q1-SSD y el Q30-SSD se retrasó y finalmente se envió a fines de agosto de 2006. [193]

El primer PC basado en memoria flash que estuvo disponible fue el Sony Vaio UX90, anunciado para pedidos anticipados el 27 de junio de 2006 y comenzó a enviarse en Japón el 3 de julio de 2006 con un disco duro de memoria flash de 16 GB. [194] A fines de septiembre de 2006, Sony actualizó la memoria flash del Vaio UX90 a 32 GB. [195]

En 2008, el primer MacBook Air incluía una unidad de estado sólido como opción y, a partir de 2010, todos los modelos se entregaron con una SSD. A partir de finales de 2011, como parte de la iniciativa Ultrabook de Intel , cada vez se entregan más portátiles ultradelgados con SSD de serie.

También existen técnicas híbridas como Hybrid Drive y ReadyBoost que intentan combinar las ventajas de ambas tecnologías, utilizando flash como un caché no volátil de alta velocidad para archivos en el disco que a menudo son referenciados, pero rara vez modificados, como archivos ejecutables de aplicaciones y sistemas operativos .

En los teléfonos inteligentes , los productos flash NAND se utilizan como dispositivos de almacenamiento de archivos, por ejemplo, eMMC y eUFS .

A partir de 2012, [update]existen intentos de utilizar la memoria flash como memoria principal del ordenador, DRAM . [196]

Los transistores de compuerta flotante en el dispositivo de almacenamiento flash retienen la carga que representa los datos. Esta carga se pierde gradualmente con el tiempo, lo que lleva a una acumulación de errores lógicos , también conocidos como " descomposición de bits " o "desvanecimiento de bits". [197]

No está claro cuánto tiempo se conservarán los datos en la memoria flash en condiciones de archivo (es decir, temperatura y humedad benignas con acceso poco frecuente con o sin reescritura profiláctica). Las hojas de datos de los microcontroladores " ATmega " basados en flash de Atmel suelen prometer tiempos de retención de 20 años a 85 °C (185 °F) y 100 años a 25 °C (77 °F). [198]

La capacidad de retención varía entre los tipos y modelos de almacenamiento flash. Cuando se suministra energía y está inactivo, la carga de los transistores que contienen los datos se actualiza de manera rutinaria mediante el firmware del almacenamiento flash. [197] La capacidad de retener datos varía entre los dispositivos de almacenamiento flash debido a las diferencias en el firmware, la redundancia de datos y los algoritmos de corrección de errores . [199]

Un artículo de la CMU de 2015 afirma que "los dispositivos flash actuales, que no requieren actualización de flash, tienen una edad de retención típica de 1 año a temperatura ambiente". Y ese tiempo de retención disminuye exponencialmente con el aumento de la temperatura. El fenómeno se puede modelar mediante la ecuación de Arrhenius . [200] [201]

Algunos FPGA se basan en celdas de configuración flash que se utilizan directamente como interruptores (programables) para conectar elementos internos entre sí, utilizando el mismo tipo de transistor de compuerta flotante que las celdas de almacenamiento de datos flash en los dispositivos de almacenamiento de datos. [187]

Una fuente afirma que, en 2008, la industria de la memoria flash representó alrededor de 9.100 millones de dólares en producción y ventas. Otras fuentes estiman que el mercado de la memoria flash alcanzó un tamaño de más de 20.000 millones de dólares en 2006, lo que representa más del ocho por ciento del mercado general de semiconductores y más del 34 por ciento del mercado total de memorias para semiconductores. [202] En 2012, el mercado se estimó en 26.800 millones de dólares. [203] Puede llevar hasta diez semanas producir un chip de memoria flash. [204]

Los siguientes fueron los mayores fabricantes de memoria flash NAND, al segundo trimestre de 2023. [205]

Samsung sigue siendo el mayor fabricante de memoria flash NAND a partir del primer trimestre de 2022. [208]

Además de los chips de memoria flash individuales, la memoria flash también está integrada en chips de microcontroladores (MCU) y dispositivos de sistema en chip (SoC). [225] La memoria flash está integrada en chips ARM , [225] que han vendido 150 mil millones de unidades en todo el mundo a partir de 2019 [update], [226] y en dispositivos de sistema en chip programables (PSoC), que han vendido 1.1 mil millones de unidades a partir de 2012. [update][ 227] Esto suma al menos 151.1 mil millones de chips MCU y SoC con memoria flash integrada, además de los 45.4 mil millones de ventas de chips flash individuales conocidos a partir de 2015 [update], lo que suma un total de al menos 196.5 mil millones de chips que contienen memoria flash.

Debido a su estructura relativamente simple y la alta demanda de mayor capacidad, la memoria flash NAND es la tecnología de escalado más agresivo entre los dispositivos electrónicos . La fuerte competencia entre los principales fabricantes solo se suma a la agresividad en la reducción de la regla de diseño de MOSFET de puerta flotante o el nodo de tecnología de proceso. [110] Si bien el cronograma de reducción esperado es un factor de dos cada tres años según la versión original de la ley de Moore , esto se ha acelerado recientemente en el caso de la memoria flash NAND a un factor de dos cada dos años.

A medida que el tamaño de las características MOSFET de las celdas de memoria flash alcanza el límite mínimo de 15-16 nm, se incrementarán aún más la densidad de memoria flash mediante TLC (3 bits/celda) combinado con el apilamiento vertical de planos de memoria NAND. La disminución de la resistencia y el aumento de las tasas de errores de bits incorregibles que acompañan a la reducción del tamaño de las características se pueden compensar con mecanismos de corrección de errores mejorados. [233] Incluso con estos avances, puede resultar imposible escalar económicamente la memoria flash a dimensiones cada vez más pequeñas a medida que se reduce la capacidad de retención de electrones. Se están investigando y desarrollando muchas tecnologías nuevas y prometedoras (como FeRAM , MRAM , PMC , PCM , ReRAM y otras) como posibles reemplazos más escalables para la memoria flash. [234]

La memoria flash se puede reprogramar hasta 100 veces.

Los dispositivos ofrecen funcionamiento con una sola fuente de alimentación (2,7 V a 3,6 V), arquitectura sectorial, algoritmos integrados, alto rendimiento y una garantía de resistencia de 1 000 000 de ciclos de programación/borrado.

El

PSoC

... utiliza un proceso Flash único:

SONOS

Los resultados de la calificación de confiabilidad muestran que la tasa de falla de retención de datos proyectada es mucho menor que 1 PPM durante 20 años a 85 °C o 100 años a 25 °C

Los envíos de unidades aumentaron un 64% en 1999 con respecto al año anterior y se prevé que aumenten un 44% hasta alcanzar los 1.800 millones de unidades en 2000.