La integridad de la señal o SI es un conjunto de medidas de la calidad de una señal eléctrica . En electrónica digital , un flujo de valores binarios se representa mediante una forma de onda de voltaje (o corriente). Sin embargo, las señales digitales son fundamentalmente analógicas por naturaleza y todas las señales están sujetas a efectos como ruido , distorsión y pérdida. En distancias cortas y a bajas tasas de bits, un simple conductor puede transmitir esto con suficiente fidelidad. A altas tasas de bits y en distancias más largas o a través de varios medios, varios efectos pueden degradar la señal eléctrica hasta el punto en que ocurren errores y el sistema o dispositivo falla. La ingeniería de integridad de señal es la tarea de analizar y mitigar estos efectos. Es una actividad importante en todos los niveles de empaquetado y ensamblaje de electrónica, desde las conexiones internas de un circuito integrado (CI), [1] pasando por el paquete , la placa de circuito impreso (PCB), la placa base y las conexiones entre sistemas. [2] Si bien hay algunos temas comunes en estos diversos niveles, también hay consideraciones prácticas, en particular el tiempo de vuelo de interconexión versus el período de bit, que causan diferencias sustanciales en el enfoque de la integridad de la señal para conexiones en chip versus conexiones de chip a chip.

Algunos de los principales problemas que preocupan a la integridad de la señal son el zumbido , la diafonía , el rebote de tierra , la distorsión , la pérdida de señal y el ruido de la fuente de alimentación .

La integridad de la señal involucra principalmente el desempeño eléctrico de los cables y otras estructuras de empaquetado utilizadas para mover señales dentro de un producto electrónico. Este desempeño es una cuestión de física básica y como tal ha permanecido relativamente sin cambios desde el comienzo de la señalización electrónica. El primer cable telegráfico transatlántico sufrió graves problemas de integridad de la señal , y el análisis de los problemas produjo muchas de las herramientas matemáticas que todavía se usan hoy para analizar problemas de integridad de la señal, como las ecuaciones del telegrafista . Productos tan antiguos como la central telefónica de barra transversal Western Electric (circa 1940), basada en el relé de resorte de alambre, sufrieron casi todos los efectos que vemos hoy: el zumbido, la diafonía, el rebote de tierra y el ruido de la fuente de alimentación que plagan los productos digitales modernos.

En las placas de circuitos impresos, la integridad de la señal se convirtió en una preocupación seria cuando los tiempos de transición (subida y bajada) de las señales comenzaron a ser comparables al tiempo de propagación a través de la placa. En términos muy generales, esto suele ocurrir cuando las velocidades del sistema superan unas pocas decenas de MHz. Al principio, solo unas pocas de las señales más importantes o de mayor velocidad necesitaban un análisis o diseño detallado. A medida que aumentaban las velocidades, una fracción cada vez mayor de señales necesitaban prácticas de análisis y diseño de SI. En los diseños de circuitos modernos (> 100 MHz), esencialmente todas las señales deben diseñarse teniendo en cuenta la SI.

Para los circuitos integrados, el análisis SI se hizo necesario como efecto de las reglas de diseño reducidas. En los primeros días de la era moderna de VLSI, el diseño y el diseño de circuitos de chips digitales eran procesos manuales. El uso de la abstracción y la aplicación de técnicas de síntesis automática han permitido desde entonces a los diseñadores expresar sus diseños utilizando lenguajes de alto nivel y aplicar un proceso de diseño automatizado para crear diseños muy complejos, ignorando en gran medida las características eléctricas de los circuitos subyacentes. Sin embargo, las tendencias de escalado (ver la ley de Moore ) trajeron los efectos eléctricos de nuevo al frente en los nodos de tecnología recientes. Con el escalado de la tecnología por debajo de 0,25 μm, los retrasos del cable se han vuelto comparables o incluso mayores que los retrasos de la compuerta. Como resultado, los retrasos del cable debían considerarse para lograr el cierre de tiempo . En las tecnologías nanométricas a 0,13 μm y por debajo, las interacciones no deseadas entre señales (por ejemplo, diafonía) se convirtieron en una consideración importante para el diseño digital. En estos nodos de tecnología, el rendimiento y la corrección de un diseño no se pueden asegurar sin considerar los efectos del ruido.

La mayor parte de este artículo trata sobre la SI en relación con la tecnología electrónica moderna, en particular el uso de circuitos integrados y tecnología de placas de circuito impreso . Sin embargo, los principios de la SI no son exclusivos de la tecnología de señalización utilizada. La SI existía mucho antes de la aparición de cualquiera de estas tecnologías y seguirá existiendo mientras persistan las comunicaciones electrónicas.

Los problemas de integridad de la señal en los circuitos integrados (CI) modernos pueden tener muchas consecuencias drásticas para los diseños digitales:

El costo de estos fallos es muy alto e incluye los costos de fotomáscara , los costos de ingeniería y el costo de oportunidad debido a la introducción tardía del producto. Por lo tanto, se han desarrollado herramientas de automatización del diseño electrónico (EDA) para analizar, prevenir y corregir estos problemas. [1] En los circuitos integrados , o CI, la principal causa de los problemas de integridad de la señal es la diafonía . En las tecnologías CMOS , esto se debe principalmente a la capacitancia de acoplamiento , pero en general puede ser causado por inductancia mutua , acoplamiento de sustrato , operación de compuerta no ideal y otras fuentes. Las soluciones normalmente implican cambiar los tamaños de los controladores y/o el espaciado de los cables.

En los circuitos analógicos, los diseñadores también se preocupan por el ruido que surge de fuentes físicas, como el ruido térmico , el ruido de parpadeo y el ruido de disparo . Estas fuentes de ruido, por un lado, presentan un límite inferior para la señal más pequeña que se puede amplificar y, por otro, definen un límite superior para la amplificación útil.

En los circuitos integrados digitales, el ruido en una señal de interés surge principalmente de los efectos de acoplamiento de la conmutación de otras señales. El aumento de la densidad de interconexión ha llevado a que cada cable tenga vecinos que están físicamente más cerca entre sí, lo que genera un aumento de la diafonía entre redes vecinas. A medida que los circuitos han seguido reduciéndose de acuerdo con la ley de Moore , varios efectos han conspirado para empeorar los problemas de ruido:

Estos efectos han aumentado las interacciones entre señales y han disminuido la inmunidad al ruido de los circuitos CMOS digitales. Esto ha llevado a que el ruido sea un problema importante para los circuitos integrados digitales que todo diseñador de chips digitales debe tener en cuenta antes de su puesta a punto . Hay varias preocupaciones que deben mitigarse:

Normalmente, un diseñador de circuitos integrados seguiría los siguientes pasos para la verificación SI:

Las herramientas modernas de integridad de señales para el diseño de circuitos integrados realizan todos estos pasos de forma automática y generan informes que dan al diseño un certificado de buena salud o una lista de problemas que deben solucionarse. Sin embargo, estas herramientas generalmente no se aplican en todo un circuito integrado, sino solo en señales de interés seleccionadas.

Una vez que se detecta un problema, es necesario solucionarlo. Las soluciones típicas para los problemas de los circuitos integrados en chip incluyen:

Cada una de estas correcciones puede causar otros problemas. Este tipo de problema debe abordarse como parte de los flujos de diseño y el cierre del diseño . Volver a analizar después de los cambios de diseño es una medida prudente.

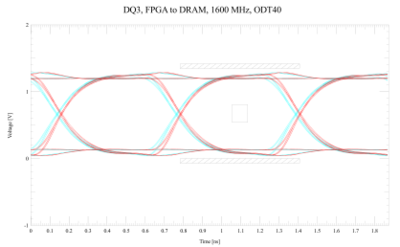

La terminación en chip (ODT) o impedancia controlada digitalmente (DCI [4] ) es una tecnología en la que la resistencia de terminación para la adaptación de impedancia en líneas de transmisión se ubica dentro de un chip semiconductor, en lugar de un dispositivo separado y discreto montado en una placa de circuito. La proximidad de la terminación con el receptor acorta el paso entre ambos, mejorando así la integridad general de la señal.

Para las conexiones cableadas, es importante comparar el tiempo de vuelo de interconexión con el período de bit para decidir si se necesita una conexión con impedancia coincidente o no.

El tiempo de vuelo del canal (retardo) de la interconexión es de aproximadamente 1 ns por cada 15 cm ( 6 pulgadas ) de línea de banda FR-4 (la velocidad de propagación depende del dieléctrico y la geometría). [5] Las reflexiones de pulsos anteriores en desajustes de impedancia se apagan después de unos pocos rebotes hacia arriba y hacia abajo de la línea (es decir, en el orden del tiempo de vuelo). A bajas velocidades de bits, los ecos se apagan por sí solos y, a mitad del pulso, no son una preocupación. La adaptación de impedancia no es necesaria ni deseable. Hay muchos tipos de placas de circuito distintas de FR-4, pero generalmente son más costosas de fabricar.

La suave tendencia hacia velocidades de bits más altas se aceleró drásticamente en 2004, con la introducción por parte de Intel del estándar PCI-Express . Siguiendo este ejemplo, la mayoría de los estándares de conexión de chip a chip experimentaron un cambio arquitectónico desde buses paralelos a enlaces serializador/deserializador ( SERDES ) llamados "carriles". Estos enlaces seriales eliminan el sesgo de reloj del bus paralelo y reducen el número de trazas y los efectos de acoplamiento resultantes, pero estas ventajas se obtienen a costa de un gran aumento en la velocidad de bits en los carriles y períodos de bits más cortos.

A velocidades de datos de varios gigabit/s, los diseñadores de enlaces deben considerar las reflexiones en los cambios de impedancia (por ejemplo, cuando las trazas cambian de nivel en las vías , consulte Líneas de transmisión ), el ruido inducido por conexiones vecinas densamente empaquetadas ( diafonía ) y la atenuación de alta frecuencia causada por el efecto pelicular en la traza metálica y la tangente de pérdida dieléctrica. Ejemplos de técnicas de mitigación para estas deficiencias son un rediseño de la geometría de la vía para garantizar una coincidencia de impedancia, el uso de señalización diferencial y el filtrado de preénfasis , respectivamente. [6] [7]

En estas nuevas velocidades de bits de varios gigabit/s, el período de bit es más corto que el tiempo de vuelo; los ecos de pulsos anteriores pueden llegar al receptor encima del pulso principal y corromperlo. En ingeniería de comunicaciones, esto se llama interferencia entre símbolos (ISI). En ingeniería de integridad de señal, generalmente se llama cierre de ojo (una referencia al desorden en el centro de un tipo de traza de osciloscopio llamado diagrama de ojo). Cuando el período de bit es más corto que el tiempo de vuelo, la eliminación de reflexiones utilizando técnicas clásicas de microondas como hacer coincidir la impedancia eléctrica del transmisor con la interconexión, las secciones de interconexión entre sí y la interconexión con el receptor, es crucial. La terminación con una fuente o carga es un sinónimo de hacer coincidir en los dos extremos. La impedancia de interconexión que se puede seleccionar está limitada por la impedancia del espacio libre ( ~377 Ω ), un factor de forma geométrico y por la raíz cuadrada de la constante dieléctrica relativa del relleno de línea de banda (normalmente FR-4, con una constante dieléctrica relativa de ~4). En conjunto, estas propiedades determinan la impedancia característica de la traza . 50 Ω es una opción conveniente para líneas de un solo extremo, [8] y 100 ohmios para diferenciales.

Como consecuencia de la baja impedancia requerida por la adaptación, las pistas de señal de PCB transportan mucha más corriente que sus contrapartes en chip. Esta corriente más grande induce diafonía principalmente en un modo magnético o inductivo en lugar de en un modo capacitivo. Para combatir esta diafonía, los diseñadores de PCB digitales deben tener muy en cuenta no solo la ruta de señal prevista para cada señal, sino también la ruta de la corriente de señal de retorno para cada señal. La señal en sí y su ruta de corriente de señal de retorno son igualmente capaces de generar diafonía inductiva. Los pares de pistas diferenciales ayudan a reducir estos efectos.

Una tercera diferencia entre la conexión en chip y la conexión de chip a chip tiene que ver con el tamaño de la sección transversal del conductor de señal, es decir, que los conductores de PCB son mucho más grandes (normalmente de 100 μm o más de ancho). Por lo tanto, las pistas de PCB tienen una pequeña resistencia en serie (normalmente 0,1 Ω/cm) en CC. Sin embargo, el componente de alta frecuencia del pulso se atenúa mediante una resistencia adicional debido al efecto pelicular y la tangente de pérdida dieléctrica asociada con el material de la PCB.

El desafío principal a menudo depende de si el proyecto es una aplicación de consumo impulsada por los costos o una aplicación de infraestructura impulsada por el rendimiento. [9] Suelen requerir una verificación extensa posterior al diseño (usando un simulador EM ) y una optimización del diseño previa al diseño (usando SPICE y un simulador de canal), respectivamente.

Los niveles de ruido en una traza/red dependen en gran medida de la topología de enrutamiento seleccionada. En una topología punto a punto, la señal se enruta desde el transmisor directamente al receptor (esto se aplica en PCIe , RapidIO , Gigabit Ethernet , DDR2 / DDR3 / DDR4 DQ/DQS, etc.). Una topología punto a punto tiene menos problemas de SI, ya que no se introducen grandes coincidencias de impedancia por las líneas T (una división bidireccional de una traza).

En el caso de interfaces en las que varios paquetes reciben datos de la misma línea (por ejemplo, con una configuración de placa base), la línea debe dividirse en algún punto para dar servicio a todos los receptores. Se considera que se producen algunos desajustes de impedancia y de stubs. Las interfaces multipaquete incluyen B LVDS , banco C/A DDR2/DDR3/DDR4, RS485 y bus CAN . Existen dos topologías principales de multipaquete: árbol y fly-by.

Existen herramientas EDA de propósito especial [12] que ayudan al ingeniero a realizar todos estos pasos en cada señal de un diseño, señalando problemas o verificando que el diseño esté listo para su fabricación. Al seleccionar qué herramienta es mejor para una tarea en particular, se deben considerar las características de cada una, como la capacidad (cuántos nodos o elementos), el rendimiento (velocidad de simulación), la precisión (qué tan buenos son los modelos), la convergencia (qué tan bueno es el solucionador), la capacidad (no lineal versus lineal, dependiente de la frecuencia versus independiente de la frecuencia, etc.) y la facilidad de uso.

Un diseñador de paquetes de circuitos integrados o de PCB elimina los problemas de integridad de la señal mediante estas técnicas:

Es posible que cada una de estas correcciones ocasione otros problemas. Este tipo de problema debe abordarse como parte de los flujos de diseño y el cierre del diseño .

{{cite book}}: |author=tiene nombre genérico ( ayuda ) Un estudio del campo de la automatización del diseño electrónico . Partes de la sección de CI de este artículo se derivaron (con permiso) del Volumen II, Capítulo 21, Consideraciones sobre el ruido en los CI digitales , de Vinod Kariat.Mantenimiento de CS1: varios nombres: lista de autores ( enlace )Para aplicaciones de consumo orientadas a los costes... [e]s tentador compactar [los buses paralelos], pero el riesgo es un fallo posterior al diseño... Para aplicaciones orientadas al rendimiento, los puntos críticos [son] la exploración del espacio de diseño previo al diseño...

...con el aumento continuo de las velocidades de reloj de los circuitos digitales, los ámbitos de la RF y los circuitos digitales están ahora más estrechamente vinculados que nunca.