En el ámbito de la electrónica digital , el sistema DIMS ( síntesis de mintérminos insensible al retardo ) [1] es una metodología de diseño asincrónica que realiza las suposiciones de tiempo más reducidas posibles. Suponiendo únicamente el modelo de retardo cuasi insensible al retardo , los diseños generados necesitan poca o ninguna prueba de riesgo de tiempo. La base de DIMS es el uso de dos cables para representar cada bit de datos. Esto se conoce como codificación de datos de doble carril. Las partes del sistema se comunican utilizando el protocolo asincrónico de cuatro fases inicial.

La construcción de puertas lógicas DIMS comprende la generación de todos los minterms posibles utilizando una fila de elementos C y luego reuniendo las salidas de estos utilizando puertas OR que generan las señales de salida verdadera y falsa. Con dos entradas de doble carril, la puerta estaría compuesta por cuatro elementos C de dos entradas. Una puerta de tres entradas utiliza ocho elementos C de tres entradas.

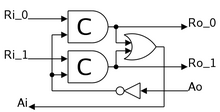

Los latches se construyen utilizando dos elementos C para almacenar los datos y una compuerta OR para reconocer la entrada una vez que los datos han sido bloqueados conectando como entradas los cables de salida de datos. El reconocimiento de la etapa de avance se invierte y se pasa a los elementos C para permitirles restablecerse una vez que se ha completado el cálculo. Este diseño de latch se conoce como "half latch". Otros latches asincrónicos proporcionan una mayor capacidad de datos y niveles de desacoplamiento.

Los diseños DIMS son grandes y lentos, pero tienen la ventaja de ser muy robustos.