La lógica de resistencia-transistor ( RTL ), a veces también conocida como lógica de transistor-resistencia ( TRL ), es una clase de circuitos digitales construidos utilizando resistencias como red de entrada y transistores de unión bipolar (BJT) como dispositivos de conmutación. RTL es la primera clase de circuito lógico digital transistorizado; fue sucedido por la lógica de diodo-transistor (DTL) y la lógica de transistor-transistor (TTL).

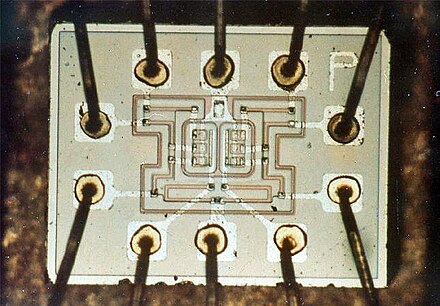

Los circuitos RTL se construyeron por primera vez con componentes discretos , pero en 1961 se convirtieron en la primera familia de lógica digital producida como un circuito integrado monolítico . Los circuitos integrados RTL se utilizaron en la Computadora de Orientación Apollo , cuyo diseño comenzó en 1961 y que voló por primera vez en 1966. [1]

Un interruptor de transistor bipolar es la puerta RTL ( inversor o puerta NOT) más simple que implementa la negación lógica . [2] Consiste en una etapa de emisor común con una resistencia de base conectada entre la base y la fuente de voltaje de entrada. La función de la resistencia base es expandir el rango de voltaje de entrada del transistor muy pequeño (aproximadamente 0,7 V) al nivel lógico "1" (aproximadamente 3,5 V) convirtiendo el voltaje de entrada en corriente. Su resistencia se establece mediante un compromiso: se elige lo suficientemente baja para saturar el transistor y lo suficientemente alta para obtener una alta resistencia de entrada. La función de la resistencia del colector es convertir la corriente del colector en voltaje; su resistencia se elige lo suficientemente alta como para saturar el transistor y lo suficientemente baja para obtener una resistencia de salida baja (alta distribución ).

Con dos o más resistencias base (R 3 y R 4 ) en lugar de una, el inversor se convierte en una puerta RTL NOR de dos entradas (consulte la figura de la derecha). La operación lógica OR se realiza aplicando consecutivamente las dos operaciones aritméticas de suma y comparación (la red de resistencias de entrada actúa como un sumador de voltaje paralelo con entradas igualmente ponderadas y la siguiente etapa de transistor de emisor común como comparador de voltaje con un umbral de aproximadamente 0,7 V). . La resistencia equivalente de todas las resistencias conectadas al "1" lógico y la resistencia equivalente de todas las resistencias conectadas al "0" lógico forman las dos patas de un divisor de voltaje compuesto que acciona el transistor. Las resistencias de base y el número de entradas se eligen (limitan) de modo que sólo un "1" lógico sea suficiente para crear un voltaje base-emisor que supere el umbral y, como resultado, saturar el transistor. Si todos los voltajes de entrada son bajos ("0" lógico), el transistor se corta. La resistencia desplegable R 1 polariza el transistor al umbral de encendido y apagado apropiado. La salida se invierte ya que el voltaje colector-emisor del transistor Q 1 se toma como salida y es alto cuando las entradas son bajas. Por tanto, la red resistiva analógica y la etapa del transistor analógico realizan la función lógica NOR. [3]

Las limitaciones de la puerta RTL NOR de un transistor se superan mediante la implementación RTL de múltiples transistores. Consiste en un conjunto de interruptores de transistores conectados en paralelo accionados por las entradas lógicas (consulte la figura de la derecha). En esta configuración, las entradas están completamente separadas y el número de entradas está limitado únicamente por la pequeña corriente de fuga de los transistores de corte en la salida lógica "1". La misma idea se utilizó más tarde para construir puertas DCTL , ECL , algunas TTL (7450, 7460), NMOS y CMOS .

Para garantizar la estabilidad y la salida predecible de los transistores bipolares, sus entradas de base (V b o voltaje del terminal de base) están polarizadas.

La principal ventaja de la tecnología RTL era que utilizaba una cantidad mínima de transistores. En los circuitos que utilizan componentes discretos, antes de los circuitos integrados, los transistores eran el componente más caro de producir. La producción inicial de lógica de circuitos integrados (como la de Fairchild en 1961) utilizó brevemente el mismo enfoque, pero rápidamente pasó a circuitos de mayor rendimiento, como la lógica de diodo-transistor y luego la lógica de transistor-transistor (a partir de 1963 en Sylvania Electric Products ), ya que los diodos y Los transistores no eran más caros que las resistencias del CI. [5]

La desventaja de RTL es su alta disipación de potencia cuando el transistor está encendido, debido a la corriente que fluye en el colector y las resistencias de la base. Esto requiere que se suministre más corriente y se elimine calor de los circuitos RTL. Por el contrario, los circuitos TTL con etapa de salida " tótem " minimizan ambos requisitos.

Otra limitación de RTL es su fan-in limitado : 3 entradas son el límite para muchos diseños de circuitos, antes de que pierda por completo la inmunidad al ruido utilizable. [ cita requerida ] Tiene un margen de ruido bajo . Lancaster dice que las puertas NOR RTL de circuito integrado (que tienen un transistor por entrada) pueden construirse con "cualquier número razonable" de entradas lógicas y da un ejemplo de una puerta NOR de 8 entradas. [6]

Una puerta RTL NOR de circuito integrado estándar puede controlar hasta otras 3 puertas similares. Alternativamente, tiene suficiente salida para controlar hasta 2 "búferes" RTL de circuito integrado estándar, cada uno de los cuales puede controlar hasta otras 25 puertas RTL NOR estándar. [6]

Varias empresas han aplicado los siguientes métodos de aceleración para RTL discreto.

La velocidad de conmutación de transistores ha aumentado constantemente desde las primeras computadoras transistorizadas hasta el presente. El Manual de transistores de GE (7.ª ed., p. 181, o 3.ª ed., p. 97 o ediciones intermedias) recomienda ganar velocidad utilizando transistores de mayor frecuencia, o condensadores, o un diodo desde la base hasta el colector ( retroalimentación negativa paralela ). para evitar la saturación. [7]

Colocar un capacitor en paralelo con cada resistencia de entrada disminuye el tiempo necesario para que una etapa impulsora polarice directamente la unión base-emisor de una etapa impulsada. Los ingenieros y técnicos utilizan "RCTL" (lógica de resistencia-condensador-transistor) para designar puertas equipadas con "condensadores de aceleración". Los circuitos de la computadora TX-0 del Laboratorio Lincoln incluían algunos RCTL. [8] Sin embargo, los métodos que involucraban condensadores no eran adecuados para circuitos integrados. [ cita necesaria ]

El uso de un alto voltaje de suministro del colector y la fijación de diodos disminuyeron el tiempo de carga de la capacitancia del cableado y de la base del colector. Esta disposición requería que un diodo sujetara el colector al nivel lógico de diseño. Este método también se aplicó a DTL discreto ( lógica de diodo-transistor ). [9]

Otro método que era familiar en los circuitos lógicos de dispositivos discretos utilizaba un diodo y una resistencia, un diodo de germanio y un diodo de silicio, o tres diodos en una disposición de retroalimentación negativa. Estas redes de diodos conocidas como varias abrazaderas de Baker redujeron el voltaje aplicado a la base cuando el colector se acercaba a la saturación. Debido a que el transistor se saturó menos, acumuló menos portadores de carga almacenados. Por lo tanto, se requirió menos tiempo para eliminar la carga almacenada durante el apagado del transistor. [7] Se aplicó un diodo de bajo voltaje dispuesto para evitar la saturación del transistor a familias lógicas integradas mediante el uso de diodos Schottky , como en Schottky TTL .

La función lógica la realiza la red de resistencias de entrada y la función inversa la realiza la configuración del transistor emisor común...