El Intel 8259 es un controlador de interrupciones programable (PIC) diseñado para los microprocesadores Intel 8085 y 8086. La pieza inicial fue 8259, una versión posterior con sufijo A era compatible con los procesadores 8086 o 8088. El 8259 combina múltiples fuentes de entrada de interrupción en una única salida de interrupción al microprocesador anfitrión, lo que extiende los niveles de interrupción disponibles en un sistema más allá de los uno o dos niveles que se encuentran en el chip del procesador. El 8259A era el controlador de interrupciones para el bus ISA en el IBM PC original y el IBM PC AT .

El 8259 se introdujo como parte de la familia MCS 85 de Intel en 1976. El 8259A se incluyó en la PC original introducida en 1981 y se mantuvo en la PC/XT cuando se introdujo en 1983. Se añadió un segundo 8259A con la introducción de la PC/AT . El 8259 ha coexistido con la arquitectura Intel APIC desde su introducción en las PC multiprocesador simétrico . Las PC modernas han comenzado a eliminar gradualmente el 8259A a favor de la arquitectura Intel APIC. Sin embargo, aunque ya no es un chip independiente, la interfaz 8259A todavía la proporciona el concentrador de controlador de plataforma o el puente sur en las placas base x86 modernas . [1]

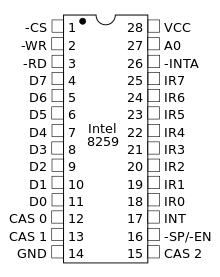

Los pines de señal principales de un 8259 son los siguientes: ocho líneas de entrada de solicitud de interrupción denominadas IRQ0 a IRQ7, una línea de salida de solicitud de interrupción denominada INTR, una línea de reconocimiento de interrupción denominada INTA, D0 a D7 para comunicar el nivel de interrupción o el desplazamiento del vector. Otras conexiones incluyen CAS0 a CAS2 para la conexión en cascada entre 8259.

Se pueden conectar en cascada hasta ocho 8259 esclavos a un 8259 maestro para proporcionar hasta 64 IRQ. Los 8259 se conectan en cascada conectando la línea INT de un 8259 esclavo a la línea IRQ de un 8259 maestro .

Las operaciones de fin de interrupción (EOI) admiten EOI específicas, EOI no específicas y EOI automáticas. Una EOI específica especifica el nivel de IRQ que está reconociendo en la ISR. Una EOI no específica restablece el nivel de IRQ en la ISR. La EOI automática restablece el nivel de IRQ en la ISR inmediatamente después de que se reconoce la interrupción.

El 8259A admite los modos de activación de interrupción de nivel y de flanco. También admite los modos de prioridad fija y prioridad rotativa.

El 8259 puede configurarse para funcionar con un 8080/8085 o un 8086/8088. En el 8086/8088, el controlador de interrupciones proporcionará un número de interrupción en el bus de datos cuando se produzca una interrupción. El ciclo de interrupción del 8080/8085 emitirá tres bytes en el bus de datos (que corresponden a una instrucción CALL en el conjunto de instrucciones del 8080/8085).

El 8259A proporciona una funcionalidad adicional en comparación con el 8259 (en particular, el modo con búfer y el modo activado por nivel) y es compatible con él.

La programación de un 8259 en conjunto con DOS y Microsoft Windows ha introducido una serie de problemas confusos por razones de compatibilidad con versiones anteriores, que se remontan al PC original presentado en 1981.

El primer problema es más o menos la raíz del segundo. Se espera que los controladores de dispositivos DOS envíen una EOI no específica a los 8259 cuando terminan de realizar el mantenimiento de su dispositivo. Esto evita el uso de cualquiera de los otros modos EOI del 8259 en DOS y excluye la diferenciación entre las interrupciones del dispositivo redirigidas desde el 8259 maestro al 8259 esclavo.

El segundo problema se refiere al uso de IRQ2 e IRQ9 a partir de la introducción de un esclavo 8259 en el PC/AT. La salida INT del esclavo 8259 está conectada al IR2 del maestro. La línea IRQ2 del bus ISA, conectada originalmente a este IR2, fue redirigida al IR1 del esclavo. De esta forma, la antigua línea IRQ2 ahora genera IRQ9 en la CPU. Para permitir la compatibilidad con versiones anteriores de los controladores de dispositivos DOS que aún están configurados para IRQ2, el BIOS instala un controlador para IRQ9 que redirige las interrupciones al controlador IRQ2 original.

En la PC, el BIOS (y por lo tanto también el DOS) tradicionalmente asigna las solicitudes de interrupción 8259 maestras (IRQ0-IRQ7) al desplazamiento del vector de interrupción 8 (INT08-INT0F) y las solicitudes de interrupción 8259 esclavas (en PC/AT y posteriores) (IRQ8-IRQ15) al desplazamiento del vector de interrupción 112 (INT70-INT77). Esto se hizo a pesar de que el procesador reservó los primeros 32 vectores de interrupción (INT00-INT1F) para excepciones internas (esto se ignoró para el diseño de la PC por alguna razón). Debido a los vectores reservados para excepciones, la mayoría de los demás sistemas operativos asignan (al menos la IRQ 8259 maestra) (si se usa en una plataforma) a otro desplazamiento base del vector de interrupción.

Dado que la mayoría de los demás sistemas operativos permiten cambios en las expectativas de los controladores de dispositivos, se pueden utilizar otros modos de funcionamiento del 8259, como Auto-EOI. Esto es especialmente importante para el hardware x86 moderno en el que se puede dedicar una cantidad significativa de tiempo a la demora del espacio de direcciones de E/S al comunicarse con los 8259. Esto también permite una serie de otras optimizaciones en la sincronización, como secciones críticas, en un sistema x86 multiprocesador con 8259.

Dado que el bus ISA no admite interrupciones activadas por nivel , el modo activado por nivel no se puede utilizar para interrupciones conectadas a dispositivos ISA. Esto significa que en PC/XT, PC/AT y sistemas compatibles, el 8259 debe programarse para el modo activado por flanco . En los sistemas MCA, los dispositivos utilizan interrupciones activadas por nivel y el controlador de interrupciones está cableado para funcionar siempre en modo activado por nivel. En los sistemas más nuevos EISA, PCI y posteriores, los registros de control de nivel/flanco (ELCR) controlan el modo por línea IRQ, lo que hace que el modo del 8259 sea irrelevante para dichos sistemas con buses ISA. El BIOS programa el ELCR al iniciar el sistema para que funcione correctamente.

Los ELCR se encuentran en 0x4d0 y 0x4d1 en el espacio de direcciones de E/S x86. Tienen 8 bits de ancho y cada bit corresponde a una IRQ de los 8259. Cuando se establece un bit, la IRQ está en modo de activación por nivel; de lo contrario, está en modo de activación por flanco.

El 8259 genera interrupciones espurias en respuesta a una serie de condiciones.

El primero es una línea IRQ que se deshabilita antes de que se reconozca. Esto puede ocurrir debido al ruido en las líneas IRQ. En el modo de activación por flanco, el ruido debe mantener la línea en estado bajo durante 100 ns. Cuando el ruido disminuye, una resistencia pull-up devuelve la línea IRQ a alto, lo que genera una interrupción falsa. En el modo de activación por nivel, el ruido puede provocar un nivel de señal alto en la línea INTR del sistema. Si el sistema envía una solicitud de reconocimiento, el 8259 no tiene nada que resolver y, por lo tanto, envía un IRQ7 en respuesta. Este primer caso generará IRQ7 falsos.

Un caso similar puede ocurrir cuando la desenmascaración del 8259 y la anulación de la afirmación de la entrada IRQ no están sincronizadas correctamente. En muchos sistemas, la entrada IRQ se anula mediante una escritura de E/S y el procesador no espera hasta que la escritura llegue al dispositivo de E/S. Si el procesador continúa y desenmascara la IRQ del 8259 antes de que se anule la afirmación de la entrada IRQ, el 8259 afirmará INTR nuevamente. Para cuando el procesador reconozca esta INTR y emita un acuse de recibo para leer la IRQ del 8259, la entrada IRQ puede anularse y el 8259 devuelva una IRQ7 falsa.

El segundo caso es que el IRQ2 del maestro 8259 está activo en alto cuando las líneas IRQ del esclavo 8259 están inactivas en el flanco descendente de un reconocimiento de interrupción. Este segundo caso generará IRQ15 espurios, pero es poco frecuente.

El sistema ISA PC/XT tenía un controlador 8259, mientras que los sistemas PC/AT y posteriores tenían dos controladores 8259, maestro y esclavo. De IRQ0 a IRQ7 son las líneas de interrupción del 8259 maestro, mientras que de IRQ8 a IRQ15 son las líneas de interrupción del 8259 esclavo. Las etiquetas de los pines de un 8259 son de IR0 a IR7. De IRQ0 a IRQ15 son los nombres de las líneas del bus ISA a las que están conectados los 8259.