Los acuerdos de fabricación de semiconductores de chips multiproyecto ( MPC ) y obleas multiproyecto ( MPW ) permiten a los clientes compartir herramientas (como máscaras ) y costos de fabricación de obleas microelectrónicas entre varios diseños o proyectos.

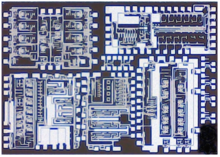

Con la disposición MPC, un chip es una combinación de varios diseños y este chip combinado se repite a lo largo de toda la oblea durante la fabricación. La disposición MPC produce, por lo general, una cantidad aproximadamente igual de diseños de chips por oblea.

_designs_for_ensuring_good_quality_of_the_processing.jpg/440px-A_wafer_consisting_of_MPC_designs_all_over_the_wafer_and_five_process_control_monitor_(PCM)_designs_for_ensuring_good_quality_of_the_processing.jpg)

Con la disposición MPW, se agregan diferentes diseños de chips en una oblea, con quizás un número diferente de diseños/proyectos por oblea. Esto es posible gracias a los novedosos sistemas de fabricación de máscaras y exposición en fotolitografía durante la fabricación de circuitos integrados. MPW se basa en los procedimientos MPC más antiguos y permite un soporte más eficaz para diferentes fases y necesidades de volúmenes de fabricación de diferentes diseños/proyectos. La disposición MPW respalda la educación, la investigación de nuevas arquitecturas y estructuras de circuitos, la creación de prototipos e incluso la producción en pequeños volúmenes. [1] [2]

En todo el mundo, existen varios servicios MPW disponibles en empresas, fundiciones de semiconductores e instituciones respaldadas por el gobierno. Originalmente, tanto los acuerdos MPC como MPW se introdujeron para la educación e investigación de circuitos integrados (CI); algunos servicios/pasarelas MPC/MPW están destinados únicamente a un uso no comercial. En la actualidad, los servicios MPC/MPW se utilizan de manera efectiva para la integración de sistemas en un chip . La selección de la plataforma de servicios adecuada en la fase de creación de prototipos garantiza una ampliación gradual de la producción a través de los servicios MPW teniendo en cuenta las reglas del servicio seleccionado.

Los arreglos MPC/MPW también se han aplicado a sistemas microelectromecánicos (MEMS), [3] fotónica integrada [4] como fabricación de fotónica de silicio , electrónica flexible, microfluídica e incluso chiplets . [5] [6]

Una mejora de la MPW es la disposición de máscaras multicapa (MLM), en la que se cambia un número limitado de máscaras (por ejemplo, 4) durante la fabricación en la fase de exposición. El resto de las máscaras son las mismas de chip a chip en toda la oblea. [7] El enfoque MLM es adecuado para varios casos específicos:

Por lo general, el enfoque MLM se utiliza para un lote de obleas (que consta de varias obleas según la línea de fabricación) y para un cliente. Al utilizar MLM, es posible obtener dispositivos más grandes (incluso del tamaño de una oblea) o una mayor cantidad de matrices y obleas en unos pocos lotes, por lo general. MLM es una continuación fluida de los volúmenes de producción de MPW en adelante y, por lo tanto, también puede respaldar la producción de volúmenes pequeños o medianos. No todas las fundiciones admiten acuerdos MLM.

Debido a la complejidad de las tecnologías disponibles y la necesidad de ejecutar MPC/MPW sin problemas, el cumplimiento de las reglas, la sincronización de los diseños y el uso de las herramientas de diseño sugeridas son fundamentales para aprovechar los beneficios de los servicios de MPC/MPW. Sin embargo, cada proveedor de servicios tiene sus propios aspectos prácticos, incluidos los datos de diseño, los tamaños de matriz, las reglas de diseño, los modelos de dispositivos, las herramientas de diseño utilizadas, los bloques de IP listos disponibles y la sincronización, etc.

Los tiempos de entrega y el costo de los servicios de MPC y MPW dependen de la tecnología de fabricación y los diseños/prototipos suelen estar disponibles como matrices o como dispositivos empaquetados. Las entregas normalmente no se prueban, pero en la mayoría de los casos la calidad del proceso de fabricación está garantizada por los resultados de las mediciones de los monitores de control de procesos (PCM) o similares.

El enfoque MPC fue una de las primeras plataformas de servicios de hardware en la industria de semiconductores, y el modelo MPW más flexible sigue siendo parte de un modelo de fabricación y fundición de microelectrónica bien establecido que no se limita a la fabricación de circuitos integrados de silicio, sino que se extiende a otras áreas de producción de semiconductores para la creación de prototipos, el desarrollo y la investigación de manera rentable.

Muchos acuerdos MPC/MPW fueron inicialmente actividades a nivel nacional, pero luego se expandieron a actividades cooperativas internacionales y globales basadas en tecnologías de fundición emergentes:

CMC Microsystems es una organización sin fines de lucro de Canadá que acelera la investigación y la innovación en tecnologías avanzadas. Fundada en 1984, CMC reduce las barreras para el diseño, la fabricación y la prueba de prototipos en microelectrónica, fotónica, cuántica, MEMS y empaquetado. Las plataformas tecnológicas de CMC, como ESP (plataforma de sensores electrónicos), impulsan proyectos de I+D, lo que permite a los ingenieros y científicos lograr resultados antes y a un menor costo. Anualmente, más de 700 equipos de investigación de empresas y 100 instituciones académicas de todo el mundo acceden a los servicios de CMC y convierten más de 400 diseños en prototipos a través de su red global de fabricantes. Este apoyo permite que 400 colaboraciones industriales y 1000 profesionales de alto nivel capacitados se unan a la industria cada año, y estas relaciones ayudan a traducir la investigación académica en resultados: publicaciones, patentes y comercialización.

Muse Semiconductor fue fundada en 2018 [8] por ex empleados de eSilicon . [9] [10] El nombre de la empresa "Muse" es un acrónimo informal de MPW University Service. [8] Muse se centra en satisfacer las necesidades de MPW de los investigadores en microelectrónica. [11] [12] Muse es compatible con todas las tecnologías de TSMC y ofrece un servicio de MPW con un área mínima de 1 mm^2 para algunas tecnologías. [13] [14] Muse es miembro del Programa FinFET de la Universidad de TSMC. [15] [16]

El primer servicio MPC conocido fue MOSIS (Metal Oxide Silicon Implementation Service), establecido por DARPA como una infraestructura técnica y humana para VLSI . MOSIS comenzó en 1981 después de que Lynn Conway organizara el primer Curso de Diseño de Sistemas VLSI en el MIT en 1978 y el curso produjo una "demostración de diseño de chips multiuniversitaria y multiproyecto" [17] entregando dispositivos a los participantes del curso en 1979. [18] [19] Los diseños para el MPC se recopilaron utilizando ARPANET . La formación técnica, además de la educación, era desarrollar e investigar de forma rentable nuevas arquitecturas informáticas sin limitaciones de componentes estándar. [20] MOSIS presta servicios principalmente a usuarios comerciales con arreglo MPW. MOSIS ha finalizado su Programa de Soporte Universitario. [21] Con MOSIS, los diseños se envían para fabricación utilizando reglas de diseño de diseño VLSI abiertas (es decir, no propietarias) o reglas propietarias del proveedor. Los diseños se agrupan en lotes comunes y se ejecutan a través del proceso de fabricación en fundiciones. Los chips terminados (empaquetados o en matriz) se devuelven a los clientes.

El primer servicio MPC de circuitos integrados de silicio internacional NORCHIP se estableció en 1981 entre cuatro países nórdicos ( Dinamarca , Finlandia , Noruega y Suecia ) y entregó los primeros chips en 1982. [22] Fue financiado por el Fondo Industrial Nórdico y organizaciones de financiación de I+D de cada país participante. Los objetivos eran la formación y la mejora de la cooperación entre la investigación y la industria, específicamente en áreas de procesamiento de señales analógicas y digitales e integración de la gestión de la energía. [23] Paralelamente a NORCHIP organizado por los mismos países nórdicos, se llevó a cabo el programa nórdico GaAs NOGAP 1986-1989, que produjo técnicas de modelado para dispositivos de circuitos integrados GaAs y demostradores de MMIC digitales y RF/analógicos de alta velocidad . De 1989 a 1995, universidades nórdicas, institutos de investigación y pequeñas empresas han participado en el EUROCHIP europeo y, a partir de 1995, en el EUROPRACTICE. [24] [25]

CMP, una empresa francesa que opera desde 1981, inició sus operaciones MPC con la oferta NMOS, pero expandió su oferta a CMOS y otras tecnologías. [26] [27] CMP también fue la primera operación MPC/MPW pancontinental oficial vinculada a MOSIS, entre otros acuerdos MPW a nivel mundial. Los servicios de CMP han incluido una variedad de tecnologías, incluidos módulos multichip (MCM) adecuados para el empaquetado de chiplets. [28]

También se han llevado a cabo proyectos similares que utilizan tecnología de circuitos integrados de silicio en Australia a partir de 1981, en Alemania el proyecto EIS (que comenzó en 1983) [29] y en Rumania, Polonia, Eslovaquia, Hungría, Chequia, Bulgaria, Estonia, Ucrania, Rusia, Letonia, Lituania y Eslovenia (1994-1997). La actividad MPC de BERCHIP, que comenzó en 1994, se organizó en América Latina. Desde 1994 se han puesto en marcha numerosos servicios MPW en todo el mundo.

Efabless permite una plataforma para circuitos integrados/sistemas en chip (SoC) diseñados utilizando únicamente herramientas de diseño de código abierto y modelos comunitarios. Comenzó a operar en el año 2020 como una empresa emergente con acceso limitado a tecnologías de fabricación de SkyWater Technology y que ofrece algunas ejecuciones anuales sincronizadas con el año académico universitario de EE. UU. [30] Con una financiación y operaciones estabilizadas, la plataforma Efabless está dirigida a nivel mundial, además de a universidades, también a institutos de investigación, pequeñas empresas posiblemente en fase de puesta en marcha y, específicamente, como un primer paso para convertir y probar la transición de FPGA a un circuito integrado.