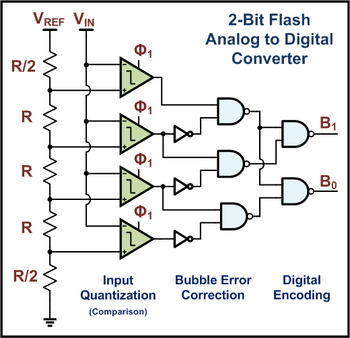

Un ADC flash (también conocido como ADC de conversión directa ) es un tipo de convertidor analógico a digital que utiliza una escalera de voltaje lineal con un comparador en cada "peldaño" de la escalera para comparar el voltaje de entrada con voltajes de referencia sucesivos. A menudo, estas escaleras de referencia se construyen con muchas resistencias ; sin embargo, las implementaciones modernas muestran que la división de voltaje capacitiva también es posible. La salida de estos comparadores generalmente se alimenta a un codificador digital, que convierte las entradas en un valor binario (las salidas recopiladas de los comparadores pueden considerarse como un valor unario ).

Los convertidores flash son de alta velocidad en comparación con muchos otros ADC, que generalmente se concentran en la respuesta correcta a lo largo de una serie de etapas. Comparado con estos, un conversor flash también es bastante sencillo y, aparte de los comparadores analógicos, sólo requiere lógica para la conversión final a binario .

Para obtener una mayor precisión, a menudo se inserta un circuito de seguimiento y retención delante de una entrada ADC. Esto es necesario para muchos tipos de ADC (como el ADC de aproximación sucesiva ), pero para los ADC flash, no existe una necesidad real porque los comparadores son los dispositivos de muestreo.

Un convertidor flash requiere muchos comparadores en comparación con otros ADC, especialmente a medida que aumenta la precisión. Por ejemplo, un convertidor flash requiere comparadores para una conversión de n bits. El tamaño, el consumo de energía y el costo de todos esos comparadores hacen que los convertidores flash generalmente no sean prácticos para precisiones mucho mayores que 8 bits (255 comparadores). En lugar de estos comparadores, la mayoría de los demás ADC sustituyen circuitos lógicos y/o analógicos más complejos que se pueden escalar más fácilmente para aumentar la precisión .

Los ADC flash se han implementado en muchas tecnologías, que van desde tecnologías bipolares basadas en silicio (BJT) y FET de óxido metálico complementario ( CMOS ) hasta tecnologías III-V raramente utilizadas . Este tipo de ADC se utiliza a menudo como primera verificación de circuito analógico de tamaño mediano.

Las primeras implementaciones consistieron en una escalera de referencia de resistencias bien adaptadas conectadas a un voltaje de referencia. Cada derivación en la escalera de resistencia se utiliza para un comparador, posiblemente precedido por una etapa de amplificación , y por lo tanto genera un 0 o 1 lógico dependiendo de si el voltaje medido está por encima o por debajo del voltaje de referencia del divisor de voltaje . La razón para agregar un amplificador es doble: amplifica la diferencia de voltaje. Por lo tanto, suprime el desplazamiento del comparador y también se suprime fuertemente el ruido de retroceso del comparador hacia la escalera de referencia. Normalmente se producen diseños desde 4 bits hasta 6 bits y, a veces, 7 bits.

Se han demostrado diseños con escaleras de referencia capacitivas de ahorro de energía. Además de cronometrar los comparadores, estos sistemas también muestrean el valor de referencia en la etapa de entrada. Como el muestreo se realiza a una velocidad muy alta, la fuga de los condensadores es insignificante.

Recientemente, se ha introducido la calibración de compensación en los diseños de ADC flash. En lugar de circuitos analógicos de alta precisión (que aumentan el tamaño de los componentes para suprimir la variación), se miden y ajustan comparadores con errores de compensación relativamente grandes. Luego, se aplica una señal de prueba y el desplazamiento de cada comparador se calibra por debajo del valor LSB del ADC.

Otra mejora de muchos ADC flash es la inclusión de corrección de errores digitales. Cuando el ADC se utiliza en entornos hostiles o se construye a partir de procesos de circuitos integrados muy pequeños, existe un mayor riesgo de que un único comparador cambie de estado aleatoriamente, lo que dará como resultado un código incorrecto. La corrección de errores de burbuja es un mecanismo de corrección digital que evita que un comparador que, por ejemplo, se ha disparado alto, informe una lógica alta si está rodeado de comparadores que informan una lógica baja.

El número de comparadores se puede reducir un poco agregando un circuito plegable en el frente, creando el llamado ADC plegable . En lugar de usar los comparadores en un ADC flash solo una vez, el ADC plegable reutiliza los comparadores varias veces durante una señal de entrada de rampa. Si se utiliza un circuito plegable m veces en un ADC de n bits, el número real de comparadores se puede reducir de a (siempre se necesita uno para detectar el cruce de rango). Los circuitos plegables típicos son el multiplicador de Gilbert y los circuitos OR cableados analógicos .

La muy alta frecuencia de muestreo de este tipo de ADC permite aplicaciones de alta frecuencia (normalmente en el rango de unos pocos GHz) como detección de radar , receptores de radio de banda ancha , equipos de prueba electrónicos y enlaces de comunicación óptica . Además, el ADC flash suele estar integrado en un circuito integrado grande que contiene muchas funciones de decodificación digital.

Además, puede haber un pequeño circuito ADC flash dentro de un bucle de modulación delta-sigma .

Los ADC flash también se utilizan en la memoria flash NAND , donde se almacenan hasta 3 bits por celda como nivel de 8 voltajes en puertas flotantes.