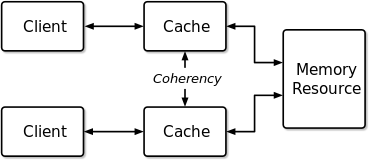

En la arquitectura informática , la coherencia de la caché es la uniformidad de los datos de recursos compartidos que terminan almacenados en múltiples cachés locales . Cuando los clientes de un sistema mantienen cachés de un recurso de memoria común, pueden surgir problemas con datos incoherentes, como es particularmente el caso de las CPU en un sistema multiprocesamiento .

En la ilustración de la derecha, considere que ambos clientes tienen una copia en caché de un bloque de memoria particular de una lectura anterior. Supongamos que el cliente en la parte inferior actualiza/cambia ese bloque de memoria, el cliente en la parte superior podría quedarse con un caché de memoria no válido sin ninguna notificación del cambio. La coherencia de la caché tiene como objetivo gestionar dichos conflictos manteniendo una vista coherente de los valores de datos en múltiples cachés.

En un sistema multiprocesador de memoria compartida con una memoria caché separada para cada procesador, es posible tener muchas copias de los datos compartidos: una copia en la memoria principal y otra en la caché local de cada procesador que la solicitó. Cuando se cambia una de las copias de datos, las otras copias deben reflejar ese cambio. La coherencia de la caché es la disciplina que garantiza que los cambios en los valores de los operandos (datos) compartidos se propaguen por todo el sistema de manera oportuna. [1]

Los siguientes son los requisitos para la coherencia de la caché: [2]

Teóricamente, la coherencia se puede realizar en la granularidad de carga/almacenamiento . Sin embargo, en la práctica generalmente se realiza en la granularidad de los bloques de caché. [3]

La coherencia define el comportamiento de lecturas y escrituras en una única ubicación de dirección. [2]

Un tipo de datos que ocurren simultáneamente en diferentes memorias caché se llama coherencia de caché o, en algunos sistemas, memoria global.

En un sistema multiprocesador, considere que más de un procesador ha almacenado en caché una copia de la ubicación de memoria X. Las siguientes condiciones son necesarias para lograr la coherencia de la caché: [4]

Las condiciones anteriores satisfacen los criterios de propagación de escritura necesarios para la coherencia de la caché. Sin embargo, no son suficientes ya que no satisfacen la condición de Serialización de transacciones. Para ilustrar esto mejor, considere el siguiente ejemplo:

Un sistema multiprocesador consta de cuatro procesadores: P1, P2, P3 y P4, todos los cuales contienen copias en caché de una variable compartida S cuyo valor inicial es 0. El procesador P1 cambia el valor de S (en su copia en caché) a 10, después de lo cual El procesador P2 cambia el valor de S en su propia copia almacenada en caché a 20. Si garantizamos solo la propagación de escritura, entonces P3 y P4 ciertamente verán los cambios realizados en S por P1 y P2. Sin embargo, P3 puede ver el cambio realizado por P1 después de ver el cambio realizado por P2 y, por lo tanto, devolver 10 en una lectura a S. P4, por otro lado, puede ver los cambios realizados por P1 y P2 en el orden en que se realizaron y, por lo tanto, devolver 20 en una lectura a S. Los procesadores P3 y P4 ahora tienen una vista incoherente de la memoria.

Por lo tanto, para satisfacer la serialización de transacciones y, por lo tanto, lograr la coherencia de la caché, se debe cumplir la siguiente condición junto con las dos anteriores mencionadas en esta sección:

La definición alternativa de un sistema coherente es a través de la definición del modelo de memoria de consistencia secuencial : "el sistema coherente en caché debe parecer ejecutar todas las cargas y almacenes de todos los subprocesos en una única ubicación de memoria en un orden total que respete el orden del programa de cada subproceso". . [3] Por lo tanto, la única diferencia entre el sistema coherente en caché y el sistema coherente secuencialmente está en el número de ubicaciones de direcciones de las que habla la definición (ubicación de memoria única para un sistema coherente en caché y todas las ubicaciones de memoria para un sistema consistente secuencialmente).

Otra definición es: "un multiprocesador es consistente con la caché si todas las escrituras en la misma ubicación de memoria se realizan en algún orden secuencial". [6]

En raras ocasiones, pero especialmente en algoritmos, la coherencia puede referirse a la localidad de referencia . Pueden existir múltiples copias de los mismos datos en diferentes cachés simultáneamente y si a los procesadores se les permite actualizar sus propias copias libremente, puede resultar en una visión inconsistente de la memoria.

Los dos mecanismos más comunes para garantizar la coherencia son el espionaje y el basado en directorios , y cada uno tiene sus propias ventajas e inconvenientes. [7] Los protocolos basados en espionaje tienden a ser más rápidos si hay suficiente ancho de banda disponible, ya que todas las transacciones son una solicitud/respuesta vista por todos los procesadores. El inconveniente es que el espionaje no es escalable. Cada solicitud debe transmitirse a todos los nodos de un sistema, lo que significa que a medida que el sistema crece, el tamaño del bus (lógico o físico) y el ancho de banda que proporciona deben crecer. Los directorios, por otro lado, tienden a tener latencias más largas (con una solicitud/reenvío/respuesta de 3 saltos) pero utilizan mucho menos ancho de banda ya que los mensajes son punto a punto y no se transmiten. Por este motivo, muchos de los sistemas más grandes (>64 procesadores) utilizan este tipo de coherencia de caché.

Los sistemas de memoria compartida distribuida imitan estos mecanismos en un intento de mantener la coherencia entre bloques de memoria en sistemas débilmente acoplados. [10]

Los protocolos de coherencia aplican coherencia de caché en sistemas multiprocesador. La intención es que dos clientes nunca vean valores diferentes para los mismos datos compartidos.

El protocolo debe implementar los requisitos básicos de coherencia. Puede personalizarse para el sistema o la aplicación de destino.

Los protocolos también se pueden clasificar como espías o basados en directorios. Por lo general, los primeros sistemas utilizaban protocolos basados en directorios en los que un directorio mantendría un seguimiento de los datos que se compartían y de quienes los compartían. En los protocolos snoopy, las solicitudes de transacción (para leer, escribir o actualizar) se envían a todos los procesadores. Todos los procesadores espían la solicitud y responden adecuadamente.

La propagación de escritura en protocolos snoopy se puede implementar mediante cualquiera de los siguientes métodos:

Si el diseño del protocolo establece que cada vez que se cambia una copia de los datos compartidos, todas las demás copias deben "actualizarse" para reflejar el cambio, entonces es un protocolo de actualización de escritura. Si el diseño establece que una escritura en una copia en caché por parte de cualquier procesador requiere que otros procesadores descarten o invaliden sus copias en caché, entonces es un protocolo de invalidación de escritura.

Sin embargo, la escalabilidad es una deficiencia de los protocolos de transmisión.

Se han ideado varios modelos y protocolos para mantener la coherencia, como MSI , MESI (también conocido como Illinois), MOSI , MOESI , MERSI , MESIF , write-once , Synapse, Berkeley, Firefly y Dragon . [1] En 2011, ARM Ltd propuso AMBA 4 ACE [11] para manejar la coherencia en SoC . La especificación AMBA CHI (Coherent Hub Interface) [12] de ARM Ltd , que pertenece al grupo de especificaciones AMBA5, define las interfaces para la conexión de procesadores totalmente coherentes.