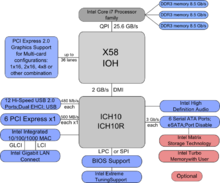

El Intel X58 ( nombre en código Tylersburg ) es un chip Intel diseñado para conectar procesadores Intel con interfaz Intel QuickPath Interconnect (QPI) a dispositivos periféricos. Los procesadores compatibles implementan la microarquitectura Nehalem y, por lo tanto, tienen un controlador de memoria integrado (IMC), por lo que el X58 no tiene una interfaz de memoria. Los procesadores inicialmente compatibles eran el Core i7 , [1] pero el chip también admitía los procesadores Xeon basados en Nehalem y Westmere .

La arquitectura QuickPath difiere considerablemente de las arquitecturas anteriores de Intel y está mucho más cerca de la arquitectura HyperTransport de AMD . Excepto por la falta de una interfaz de memoria, el X58 es similar al puente norte tradicional : se comunica con los procesadores a través de QuickPath Interconnect de gran ancho de banda , se comunica con el puente sur a través de Direct Media Interface (DMI) y se comunica con periféricos de gran ancho de banda a través de PCI Express (PCIe).

El X58 no es un concentrador de controlador de memoria (MCH), porque no tiene interfaz de memoria, por lo que Intel lo llama concentrador de E/S . Esto no debe confundirse con el término similar concentrador controlador de E/S ( ICH ) que se ha utilizado tradicionalmente para referirse a los chips del puente sur . La documentación de Intel ahora se refiere al puente sur como el concentrador de controladores de E/S heredado .

El X58 tiene 36 carriles PCIe que están dispuestos en dos enlaces ×16, un enlace DMI y un enlace basado en "repuesto". Cuando se utiliza con el concentrador del controlador de E/S ICH10 con conexión DMI ×4, el "repuesto" admite una conexión PCIe ×4 separada. Los futuros chips DMI del puente sur pueden admitir un DMI más amplio.

Cada interconexión X58 QuickPath utiliza 21 pares diferenciales unidireccionales en cada dirección, para un total de 84 pines por QPI. Con el ancho de banda más alto, cada QPI puede transferir hasta 12,8 GB/s utilizables en cada dirección simultáneamente utilizando el protocolo QPI. El protocolo transfiere información en saltos de 80 bits que contienen 8 bits de corrección de errores, 8 bits de información de enrutamiento QPI y 64 bits de datos.

Los puertos PCIe X58 admiten ancho de banda PCIe 2.0 completo (por ejemplo, hasta 8 GB/s, incluidos los gastos generales por enlace ×16) y cada enlace ×16 se puede dividir en un total de 16 carriles en cualquier combinación de ×8, ×4, ×2 o ×1 puertos. También admiten todas las funciones de cableado de línea reservada, lo que significa que en las combinaciones de ranuras (×16 + ×1/×8), que se utilizan a menudo en las placas base, no solo se pueden instalar tarjetas ×1 u ×8 en las × Ranura 1/×8, pero las tarjetas ×4 también deberían funcionar (si el BIOS de la placa base no lo permite).

A diferencia del bus frontal (FSB), QPI es una interfaz punto a punto y admite no solo la interfaz procesador-chipset, sino también la conexión de procesador a procesador y la conexión de chip a chip. El X58 tiene dos QPI y puede conectarse directamente a dos procesadores en una placa base de múltiples sockets o formar una conexión en forma de anillo (del procesador 1 al X58 al procesador 2 y de regreso al procesador 1). Cuando se usa con Intel Core i7 , el segundo QPI generalmente no se usa (aunque, en principio, el segundo X58 podría estar conectado en cadena en la placa).

Cuando se usa con el procesador DP "Gainestown", que tendrá dos QPI, el X58 y los dos procesadores pueden conectarse en un triángulo o anillo. Para procesadores MP como "Beckton" con más de dos QPI, el X58 está conectado a dos procesadores, que a su vez están conectados en una "malla" de QPI a otros procesadores o conectados "en pares" a dos procesadores diferentes. La E/S para procesadores "remotos" se transmite a través del QPI entre procesadores.

Los fabricantes de placas X58 pueden construir placas con chipset Intel compatibles con SLI enviando sus diseños a nVidia para su validación. Sin embargo, los usuarios que deseen ejecutar más de dos tarjetas de video Nvidia en PCIe ×16 deberán comprar placas base equipadas con uno o más conjuntos de chips nVidia nForce . Aún es posible ejecutar más de dos tarjetas de video en una configuración SLI con menos anchos de carril PCIe . [2] El chipset X58 admite hasta 36 carriles PCI-Express 2.0, por lo que es posible tener dos ranuras PCIe ×16 y una ranura PCIe ×4 en la misma placa base. [1]