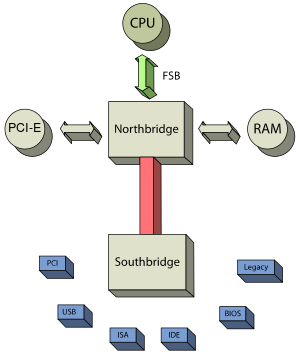

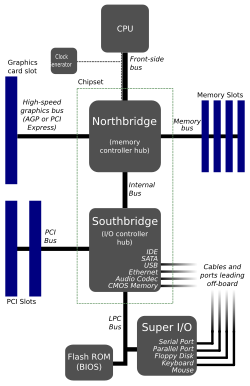

En las placas base de ordenadores personales más antiguas , el puente sur es uno de los dos chips del conjunto de chips lógicos básicos, que se encarga de muchas de las funciones de entrada y salida de un ordenador . El otro componente del conjunto de chips es el puente norte , que generalmente se encarga de las tareas de control integradas.

Un chipset southbridge maneja funciones como USB, audio, el firmware del sistema, los buses PCI/PCIe de menor velocidad, el controlador de interrupciones IOAPIC, el almacenamiento SATA, el almacenamiento PATA histórico, el almacenamiento NVMe y buses de baja velocidad como ISA , LPC , SPI y/o eSPI . [1] [2] Son posibles diferentes combinaciones de chips southbridge y northbridge, [3] pero estos dos tipos de chips están diseñados para funcionar juntos. [ cita requerida ] No existe un estándar a nivel de la industria para la interoperabilidad entre diferentes diseños de chipset de lógica central. En la década de 1990 y principios de la de 2000, la interfaz entre un northbridge y un southbridge era el bus PCI. A partir de 2023, las principales interfaces de puente utilizadas son Direct Media Interface ( Intel ) y PCI Express ( AMD ).

El puente sur generalmente implementa las capacidades más lentas de la placa base en una arquitectura informática con chipset puente norte-puente sur. En sistemas con chipsets Intel , el puente sur se ha denominado concentrador de controlador de E/S (ICH) y luego se ha reemplazado por chipsets de concentrador de controlador de plataforma . En arquitecturas Intel/AMD más antiguas, el puente sur generalmente está vinculado al puente norte, que a su vez está conectado a la CPU. Alrededor de 2004 y en adelante, las arquitecturas Intel comenzaron a vincular el puente sur directamente a la CPU (por ejemplo, a través de Direct Media Interface ). A través del uso de circuitos de canal integrados en el controlador, el puente norte (o la CPU en sí) puede vincular directamente las señales de las unidades de E/S a la CPU para el control y acceso a los datos.

A partir de 2024, la mayoría de los dispositivos informáticos personales basados en arquitecturas Intel o AMD ya no utilizan un conjunto de dos chips, sino que tienen un solo chip que actúa como "chipset", por ejemplo, el chipset Z790 de Intel, y una unidad central de procesamiento.

Debido al impulso hacia los procesadores de sistema en chip (SoC), los dispositivos modernos tienen cada vez más el puente norte integrado en la propia matriz de la CPU ; [ se necesita más explicación ] algunos ejemplos son el Sandy Bridge de Intel [4] y los procesadores Fusion de AMD [5] , ambos lanzados en 2011.

Con el chipset Intel Serie 5 en 2008, el puente sur se volvió redundante y fue reemplazado por la arquitectura Platform Controller Hub (PCH). AMD hizo lo mismo con el lanzamiento de sus primeras APU en 2011, nombrando al PCH como Fusion Controller Hub (FCH), que solo se usó en las APU de AMD hasta 2017, cuando comenzó a usarse en la arquitectura Zen de AMD y se eliminó el nombre FCH.

En las plataformas Intel, todas las funciones del puente sur y las demás funciones de E/S son administradas por el PCH, que está conectado directamente a la CPU a través de la Interfaz de Medios Directos (DMI). [6] Los procesadores de bajo consumo de Intel (Haswell-U y posteriores) y los procesadores de consumo ultrabajo (Haswell-Y y posteriores) también integran un PCH en el paquete. Basados en su diseño Chiplet , los procesadores AMD Ryzen también integraron algunas funciones del puente sur, como algunas interfaces USB y SATA / NVMe . [7]

El nombre se deriva de la representación de la arquitectura en forma de mapa y fue descrito por primera vez como tal con la introducción de la arquitectura de bus local PCI en 1991. En Intel, los autores de la especificación PCI vieron al bus local PCI como el centro mismo de la arquitectura de la plataforma de PC (es decir, en el Ecuador ).

El puente norte se extiende hacia el norte de la red troncal del bus PCI para dar soporte a la CPU, la memoria/ caché y otras funciones críticas para el rendimiento. Asimismo, el puente sur se extiende hacia el sur de la red troncal del bus PCI y sirve de puente hacia funciones de E/S menos críticas para el rendimiento, como la interfaz de disco, el audio, etc.

La CPU se encuentra en la parte superior del mapa, en dirección norte. La CPU está conectada al chipset a través de un puente rápido (el puente norte) ubicado al norte de otros dispositivos del sistema, como se muestra en el dibujo. El puente norte está conectado al resto del chipset a través de un puente lento (el puente sur) ubicado al sur de otros dispositivos del sistema, como se muestra en el dibujo.

Aunque la arquitectura actual de la plataforma PC ha reemplazado la red troncal del bus PCI con redes troncales de E/S más rápidas, la convención de nombres del puente se mantiene.

La funcionalidad que se encuentra en un puente sur contemporáneo incluye: [8] [2]

Opcionalmente, un puente sur también incluye soporte (chip discreto integrado o puente sur integrado) para Ethernet , Wi-Fi , RAID , Thunderbolt y administración fuera de banda .