En informática , el protocolo MSI (un protocolo básico de coherencia de caché ) funciona en sistemas multiprocesador. Al igual que con otros protocolos de coherencia de caché, las letras del nombre del protocolo identifican los posibles estados en los que puede estar una línea de caché.

En MSI, cada bloque contenido dentro de un caché puede tener uno de tres estados posibles:

Estos estados de coherencia se mantienen mediante la comunicación entre las memorias caché y el almacenamiento de respaldo. Las memorias caché tienen distintas responsabilidades cuando se leen o escriben bloques, o cuando se enteran de que otras memorias caché emiten operaciones de lectura o escritura para un bloque.

Cuando llega una solicitud de lectura a una caché para un bloque en los estados "M" o "S", la caché proporciona los datos. Si el bloque no está en la caché (en el estado "I"), debe verificar que el bloque no esté en el estado "M" en ninguna otra caché. Las diferentes arquitecturas de almacenamiento en caché manejan esto de manera diferente. Por ejemplo, las arquitecturas de bus a menudo realizan un seguimiento , donde la solicitud de lectura se transmite a todas las cachés. Otras arquitecturas incluyen directorios de caché que tienen agentes (directorios) que saben qué cachés tuvieron las últimas copias de un bloque de caché en particular. Si otra caché tiene el bloque en el estado "M", debe volver a escribir los datos en el almacenamiento de respaldo y pasar a los estados "S" o "I". Una vez que se vuelve a escribir cualquier línea "M", la caché obtiene el bloque del almacenamiento de respaldo o de otra caché con los datos en el estado "S". Luego, la caché puede proporcionar los datos al solicitante. Después de proporcionar los datos, el bloque de caché está en el estado "S".

Cuando llega una solicitud de escritura a una caché para un bloque en el estado "M", la caché modifica los datos localmente. Si el bloque está en el estado "S", la caché debe notificar a cualquier otra caché que pueda contener el bloque en el estado "S" que deben expulsar el bloque. Esta notificación puede ser a través de un rastreo de bus o un directorio, como se describió anteriormente. Luego, los datos pueden modificarse localmente. Si el bloque está en el estado "I", la caché debe notificar a cualquier otra caché que pueda contener el bloque en los estados "S" o "M" que deben expulsar el bloque. Si el bloque está en otra caché en el estado "M", esa caché debe escribir los datos en el almacenamiento de respaldo o proporcionárselos a la caché solicitante. Si en este punto la caché aún no tiene el bloque localmente, el bloque se lee desde el almacenamiento de respaldo antes de modificarse en la caché. Después de que se modifican los datos, el bloque de la caché está en el estado "M".

Para cualquier par de cachés dado, los estados permitidos de una línea de caché determinada son los siguientes:

Las solicitudes del procesador a la caché incluyen:

Además, existen solicitudes para el lado del autobús, entre las que se incluyen:

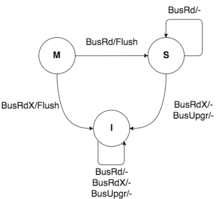

Transiciones de estado:

Este protocolo es similar al utilizado en la máquina SGI 4D. [3]

Los sistemas modernos utilizan variantes del protocolo MSI para reducir la cantidad de tráfico en la interconexión de coherencia. El protocolo MESI agrega un estado "Exclusivo" para reducir el tráfico causado por escrituras de bloques que solo existen en una caché. El protocolo MOSI agrega un estado "Propiedad" para reducir el tráfico causado por reescrituras de bloques que son leídos por otras cachés. El protocolo MOESI hace ambas cosas.