La memoria de acceso aleatorio dinámico síncrono de velocidad de datos doble ( SDRAM DDR ) es una clase de circuitos integrados de memoria de memoria de acceso aleatorio dinámico síncrono (SDRAM) de velocidad de datos doble (DDR) utilizados en computadoras . DDR SDRAM, también llamada retroactivamente DDR1 SDRAM, ha sido reemplazada por DDR2 SDRAM , DDR3 SDRAM , DDR4 SDRAM y DDR5 SDRAM . Ninguno de sus sucesores es compatible con versiones anteriores o posteriores de DDR1 SDRAM, lo que significa que los módulos de memoria DDR2, DDR3, DDR4 y DDR5 no funcionarán en placas base equipadas con DDR1 , y viceversa.

En comparación con la SDRAM de velocidad de datos única ( SDR ), la interfaz SDRAM DDR hace posibles velocidades de transferencia más altas a través de un control más estricto de la sincronización de los datos eléctricos y las señales de reloj. Las implementaciones a menudo tienen que utilizar esquemas como bucles de bloqueo de fase y autocalibración para alcanzar la precisión de sincronización requerida. [4] [5] La interfaz utiliza doble bombeo (transfiriendo datos en los flancos ascendente y descendente de la señal del reloj ) para duplicar el ancho de banda del bus de datos sin el correspondiente aumento en la frecuencia del reloj. Una ventaja de mantener baja la frecuencia del reloj es que reduce los requisitos de integridad de la señal en la placa de circuito que conecta la memoria al controlador. El nombre "velocidad de datos doble" se refiere al hecho de que una SDRAM DDR con una determinada frecuencia de reloj alcanza casi el doble de ancho de banda que una SDRAM SDR funcionando a la misma frecuencia de reloj, debido a este doble bombeo.

Con datos transferidos de 64 bits a la vez, DDR SDRAM proporciona una velocidad de transferencia (en bytes/s) de (velocidad de reloj del bus de memoria) × 2 (para velocidad dual) × 64 (número de bits transferidos) / 8 (número de bits /byte). Así, con una frecuencia de bus de 100 MHz, DDR SDRAM proporciona una velocidad de transferencia máxima de 1600 MB/s .

A finales de la década de 1980, IBM había construido DRAM utilizando una función de sincronización de doble filo y presentó sus resultados en la Convención Internacional de Circuitos de Estado Sólido en 1990. [6] [7]

Samsung demostró el primer prototipo de memoria DDR en 1997, [1] y lanzó el primer chip DDR SDRAM comercial (64 Mbit ) en junio de 1998, [8] [2] [3] seguido poco después por Hyundai Electronics (ahora SK Hynix ), el mismo año. [9] El desarrollo de DDR comenzó en 1996, antes de que JEDEC finalizara su especificación en junio de 2000 (JESD79). [10] JEDEC ha establecido estándares para las velocidades de datos de DDR SDRAM, divididos en dos partes. La primera especificación es para chips de memoria y la segunda es para módulos de memoria. La primera placa base para PC minorista que utiliza DDR SDRAM se lanzó en agosto de 2000. [11]

.jpg/440px-Generic_DDR_Memory_(Xytram).jpg)

Para aumentar la capacidad de memoria y el ancho de banda, los chips se combinan en un módulo. Por ejemplo, el bus de datos de 64 bits para DIMM requiere ocho chips de 8 bits direccionados en paralelo. Varios chips con líneas de dirección comunes se denominan rango de memoria . El término se introdujo para evitar confusión con filas y bancos internos de chips . Un módulo de memoria puede tener más de un rango. El término lados también sería confuso porque sugiere incorrectamente la ubicación física de los chips en el módulo. Todos los rangos están conectados al mismo bus de memoria (dirección + datos). La señal de selección de chip se utiliza para emitir comandos para un rango específico.

Agregar módulos al bus de memoria único crea una carga eléctrica adicional en sus controladores. Para mitigar la caída resultante en la tasa de señalización del bus y superar el cuello de botella de la memoria , los nuevos conjuntos de chips emplean la arquitectura multicanal .

Nota: JEDEC especifica todos los elementos enumerados anteriormente como JESD79F. [13] JEDEC no estandariza todas las velocidades de datos de RAM que se encuentran entre o por encima de estas especificaciones enumeradas; a menudo son simplemente optimizaciones del fabricante que utilizan tolerancias más estrictas o chips sobrevolteados. JEDEC también estandariza los tamaños de paquete en los que se fabrica DDR SDRAM.

No existe ninguna diferencia arquitectónica entre los módulos DDR SDRAM. En cambio, los módulos están diseñados para funcionar a diferentes frecuencias de reloj: por ejemplo, un módulo PC-1600 está diseñado para funcionar a 100 MHz y un PC-2100 está diseñado para funcionar a 133 MHz . La velocidad de reloj de un módulo designa la velocidad de datos a la que se garantiza que funcionará, por lo tanto, se garantiza que funcionará a velocidades más bajas ( underclocking ) y posiblemente pueda funcionar a velocidades de reloj más altas ( overclocking ) que aquellas para las que fue creado. [14]

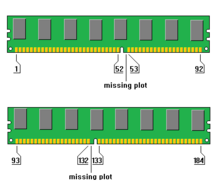

Los módulos DDR SDRAM para computadoras de escritorio, módulos de memoria dual en línea (DIMM) , tienen 184 pines (a diferencia de 168 pines en SDRAM o 240 pines en DDR2 SDRAM) y se pueden diferenciar de los SDRAM DIMM por el número de muescas ( DDR SDRAM tiene uno, SDRAM tiene dos). La SDRAM DDR para computadoras portátiles, SO-DIMM , tiene 200 pines, que es la misma cantidad de pines que los SO-DIMM DDR2. Estas dos especificaciones tienen muescas de manera muy similar y se debe tener cuidado durante la inserción si no está seguro de que coincidan correctamente. La mayoría de las DDR SDRAM funcionan a un voltaje de 2,5 V, en comparación con los 3,3 V de la SDRAM. Esto puede reducir significativamente el consumo de energía. Los chips y módulos con el estándar DDR-400/PC-3200 tienen una tensión nominal de 2,6 V.

El estándar JEDEC No. 21–C define tres posibles voltajes de funcionamiento para DDR de 184 pines, identificados por la posición de la muesca de la llave en relación con su línea central. La página 4.5.10-7 define 2,5 V (izquierda), 1,8 V (centro), TBD (derecha), mientras que la página 4.20.5–40 nomina 3,3 V para la posición de muesca derecha. La orientación del módulo para determinar la posición de la muesca de la llave es con 52 posiciones de contacto a la izquierda y 40 posiciones de contacto a la derecha.

Aumentar ligeramente el voltaje de funcionamiento puede aumentar la velocidad máxima, pero a costa de una mayor disipación de energía y calentamiento, y con el riesgo de mal funcionamiento o daños.

Las características del módulo y del chip están inherentemente vinculadas.

La capacidad total del módulo es el producto de la capacidad de un chip y la cantidad de chips. Los módulos ECC lo multiplican por 8 ⁄ 9 porque utilizan 1 bit por byte (8 bits) para la corrección de errores. Por lo tanto, un módulo de cualquier tamaño particular puede ensamblarse a partir de 32 chips pequeños (36 para memoria ECC) o de 16 (18) u 8 (9) más grandes.

El ancho del bus de memoria DDR por canal es de 64 bits (72 para memoria ECC). El ancho total de bits del módulo es el producto de los bits por chip y el número de chips. También equivale al número de rangos (filas) multiplicado por el ancho del bus de memoria DDR. En consecuencia, un módulo con una mayor cantidad de chips o que utilice chips ×8 en lugar de ×4 tendrá más rangos.

Este ejemplo compara diferentes módulos de memoria de servidor del mundo real con un tamaño común de 1 GB. Definitivamente hay que tener cuidado al comprar módulos de memoria de 1 GB, porque todas estas variaciones se pueden vender en una misma posición de precio sin indicar si son ×4 u ×8, de clasificación simple o doble.

Existe la creencia común de que el número de rangos de módulos es igual al número de lados. Como muestran los datos anteriores, esto no es cierto. También se pueden encontrar módulos de 2 lados/1 rango. Incluso se puede pensar en un módulo de memoria de 1 lado/2 rangos que tenga 16(18) chips en un solo lado ×8 cada uno, pero es poco probable que tal módulo se haya producido alguna vez.

De la boleta JCB-99-70, y modificado por muchas otras boletas de la Junta, formuladas bajo el conocimiento del Comité JC-42.3 sobre Parámetros de DRAM.

Registro de revisión de la norma No. 79:

"Este estándar integral define todos los aspectos requeridos de las SDRAM DDR de 64 Mb a 1 Gb con interfaces de datos X4/X8/X16, incluidas características, funcionalidad, parámetros de CA y CC, paquetes y asignaciones de pines. Este alcance se ampliará posteriormente para aplicarse formalmente a dispositivos x32. , y también dispositivos de mayor densidad".

PC3200 es DDR SDRAM diseñada para funcionar a 200 MHz utilizando chips DDR-400 con un ancho de banda de 3200 MB/s. Debido a que la memoria PC3200 transfiere datos tanto en el flanco ascendente como en el descendente del reloj, su frecuencia de reloj efectiva es de 400 MHz.

Los módulos PC3200 no ECC de 1 GB generalmente se fabrican con 16 chips de 512 Mbit, 8 en cada lado (512 Mbits × 16 chips) / (8 bits (por byte)) = 1024 MB. Los chips individuales que componen un módulo de memoria de 1 GB suelen estar organizados como 2 26 palabras de 8 bits, comúnmente expresadas como 64M×8. La memoria fabricada de esta manera es RAM de baja densidad y suele ser compatible con cualquier placa base que especifique memoria PC3200 DDR-400. [19] [ cita necesaria ]

DDR (DDR1) fue reemplazada por DDR2 SDRAM , que tuvo modificaciones para una frecuencia de reloj más alta y nuevamente duplicó el rendimiento, pero funciona según el mismo principio que DDR. Compitiendo con DDR2 estaba Rambus XDR DRAM . DDR2 dominó debido a factores de costo y soporte. A su vez, DDR2 fue reemplazada por DDR3 SDRAM , que ofrecía un mayor rendimiento para mayores velocidades de bus y nuevas funciones. DDR3 ha sido reemplazada por DDR4 SDRAM , que se produjo por primera vez en 2011 y cuyos estándares aún estaban en constante cambio (2012) con importantes cambios arquitectónicos.

La profundidad del búfer de captación previa de DDR es 2 (bits), mientras que DDR2 usa 4. Aunque las velocidades de reloj efectivas de DDR2 son más altas que las de DDR, el rendimiento general no fue mayor en las primeras implementaciones, principalmente debido a las altas latencias de los primeros módulos DDR2. DDR2 comenzó a ser eficaz a finales de 2004, cuando estuvieron disponibles módulos con latencias más bajas. [20]

Los fabricantes de memoria declararon que no era práctico producir en masa memoria DDR1 con tasas de transferencia efectiva superiores a 400 MHz (es decir, 400 MT/s y 200 MHz de reloj externo) debido a limitaciones de velocidad interna. DDR2 continúa donde lo dejó DDR1, utilizando velocidades de reloj internas similares a DDR1, pero está disponible a velocidades de transferencia efectivas de 400 MHz y superiores. Los avances de DDR3 ampliaron la capacidad de preservar las velocidades de reloj interno y al mismo tiempo proporcionar velocidades de transferencia efectivas más altas al duplicar nuevamente la profundidad de captación previa.

La SDRAM DDR4 es una memoria dinámica de acceso aleatorio de alta velocidad configurada internamente como 16 bancos, 4 grupos de bancos con 4 bancos para cada grupo de bancos para ×4/×8 y 8 bancos, 2 grupos de bancos con 4 bancos para cada grupo de bancos para ×16 COPITAS. La SDRAM DDR4 utiliza una arquitectura de captación previa de 8 n para lograr un funcionamiento de alta velocidad. La arquitectura de captación previa de 8 n se combina con una interfaz diseñada para transferir dos palabras de datos por ciclo de reloj en los pines de E/S. Una única operación de lectura o escritura para la SDRAM DDR4 consta de una única transferencia de datos de 4 relojes de 8 n bits de ancho en el núcleo de la DRAM interna y 8 transferencias de datos de medio ciclo de reloj de n bits de ancho correspondientes en la E/S. patas. [21]

La RDRAM era una alternativa particularmente cara a la SDRAM DDR y la mayoría de los fabricantes eliminaron el soporte de sus conjuntos de chips. Los precios de la memoria DDR1 aumentaron sustancialmente desde el segundo trimestre de 2008, mientras que los precios de la DDR2 disminuyeron. En enero de 2009, 1 GB de DDR1 era entre 2 y 3 veces más caro que 1 GB de DDR2. [ cita necesaria ]

MDDR es un acrónimo que algunas empresas utilizan para Mobile DDR SDRAM, un tipo de memoria utilizada en algunos dispositivos electrónicos portátiles, como teléfonos móviles , dispositivos portátiles y reproductores de audio digitales . A través de técnicas que incluyen un suministro de voltaje reducido y opciones de actualización avanzadas, Mobile DDR puede lograr una mayor eficiencia energética.