Pixel Visual Core ( PVC ) es una serie de procesadores de imágenes de sistema en paquete (SiP) basados en ARM diseñados por Google . [1] El PVC es una arquitectura de dominio específico ( DSA ) multinúcleo de imagen , visión e IA totalmente programable para dispositivos móviles y, en el futuro, para IoT . [2] Apareció por primera vez en Google Pixel 2 y 2 XL, que se presentaron el 19 de octubre de 2017. También apareció en Google Pixel 3 y 3 XL . A partir del Pixel 4, este chip fue reemplazado por el Pixel Neural Core .

Anteriormente, Google utilizaba la CPU , la GPU , la IPU y el DSP de Qualcomm Snapdragon para manejar el procesamiento de imágenes de sus dispositivos Google Nexus y Google Pixel . Con la creciente importancia de las técnicas de fotografía computacional , Google desarrolló el Pixel Visual Core (PVC). Google afirma que el PVC consume menos energía que el uso de la CPU y la GPU y, al mismo tiempo, es totalmente programable, a diferencia de su circuito integrado específico de la aplicación (ASIC) de unidad de procesamiento tensorial (TPU) . De hecho, los dispositivos móviles clásicos equipan un procesador de señal de imagen (ISP) que es una tubería de procesamiento de imágenes de funcionalidad fija . En contraste con esto, el PVC tiene una funcionalidad programable flexible, que no se limita solo al procesamiento de imágenes.

El PVC en los Google Pixel 2 y 2 XL tiene la etiqueta SR3HX X726C502. [3]

El PVC en los Google Pixel 3 y 3 XL tiene la etiqueta SR3HX X739F030. [4]

Gracias al PVC, el Pixel 2 y el Pixel 3 obtuvieron un DxOMark móvil de 98 [5] y 101 [6]. Este último fue el puntaje DxOMark móvil de lente única mejor clasificado, empatado con el iPhone XR. [7]

Un programa típico de procesamiento de imágenes del PVC está escrito en Halide . Actualmente, solo admite un subconjunto del lenguaje de programación Halide sin operaciones de punto flotante y con patrones de acceso a memoria limitados. [8] Halide es un lenguaje específico de dominio que permite al usuario desacoplar el algoritmo y la programación de su ejecución. De esta manera, el desarrollador puede escribir un programa optimizado para la arquitectura de hardware de destino. [2]

El PVC tiene dos tipos de arquitectura de conjunto de instrucciones (ISA) , una virtual y otra física. Primero, un programa de lenguaje de alto nivel se compila en una ISA virtual (vISA) , inspirada en la ISA RISC-V [2] , que se abstrae completamente de la generación del hardware de destino. Luego, el programa vISA se compila en la llamada ISA física (pISA) , que es una ISA VLIW . Este paso de compilación tiene en cuenta los parámetros del hardware de destino (por ejemplo, tamaño de la matriz de PE, tamaño de STP, etc.) y especifica explícitamente los movimientos de memoria. El desacoplamiento de vISA y pISA permite que el primero sea de arquitectura cruzada e independiente de la generación, mientras que pISA se puede compilar fuera de línea o mediante compilación JIT [8] .

El Pixel Visual Core está diseñado para ser una arquitectura escalable de múltiples núcleos y de bajo consumo energético, que va desde diseños de números pares entre 2 y 16 núcleos. [2] El núcleo de un PVC es la unidad de procesamiento de imágenes (IPU), una unidad programable diseñada a medida para el procesamiento de imágenes. La arquitectura Pixel Visual Core también fue diseñada para ser su propio chip, como el SR3HX, o como un bloque IP para el sistema en un chip (SOC) . [2]

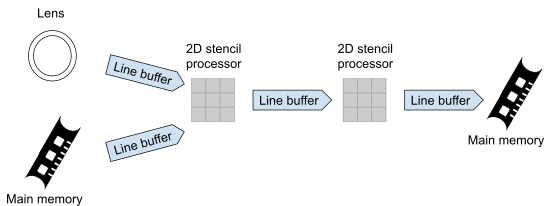

El núcleo de la IPU tiene un procesador de esténcil (STP), un grupo de búfer de línea (LBP) y un NoC . El STP proporciona principalmente una matriz SIMD 2-D de elementos de procesamiento (PE) capaces de realizar cálculos de esténcil , un pequeño vecindario de píxeles. Aunque parece similar a los cálculos de matriz sistólica y frente de onda, el STP tiene un movimiento de datos controlado por software explícito. Cada PE presenta 2 unidades lógicas aritméticas (ALU) de 16 bits, 1 unidad multiplicadora-acumuladora (MAC) de 16 bits , 10 registros de 16 bits y 10 registros de predicado de 1 bit. [2]

Teniendo en cuenta que una de las operaciones más costosas en términos de energía es el acceso a la DRAM, cada STP tiene buffers temporales para aumentar la localidad de datos , es decir, LBP. El LBP utilizado es un FIFO 2-D que admite diferentes tamaños de lectura y escritura. El LBP utiliza un modelo de comportamiento de un solo productor y múltiples consumidores. Cada LBP puede tener ocho memorias LB lógicas y una para operaciones de entrada-salida DMA . [8] Debido a la alta complejidad real del sistema de memoria, los diseñadores de PVC indican que el controlador LBP es uno de los componentes más desafiantes. [2] El NoC utilizado es una red de anillo en chip que se utiliza para comunicarse solo con núcleos vecinos para ahorrar energía y preservar el patrón computacional canalizado. [2]

El STP tiene una matriz 2-D de PEs: por ejemplo, una matriz 16x16 de PEs completos y cuatro carriles de PEs simplificados llamados "halo" . El STP tiene un procesador escalar, llamado carril escalar (SCL), que agrega instrucciones de control con una pequeña memoria de instrucciones. El último componente de un STP es una unidad de almacenamiento de carga llamada generador de hojas (SHG), donde la hoja es la unidad de acceso a la memoria PVC. [2]

El SR3HX PVC cuenta con una CPU ARMv8a ARM Cortex-A53 de 64 bits , 8 núcleos de unidad de procesamiento de imágenes (IPU), 512 MB LPDDR4 , MIPI, PCIe. Cada núcleo de la IPU tiene 512 unidades lógicas aritméticas (ALU) que constan de 256 elementos de procesamiento (PE) dispuestos como una matriz bidimensional de 16 x 16. Esos núcleos ejecutan una ISA VLIW personalizada. Hay dos ALU de 16 bits por elemento de procesamiento y pueden funcionar de tres formas distintas: independientes, unidas y fusionadas. [9] El SR3HX PVC es fabricado como un SiP por TSMC utilizando su proceso HKMG de 28HPM. [1] Fue diseñado durante 4 años en asociación con Intel . (Nombre en clave: Monette Hill) [10] Google afirma que el SR3HX PVC es entre 7 y 16 veces más eficiente energéticamente que el Snapdragon 835 . [1] Y que el SR3HX PVC puede realizar 3 billones de operaciones por segundo, HDR+ puede funcionar 5 veces más rápido y con menos de una décima parte de la energía que el Snapdragon 835. [ 11] Es compatible con Halide para el procesamiento de imágenes y TensorFlow para el aprendizaje automático. [11] El chip actual funciona a 426 MHz y la IPU única puede realizar más de 1 TeraOPS. [2] [8]