Las cachés de varios niveles se pueden diseñar de varias maneras dependiendo de si el contenido de una caché está presente en otros niveles de cachés. Si todos los bloques de la caché de nivel superior también están presentes en la caché de nivel inferior, se dice que la caché de nivel inferior incluye a la caché de nivel superior. Si la caché de nivel inferior contiene solo bloques que no están presentes en la caché de nivel superior, se dice que la caché de nivel inferior excluye a la caché de nivel superior. Si el contenido de la caché de nivel inferior no es estrictamente inclusivo ni exclusivo de la caché de nivel superior, se denomina caché no inclusiva ni exclusiva (NINE) . [1] [2]

Consideremos un ejemplo de una jerarquía de caché de dos niveles donde L2 puede ser inclusiva, exclusiva o NUEVE de L1. Consideremos el caso en el que L2 es inclusiva de L1. Supongamos que hay una solicitud de lectura del procesador para el bloque X. Si el bloque se encuentra en la caché L1, entonces los datos se leen de la caché L1 y se devuelven al procesador. Si el bloque no se encuentra en la caché L1, pero está presente en la caché L2, entonces el bloque de caché se obtiene de la caché L2 y se coloca en L1. Si esto hace que se expulse un bloque de L1, no hay participación de L2. Si el bloque no se encuentra ni en L1 ni en L2, entonces se obtiene de la memoria principal y se coloca tanto en L1 como en L2. Ahora, si hay un desalojo de L2, la caché L2 envía una invalidación de vuelta a la caché L1, de modo que no se viole la inclusión.

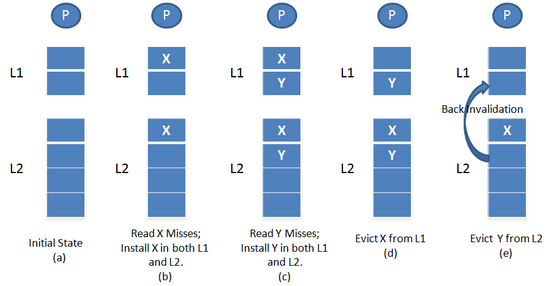

Como se ilustra en la Figura 1, inicialmente considere que tanto las cachés L1 como L2 están vacías (a). Suponga que el procesador envía una solicitud de lectura X. Será un error tanto en L1 como en L2 y, por lo tanto, el bloque se lleva a L1 y L2 desde la memoria principal como se muestra en (b). Ahora, suponga que el procesador emite una solicitud de lectura Y que es un error tanto en L1 como en L2. Por lo tanto, el bloque Y se coloca tanto en L1 como en L2 como se muestra en (c). Si el bloque X tiene que ser expulsado de L1, entonces se elimina de L1 solamente como se muestra en (d). Si el bloque Y tiene que ser expulsado de L2, envía una solicitud de invalidación de retorno a L1 y, por lo tanto, el bloque Y es expulsado de L1 como se muestra en (e).

Para que se cumpla la inclusión, deben cumplirse ciertas condiciones. La asociatividad L2 debe ser mayor o igual que la asociatividad L1, independientemente del número de conjuntos. El número de conjuntos L2 debe ser mayor o igual que el número de conjuntos L1, independientemente de la asociatividad L2. Toda la información de referencia de L1 se pasa a L2 para que pueda actualizar sus bits de reemplazo .

Un ejemplo de caché inclusiva es el procesador Intel de cuatro núcleos con 4 cachés L2 de 256 KB y 8 MB (incluidos) de caché L3. [3]

Considere el caso en el que L2 es exclusivo de L1. Suponga que hay una solicitud de lectura del procesador para el bloque X. Si el bloque se encuentra en la caché L1, entonces los datos se leen de la caché L1 y se devuelven al procesador. Si el bloque no se encuentra en la caché L1, pero está presente en la caché L2, entonces el bloque de la caché se mueve de la caché L2 a la caché L1. Si esto hace que un bloque sea expulsado de L1, el bloque expulsado se coloca en L2. Esta es la única forma en que L2 se llena. Aquí, L2 se comporta como una caché víctima . Si el bloque no se encuentra ni en L1 ni en L2, entonces se obtiene de la memoria principal y se coloca solo en L1 y no en L2.

Como se ilustra en la Figura 2, inicialmente se considera que tanto la caché L1 como la caché L2 están vacías (a). Supongamos que el procesador envía una solicitud de lectura X. Será un error tanto en L1 como en L2 y, por lo tanto, el bloque se lleva a L1 desde la memoria principal como se muestra en (b). Ahora, nuevamente el procesador emite una solicitud de lectura Y que es un error tanto en L1 como en L2. Por lo tanto, el bloque Y se coloca en L1 como se muestra en (c). Si el bloque X tiene que ser desalojado de L1, entonces se elimina de L1 y se coloca en L2 como se muestra en (d).

Un ejemplo de caché exclusiva es AMD Opteron con 512 KB (por núcleo) de caché L2, exclusivo de L1. [3]

Consideremos el caso en el que L2 no es inclusivo ni excluyente de L1. Supongamos que hay una solicitud de lectura del procesador para el bloque X. Si el bloque se encuentra en la caché L1, entonces los datos se leen de la caché L1 y se devuelven al procesador. Si el bloque no se encuentra en la caché L1, pero está presente en la caché L2, entonces el bloque de la caché se obtiene de la caché L2 y se coloca en L1. Si esto hace que se expulse un bloque de L1, no hay participación de L2, que es lo mismo que en el caso de la política inclusiva. Si el bloque no se encuentra en L1 y L2, entonces se obtiene de la memoria principal y se coloca tanto en L1 como en L2. Ahora bien, si hay un desalojo de L2, a diferencia de la política inclusiva, no hay invalidación hacia atrás.

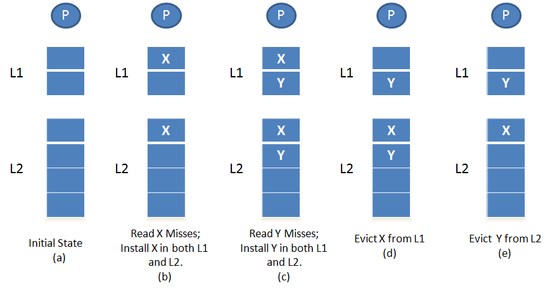

Como se ilustra en la Figura 3, inicialmente se considera que tanto la caché L1 como la caché L2 están vacías (a). Supongamos que el procesador envía una solicitud de lectura X. Será un error tanto en L1 como en L2 y, por lo tanto, el bloque se lleva a L1 y L2 desde la memoria principal como se muestra en (b). Ahora, nuevamente el procesador emite una solicitud de lectura Y que es un error tanto en L1 como en L2. Por lo tanto, el bloque Y se coloca tanto en L1 como en L2 como se muestra en (c). Si el bloque X tiene que ser expulsado de L1, entonces se elimina solo de L1 como se muestra en (d). Si el bloque Y tiene que ser expulsado de L2, se expulsa solo de L2 como se muestra en (e).

Un ejemplo de caché no inclusiva y no exclusiva es AMD Opteron con caché L3 no inclusiva de 6 MB (compartida). [3]

La ventaja de la política inclusiva es que, en sistemas paralelos con caché privada por procesador, si se produce un error de caché, se comprueban otros cachés de pares en busca del bloque. Si el caché de nivel inferior incluye al caché de nivel superior y se produce un error en el caché de nivel inferior, no es necesario realizar una búsqueda en el caché de nivel superior. Esto implica una latencia de error más corta para un caché inclusivo en comparación con el exclusivo y el NINE. [1]

Una desventaja de una política inclusiva es que la capacidad de memoria única de la caché está determinada por la caché de nivel inferior. A diferencia del caso de la caché exclusiva, donde la capacidad de memoria única es la capacidad combinada de todas las cachés en la jerarquía. [4] Si el tamaño de la caché de nivel inferior es pequeño y comparable con el tamaño de la caché de nivel superior, hay más capacidad de caché desperdiciada en cachés inclusivos. Aunque la caché exclusiva tiene más capacidad de memoria única, utiliza más ancho de banda ya que sufre una mayor tasa de llenado de nuevos bloques (igual a la tasa de errores de la caché de nivel superior) en comparación con la caché NINE que se llena con un nuevo bloque solo cuando sufre un error. Por lo tanto, la evaluación del costo en relación con el beneficio debe realizarse al explotar la elección entre cachés inclusivos, exclusivos y NINE.

Inclusión de valores : no es necesario que un bloque tenga los mismos valores de datos cuando se almacena en caché tanto en cachés de nivel superior como de nivel inferior, aunque se mantenga la inclusión. Pero, si los valores de los datos son los mismos, se mantiene la inclusión de valores. [1] Esto depende de la política de escritura en uso, ya que la política de escritura diferida no notifica a la caché de nivel inferior los cambios realizados en el bloque en la caché de nivel superior. Sin embargo, en el caso de la caché de escritura simultánea no existe tal preocupación.