En electrónica digital , una compuerta NAND ( NOT-AND ) es una compuerta lógica que produce una salida que es falsa solo si todas sus entradas son verdaderas; por lo tanto, su salida es complementaria a la de una compuerta AND . Una salida BAJO (0) resulta solo si todas las entradas a la compuerta son ALTAS (1); si alguna entrada es BAJA (0), resulta una salida ALTA (1). Una compuerta NAND se fabrica utilizando transistores y diodos de unión. Por las leyes de De Morgan , la lógica de una compuerta NAND de dos entradas puede expresarse como , lo que hace que una compuerta NAND sea equivalente a inversores seguidos de una compuerta OR .

La compuerta NAND es importante porque cualquier función booleana se puede implementar mediante una combinación de compuertas NAND. Esta propiedad se denomina " completitud funcional ". Comparte esta propiedad con la compuerta NOR . Los sistemas digitales que emplean ciertos circuitos lógicos aprovechan la completitud funcional de NAND.

Las puertas NAND con dos o más entradas están disponibles como circuitos integrados en lógica transistor-transistor , CMOS y otras familias lógicas .

Existen tres símbolos para las puertas NAND: el símbolo MIL/ ANSI , el símbolo IEC y el símbolo DIN obsoleto que a veces se encuentra en esquemas antiguos. El símbolo ANSI para la puerta NAND es una puerta AND estándar con una burbuja de inversión conectada.

La función NAND( a 1 , a 2 , ..., a n ) es lógicamente equivalente a NOT( a 1 AND a 2 AND ... AND a n ).

Una forma de expresar A NAND B es , donde el símbolo significa AND y la barra significa la negación de la expresión debajo de él: en esencia, simplemente .

Las implementaciones básicas se pueden entender a partir de la imagen de la izquierda a continuación: si cualquiera de los interruptores S1 o S2 está abierto, la resistencia pull-up R establecerá la señal de salida Q en 1 (alta). Si S1 y S2 están cerrados, la resistencia pull-up será anulada por los interruptores y la salida será 0 (baja).

En la realización de lógica NMOS de agotamiento-carga en el medio a continuación, los interruptores son los transistores T2 y T3, y el transistor T1 cumple la función de resistencia pull-up.

En la realización CMOS de la derecha abajo, los interruptores son los transistores T3 y T4, y la resistencia pull-up está formada por los transistores T1 y T2, que forman el complemento de los transistores T3 y T4.

Las puertas NAND son puertas lógicas básicas y, como tales, se reconocen en los circuitos integrados TTL y CMOS .

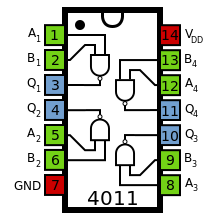

El CI CMOS estándar de la serie 4000 es el 4011, que incluye cuatro puertas NAND independientes de dos entradas. Estos dispositivos están disponibles en muchos fabricantes de semiconductores. Suelen estar disponibles en formatos SOIC y DIL de orificio pasante . Las hojas de datos están disponibles en la mayoría de las bases de datos de hojas de datos .

Las puertas NAND estándar de dos, tres, cuatro y ocho entradas están disponibles:

La compuerta NAND tiene la propiedad de completitud funcional , que comparte con la compuerta NOR . Es decir, cualquier otra función lógica (AND, OR, etc.) se puede implementar utilizando únicamente compuertas NAND. [1] Se puede crear un procesador completo utilizando únicamente compuertas NAND. En los circuitos integrados TTL que utilizan transistores de múltiples emisores , también se requieren menos transistores que una compuerta NOR.

Como las puertas NOR también son funcionalmente completas, si no hay puertas NAND específicas disponibles, se puede hacer una a partir de puertas NOR utilizando lógica NOR . [1]